PUBLICATION NUMBER: 6918-0100A OCTOBER 1983

# **RF-3352** FSK TERMINAL

INSTRUCTION MANUAL

#### LIMITED ONE YEAR WARRANTY HARRIS CORPORATION (RF COMMUNICATIONS GROUP)

FROM HARRIS TO YOU – This warranty is extended to the original buyer and applies to all Harris Corporation, RF Communications Group equipment purchased and employed for the service normally intended, except those products specifically excluded.

WHAT WE WILL DO - If your Harris Corporation, RF Communications Group equipment purchased from us for use outside the United States fails in normal use because of a defect in workmanship or materials within one year from the date of shipment, we will repair or replace (at our option) the equipment or part without charge to you, at our factory. If the product was purchased for use in the United States, we will repair or replace (at our option) the equipment or part without charge to you at our Authorized Repair Center or factory.

WHAT YOU MUST DO - You must notify us promptly of a defect within one year from date of shipment. Assuming that Harris concurs that the complaint is valid, and is unable to correct the problem without having the equipment shipped to Harris:

- Customers with equipment purchased for use outside the United States will be supplied with information for the return of the defective equipment or part to our factory in Rochester, NY, U.S.A., for repair or replacement. You must prepay all transportation, insurance, duty and customs charges. We will pay for return to you of the repaired/replaced equipment or part, C.I.F. destination; you must pay any duty, taxes or customs charges.

- Customers with equipment purchased for use in the United States must obtain a Return Authorization Number, properly pack, insure, prepay the shipping charges and ship the defective equipment or part to our factory or to the Authorized Warranty Repair Center indicated by us.

Harris Corporation RF Communications Group Customer Service 1680 University Avenue Rochester, NY 14610, U.S.A. Telephone: (716) 244-5830 Telex: 240313 Cable: RFCOM

Harris will repair or replace the defective equipment or part and pay for its return to you, provided the repair or replacement is due to a cause covered by this warranty.

WHAT IS NOT COVERED - We regret that we cannot be responsible for:

- Defects or failures caused by buyer or user abuse or misuse.

- Defects or failures caused by unauthorized attempts to repair or alter the equipment in any way.

- Consequential damages incurred by a buyer or user from any cause whatsoever, including, but not limited to transportation, non-Harris repair or service costs, downtime costs, costs for substituting equipment or loss of anticipated profits or revenue.

- The performance of the equipment when used in combination with equipment not purchased from Harris.

- HARRIS MAKES NO OTHER WARRANTIES BEYOND THE EXPRESS WARRANTY AS CONTAINED HEREIN. ALL EXPRESS OR IMPLIED WARRANTIES OF FITNESS FOR A PARTICULAR PURPOSE OR MERCHANTABILITY ARE EXCLUDED.

SERVICE WARRANTY – Any repair service performed by Harris under this limited warranty is warranted to be free from defects in material or workmanship for sixty days from date of repair. All terms and exclusions of this limited warranty apply to the service warranty.

IMPORTANT – Customers who purchased equipment for use in the United States must obtain a Return Authorization Number before shipping the defective equipment to us. Failure to obtain a Return Authorization Number before shipment may result in a delay in the repair/replacement and return of your equipment.

IF YOU HAVE ANY QUESTIONS – Concerning this warranty or equipment sales or services, please contact our Customer Service Department.

#### SPARE PARTS KITS AND MOUNTING OPTIONS

Listed below are the spare parts kits and mounting options available from Harris Corporation for use with the equipment described in this manual. To order any of these items, or to obtain more information concerning them, write to:

HARRIS CORPORATION RF Communications Division Rochester, New York 14610 U.S.A.

#### ATTN: MARKETING DEPARTMENT

or call: (716) 244-5830, and ask for Marketing Department

When placing an order, please specify the model number.

We will be happy to answer any questions you may have regarding these or any other items we manufacture. We also welcome your evaluation of our equipment and suggestions for other accessory items or spare parts.

| Kit Model and<br>Part Number         | Name                                                                                                | Kit Description/Content                                                                                                                                                                                                                                                    | Model<br>Designation                | Part Number                                                        | Option Contents/Nomenclature                                                                   |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| RF-3352 (RSK).<br>Part No. 1001-0280 | RF-3352 Running<br>Spares Kit                                                                       | This kit comprises the field-replaceable 1/8<br>Ampere fuses that may be consumed during<br>equipment installation and setup.                                                                                                                                              | RF-3352-1                           | 6918-0011<br>6918-0010<br>213-0005-054<br>6918-1020                | FSK Terminal, Slide Mounted<br>RF-3352 FSK Terminal<br>Chassis Slide<br>Slide Mounting Bracket |

| RF-3352 (OSK)<br>Part No. 1001-0281  | RF-3352 Operational<br>Spares Kit                                                                   | This kit contains those items that will allow<br>the unit to be repaired at the highest<br>practical level of assembly (thus minimizing<br>"down" or "off the air" time). The kit<br>includes a complete set of assemblies and<br>subassemblies, and piece parts for items | RF-3352-2                           | 6918-0012<br>6918-0010<br>Z13-0005-054<br>6918-0120                | FSK Terminal, Stack Mounted<br>RF-3352 FSK Terminal<br>Chassis Slide<br>Stacking Bracket       |

|                                      | impractical to repair by assembly or sub-<br>assembly replacement (such as switches and<br>meters). | RF-3352-3                                                                                                                                                                                                                                                                  | 6918-0013<br>6918-0010<br>6918-1005 | FSK Terminal, Desk Top<br>RF-3352 FSK Terminal<br>Desk Top Cabinet |                                                                                                |

#### Spares Kits for the RF-3352 FSK Terminal

Mounting Options Available for the RF-3352 FSK Terminal

# TABLE OF CONTENTS

Page

| Paragraph |  |

|-----------|--|

|           |  |

# SECTION 1 INTRODUCTION

| 1.1 | Manual Scope and General Description 1-1  |

|-----|-------------------------------------------|

| 1.2 | Technical Characteristics                 |

| 1.3 | Spare Parts Kits and Mounting Options 1-1 |

# SECTION 2 INSTALLATION

| 2.1   | Introduction                                              | . 2-1 |

|-------|-----------------------------------------------------------|-------|

| 2.2   | Unpacking and Inspection Instructions                     | . 2-1 |

| 2.3   | Mechanical Installation/Replacement of Damaged Assemblies | . 2-1 |

| 2.4   | RF-3352 FSK Terminal Electrical Interconnection           |       |

| 2.4.1 | Primary Power Selection                                   | . 2-5 |

| 2.4.2 | Emergency Shutdown Instructions                           | . 2-5 |

| 2.5   | Initial Position of Controls and Switches                 | . 2-6 |

| 2.6   | Loop Current Adjustments                                  | . 2-6 |

| 2.7   | Operational Adjustments                                   | . 2-6 |

| 2.8   | Repacking and Shipping Instructions                       | . 2-7 |

#### SECTION 3 OPERATION

| 3.1 | Introduction                                                                           | 3-1 |

|-----|----------------------------------------------------------------------------------------|-----|

| 3.2 | Front and Rear Panel Connector, Control, Indicator and Switch Locations and Functions. | 3-1 |

| 3.3 | Operation                                                                              |     |

| 3.4 | Determining the Unknown Center and Shift Frequencies                                   | 3-1 |

| 3.5 | Determining the Unknown Center Frequency When the Shift Frequency Is Known             | 3-6 |

| 3.6 | Loop Current Adjustment                                                                | 3-6 |

| 3.7 | Emergency Shutdown Instructions                                                        | 3-7 |

#### SECTION 4 THEORY OF OPERATION

| 4.1       | Introduction                                                                       | 4-1 |

|-----------|------------------------------------------------------------------------------------|-----|

| 4.2       | Overall Terminal and Subassembly Functional Descriptions                           | 4-1 |

| 4.3       | Signal Path Routing for Various Operational States                                 | 4-2 |

| 4.4       | Major Assembly Operational Analyses                                                | 4-2 |

| 4.4.1     | Modulator Pwb Assembly A1 Operation Description                                    | 4-2 |

| 4.4.1.1   | Overall Description.                                                               | 4-2 |

| 4.4.1.2   | Detailed Circuit Description                                                       | 4-4 |

| 4.4.1.2.1 | Phase-locked Loop Operation                                                        | 4-4 |

| 4.4.1.2.2 | Divide-by-N Counter Operation                                                      | 4-4 |

| 4.4.1.2.3 | Binary Number Application to Counter/Latch Operation                               | 4-5 |

| 4.4.1.2.4 | Synthesizer Output Routing, Divide-by-10 Counter, Divide-by-20 Johnson Counter and |     |

|           | Audio Conditioning                                                                 | 4-5 |

| 4.4.1.2.5 | Traffic Detector Circuitry                                                         | 4-6 |

| 4.4.1.2.6 | Combinational Logic Circuitry                                                      | 4-6 |

| 4.4.1.2.7 | Clear-to-Send Delay Function                                                       |     |

| 4.4.1.2.8 | Keyline Closure Function                                                           | 4-6 |

iv

# TABLE OF CONTENTS (Cont.)

# Paragraph

# Page

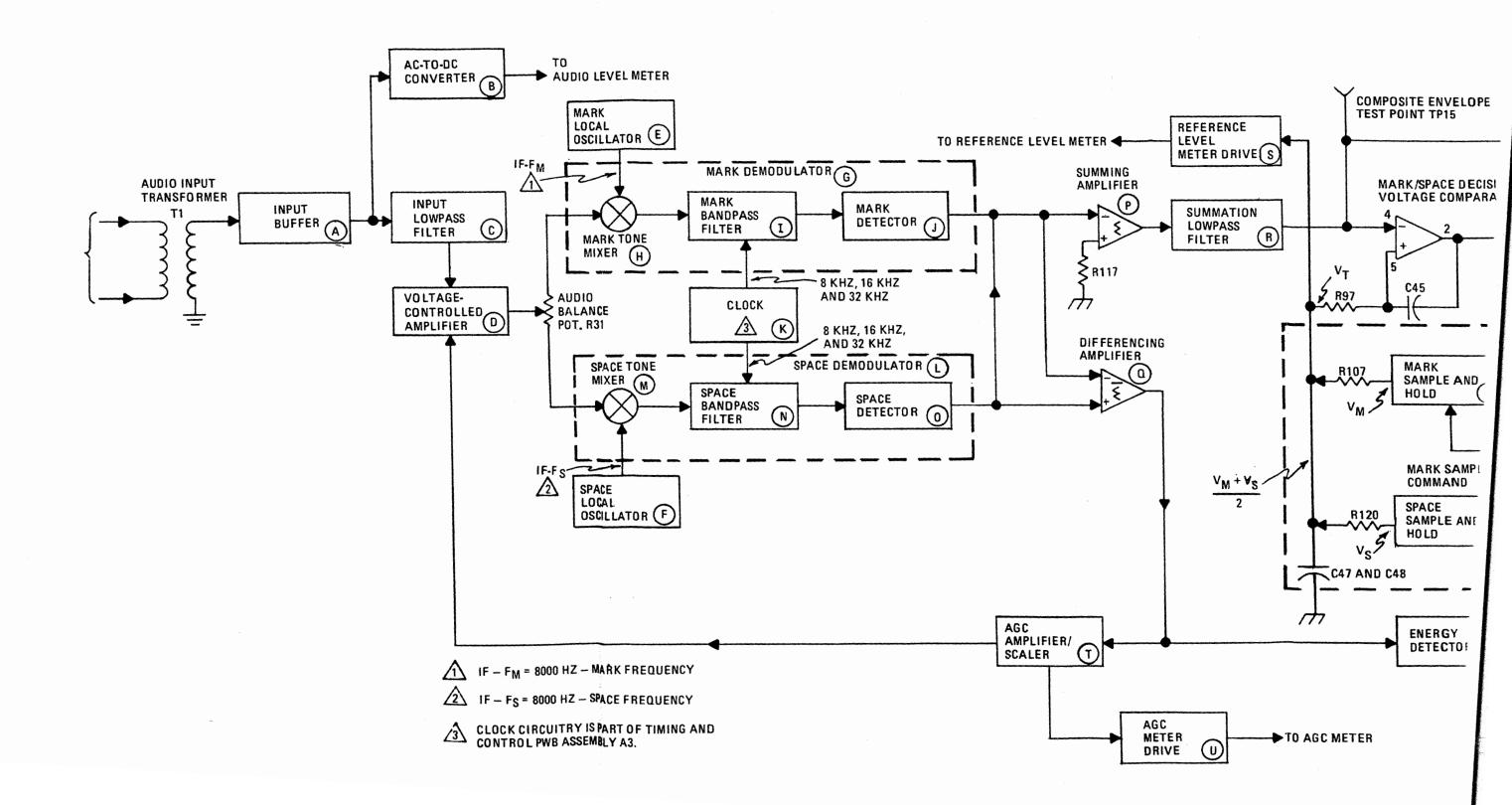

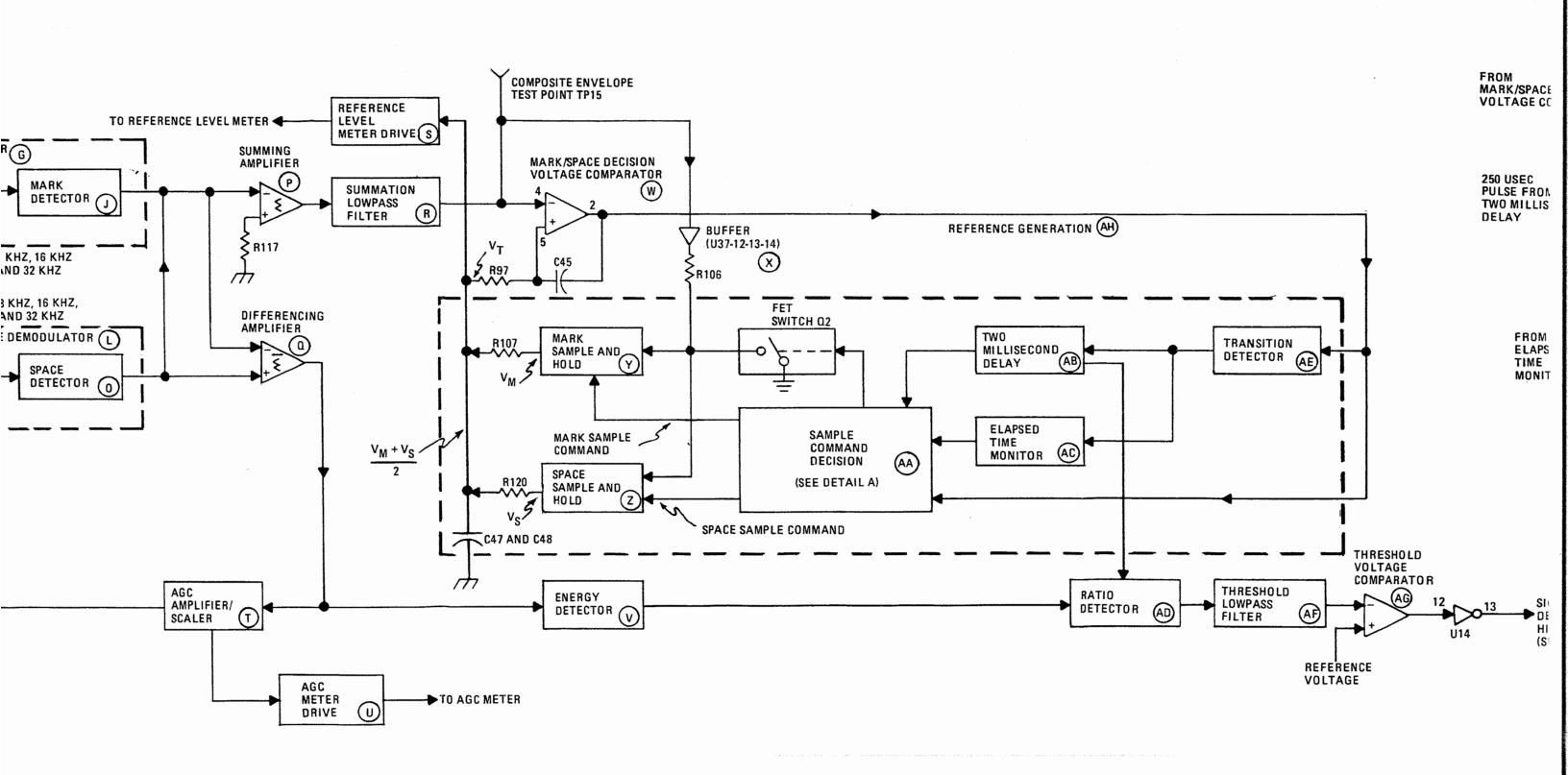

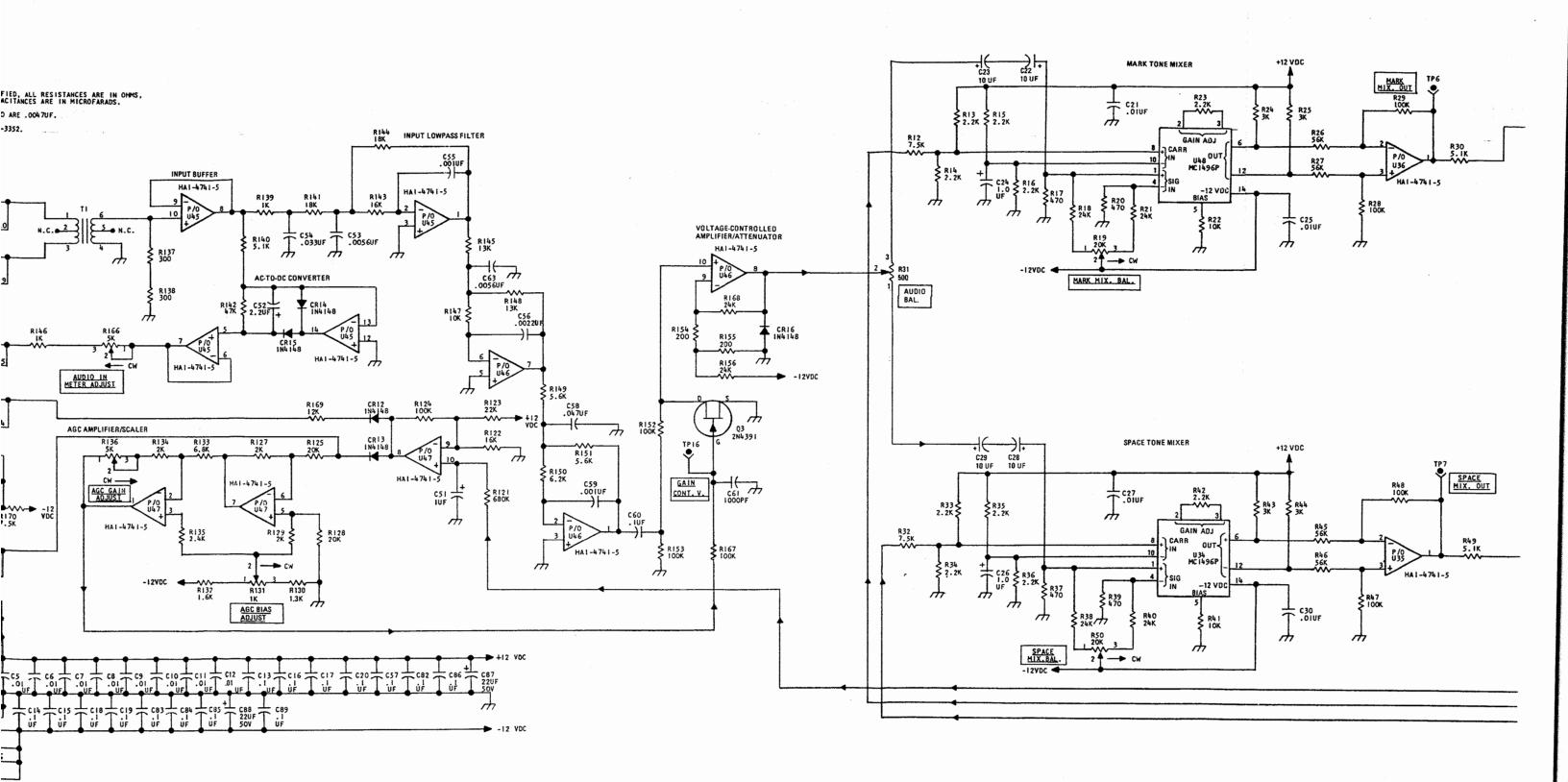

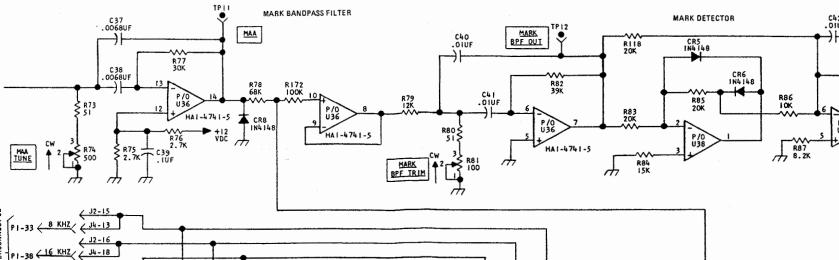

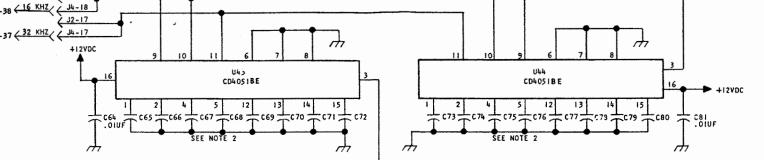

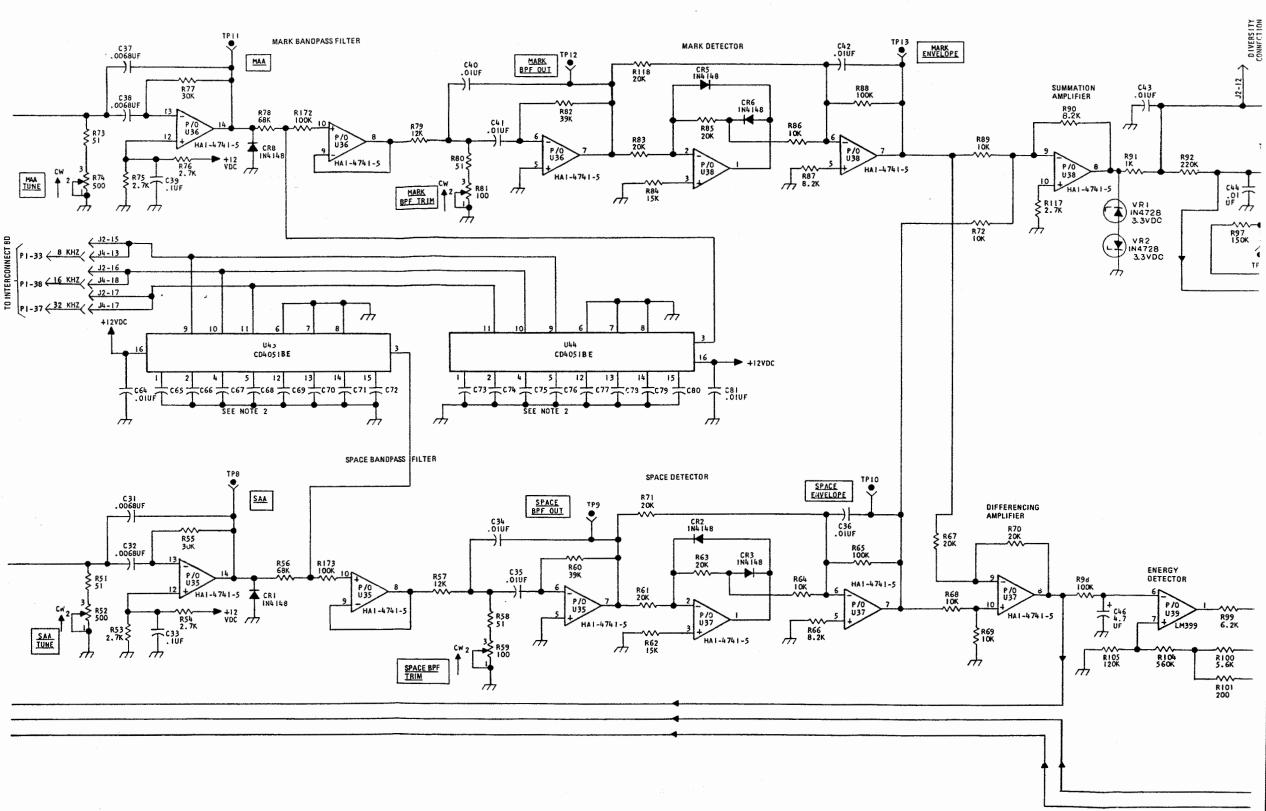

| 4.4.2     | Demodulator Pwb Assembly A2 Operation Description                                                     |

|-----------|-------------------------------------------------------------------------------------------------------|

| 4.4.2.1   | Input Circuitry Operation 4-8                                                                         |

| 4.4.2.2   | Voltage-Controlled Amplifier/Attenuator, Local Oscillator, and Demodulator Circuitry                  |

| 4.4.2.3   | Operation                                                                                             |

| 4.4.2.3   | Mark/Space Decision Voltage Comparator Circuitry Operation                                            |

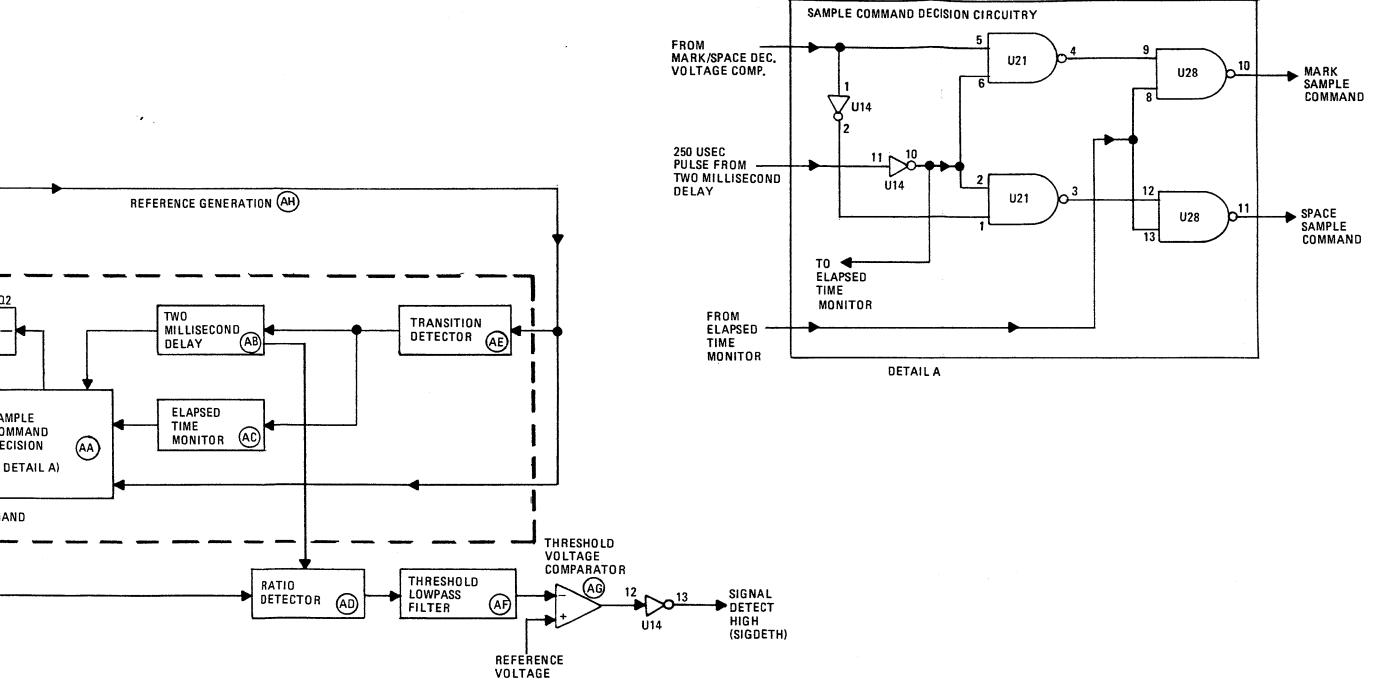

| 4.4.2.4   | Reference Generator Circuitry Operation                                                               |

|           |                                                                                                       |

| 4.4.2.6   | Energy Detector, Radio Detector, and Carrier Detect Voltage Comparator Circuitry<br>Operation         |

| 4.4.2.7   | Demodulator Circuitry Detailed Theoretical Analysis                                                   |

| 4.4.2.8   | Detailed Operation of Differencing Amplifier U37-9-10-8 and the AGC Amplifier/Scaler<br>Circuitry     |

| 4.4.2.8.1 | AGC Amplifier/Scaler Circuitry                                                                        |

| 4.4.2.9   | Detailed Operation of the Transition Detector                                                         |

| 4.4.2.9   | Detailed Operation of the Transition Detector                                                         |

| 4.4.2.10  |                                                                                                       |

|           | Detailed Operation of the Ratio Detector                                                              |

| 4.4.2.12  | Detailed Operation of the Threshold Lowpass, Filter and Threshold Voltage Comparator 4-20             |

| 4.4.2.13  | Data Line Routing-Output of Mark/Space Decision Voltage Comparator U39-4-5-24-20                      |

| 4.4.2.14  | Detailed Operation of the Timed Mark Hold Circuit                                                     |

| 4.4.2.15  | Untimed Mark Hold Circuits Description                                                                |

| 4.4.2.16  | Auto Start Relay Circuit Description                                                                  |

| 4.4.2.17  | Signal Processing and Operation of the Threshold Generator, Including the Sample and<br>Hold Circuits |

| 4.4.2.18  | Mark and Space Local Oscillator Circuitry                                                             |

| 4.4.3     | Timing and Control Pwb Assembly A3 and Frequency Control Board Assembly A7 Opera-                     |

|           | tion Description                                                                                      |

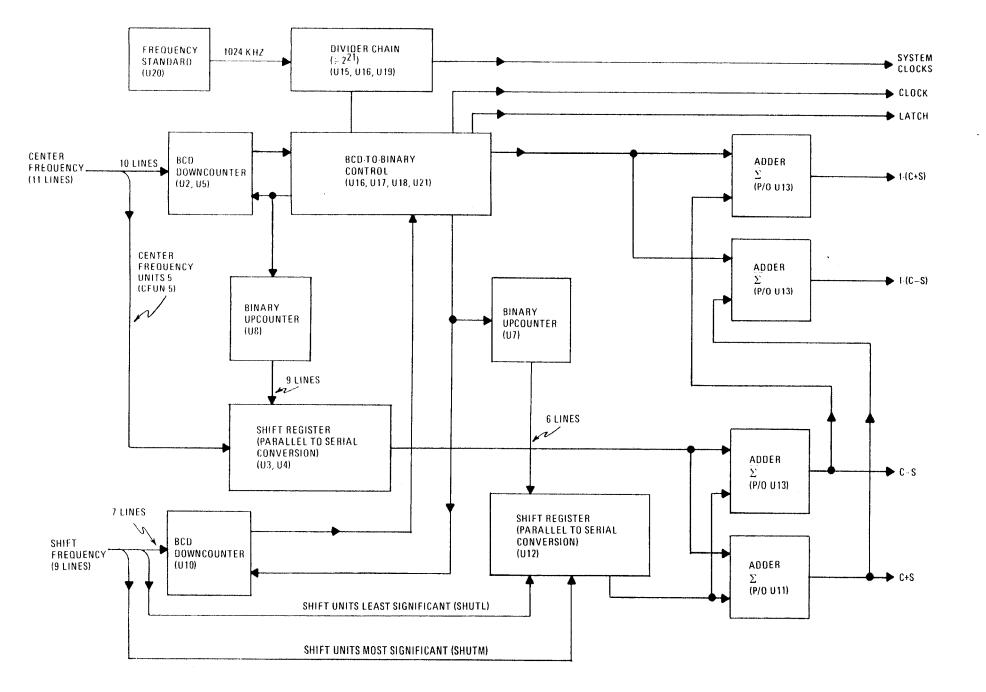

| 4.4.3.1   | Frequency Processing - General Description                                                            |

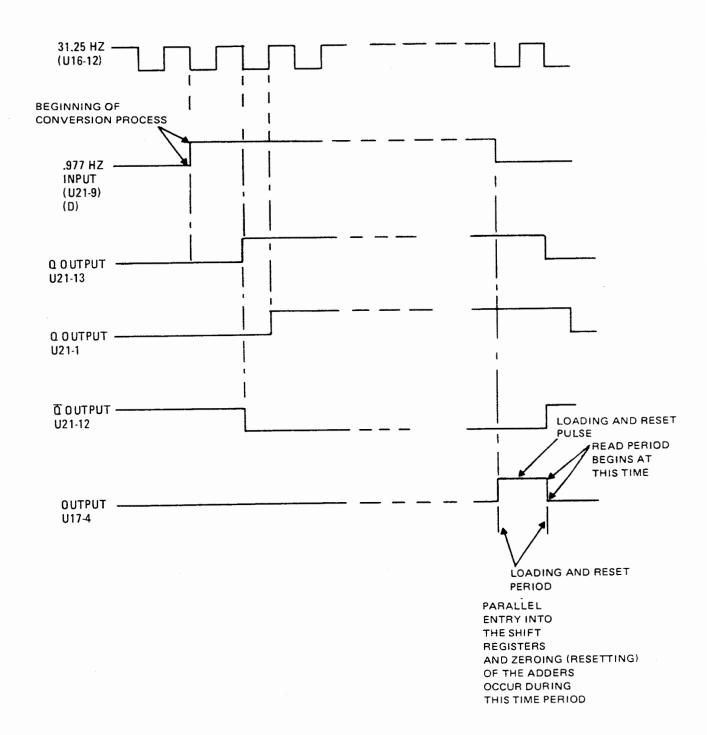

| 4.4.3.2   | Conversion Process Description                                                                        |

| 4.4.3.3   | Counter Initialization                                                                                |

| 4.4.3.4   | Counter Clocking                                                                                      |

| 4.4.3.5   | Counter Time Description                                                                              |

| 4.4.3.6   | Loading and Reset Period                                                                              |

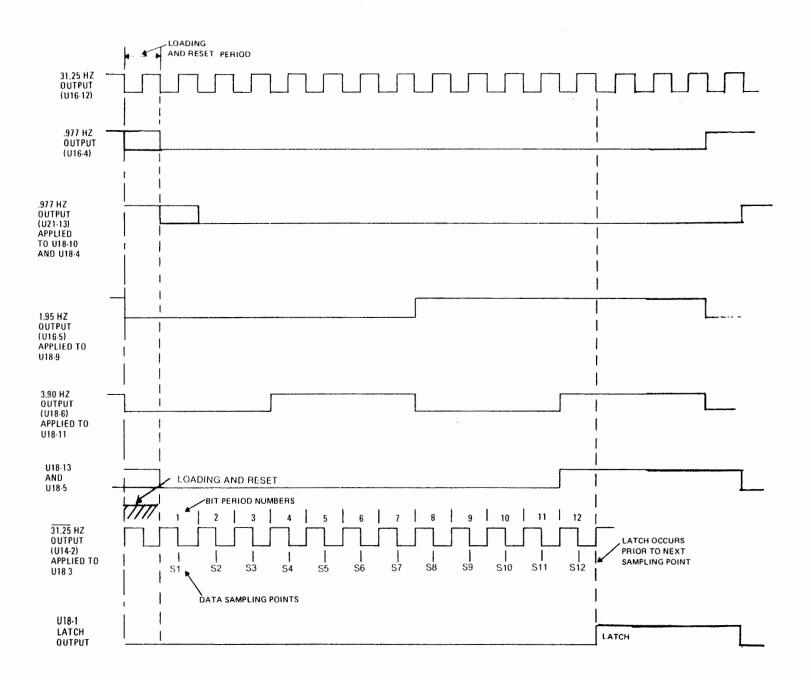

| 4.4.3.7   | Read Period Timing                                                                                    |

| 4.4.3.8   | Read Period Data Interpretation                                                                       |

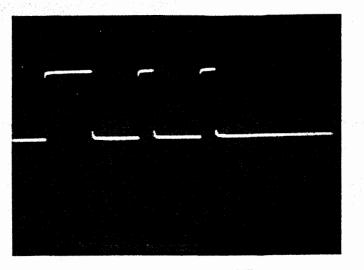

| 4.4.3.9   | Description of Latch Timing                                                                           |

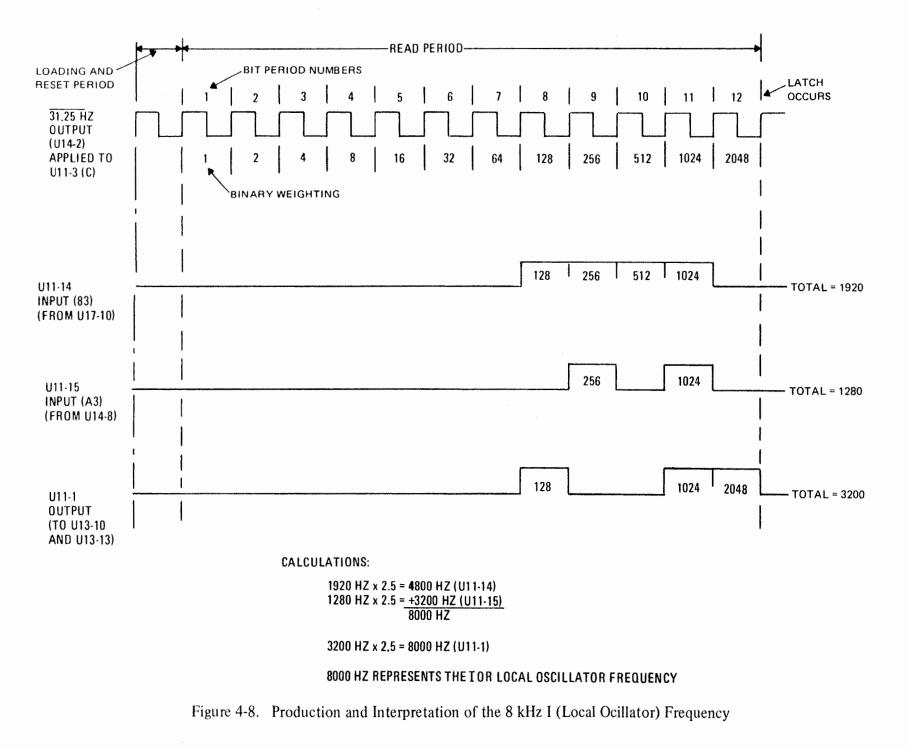

| 4.4.3.10  | Production of the I, C + S, and C-S Outputs                                                           |

|           |                                                                                                       |

| 4.4.3.11  | Production of Other Frequency Outputs                                                                 |

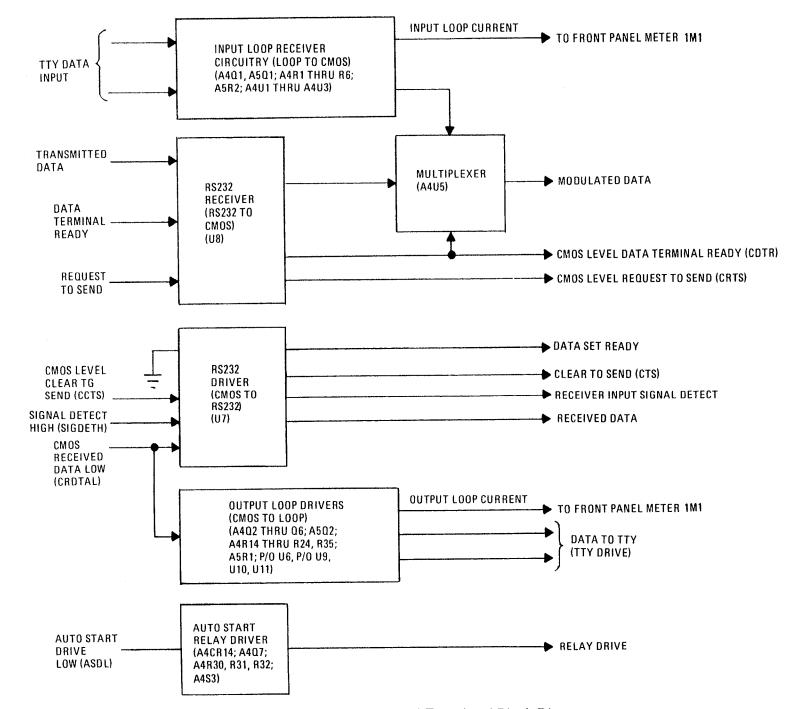

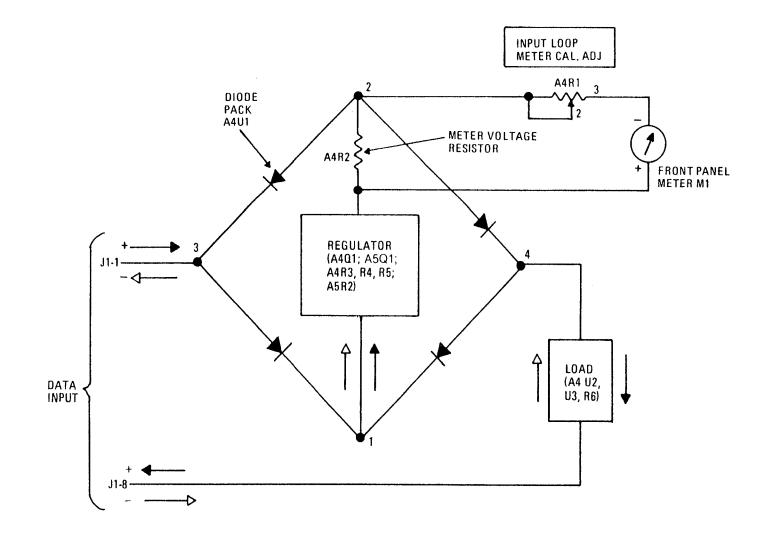

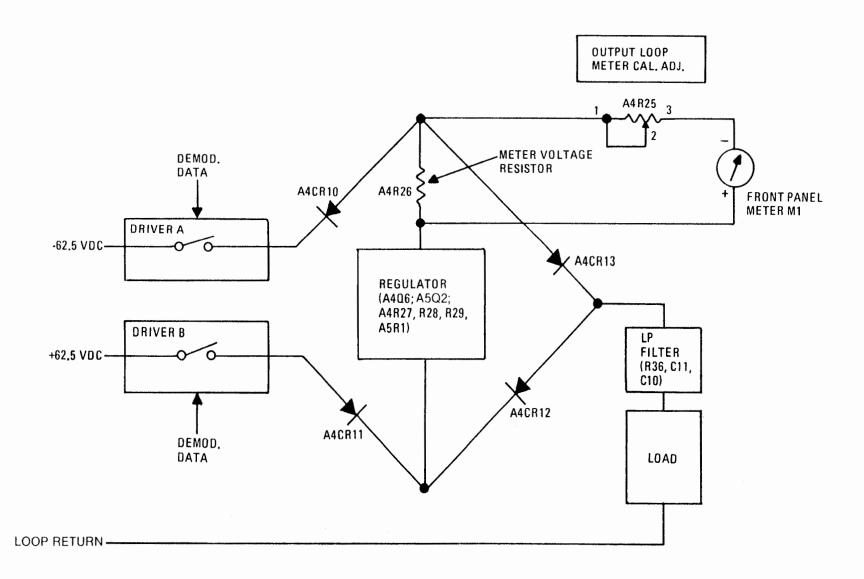

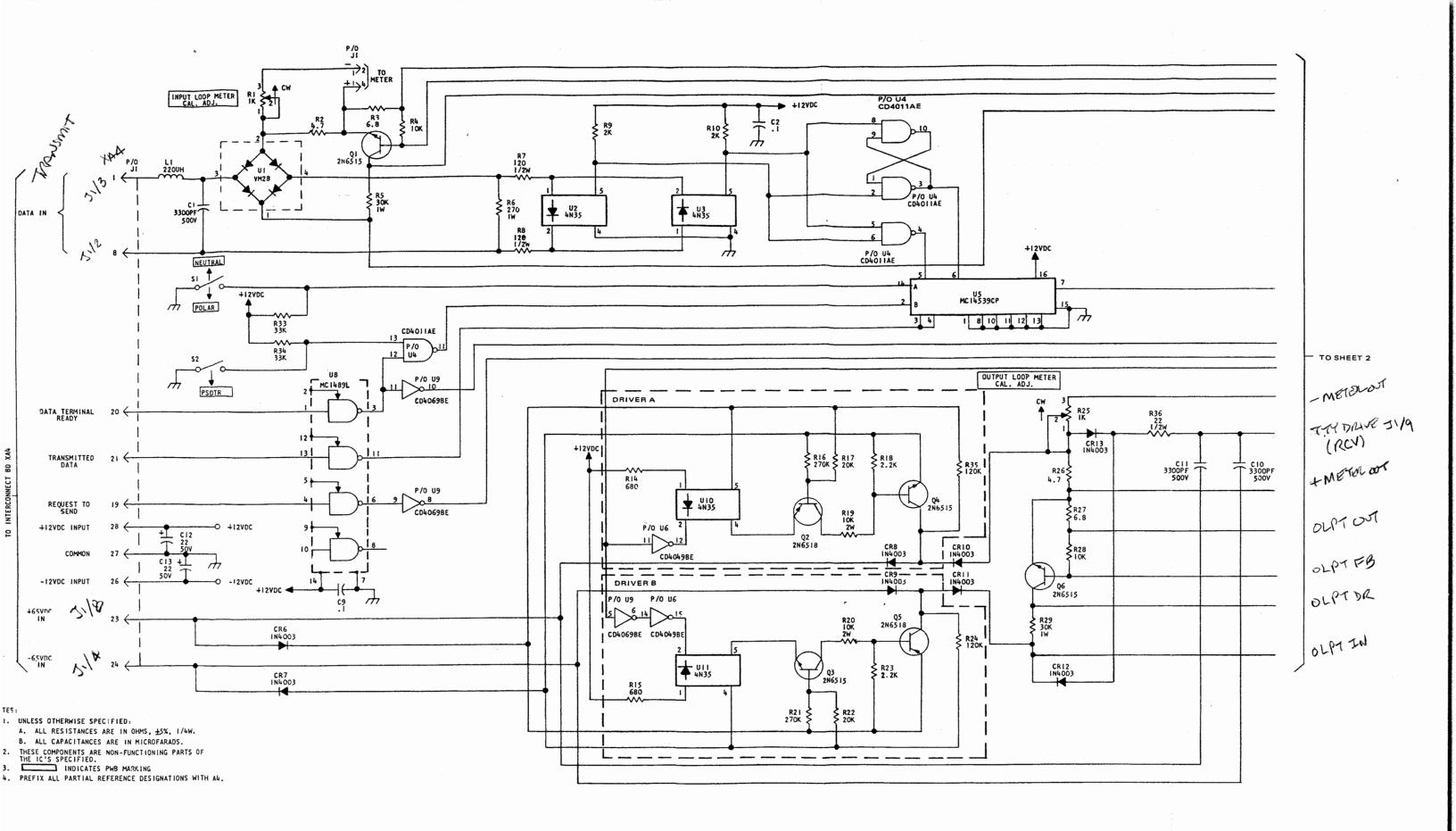

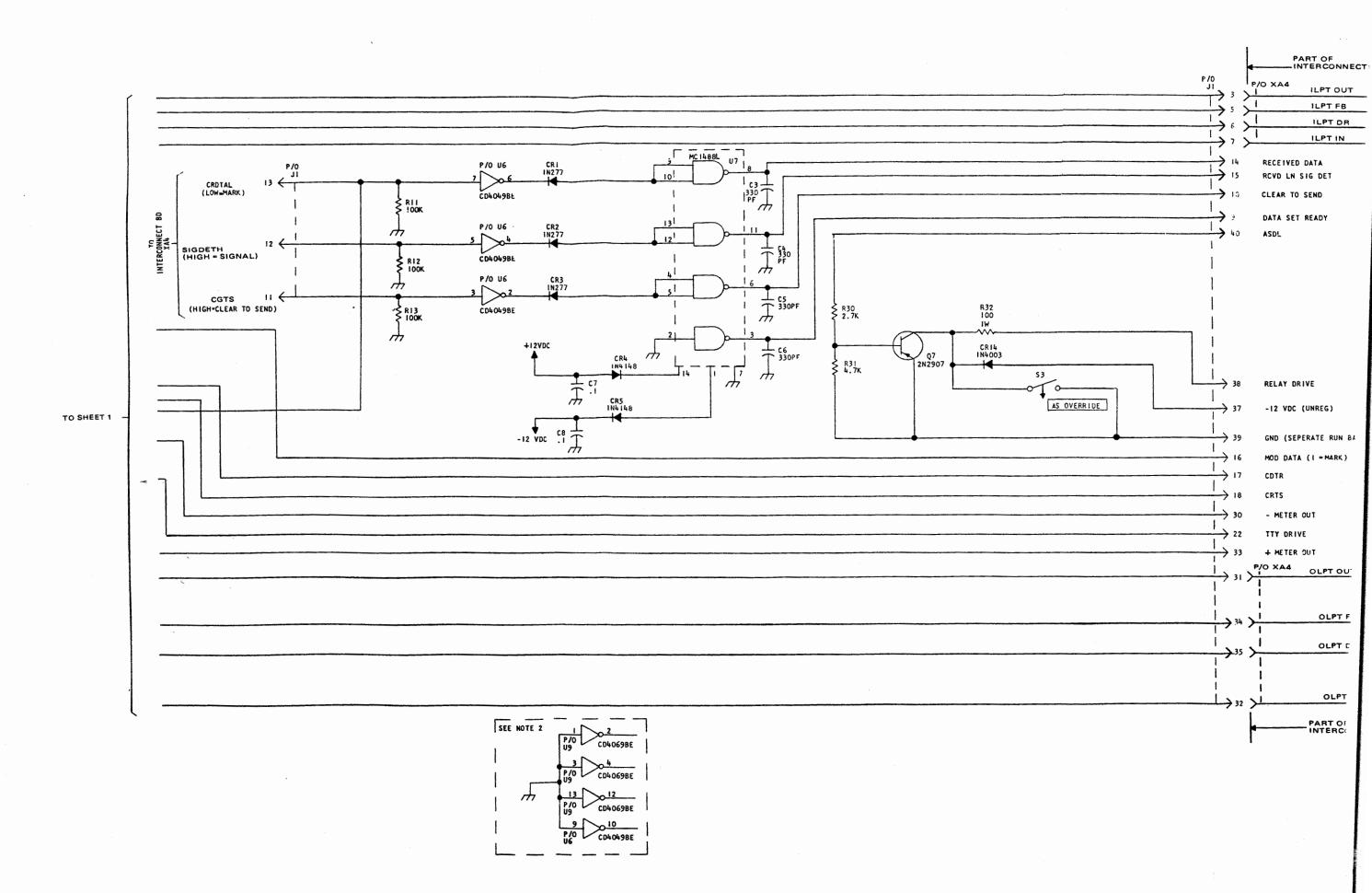

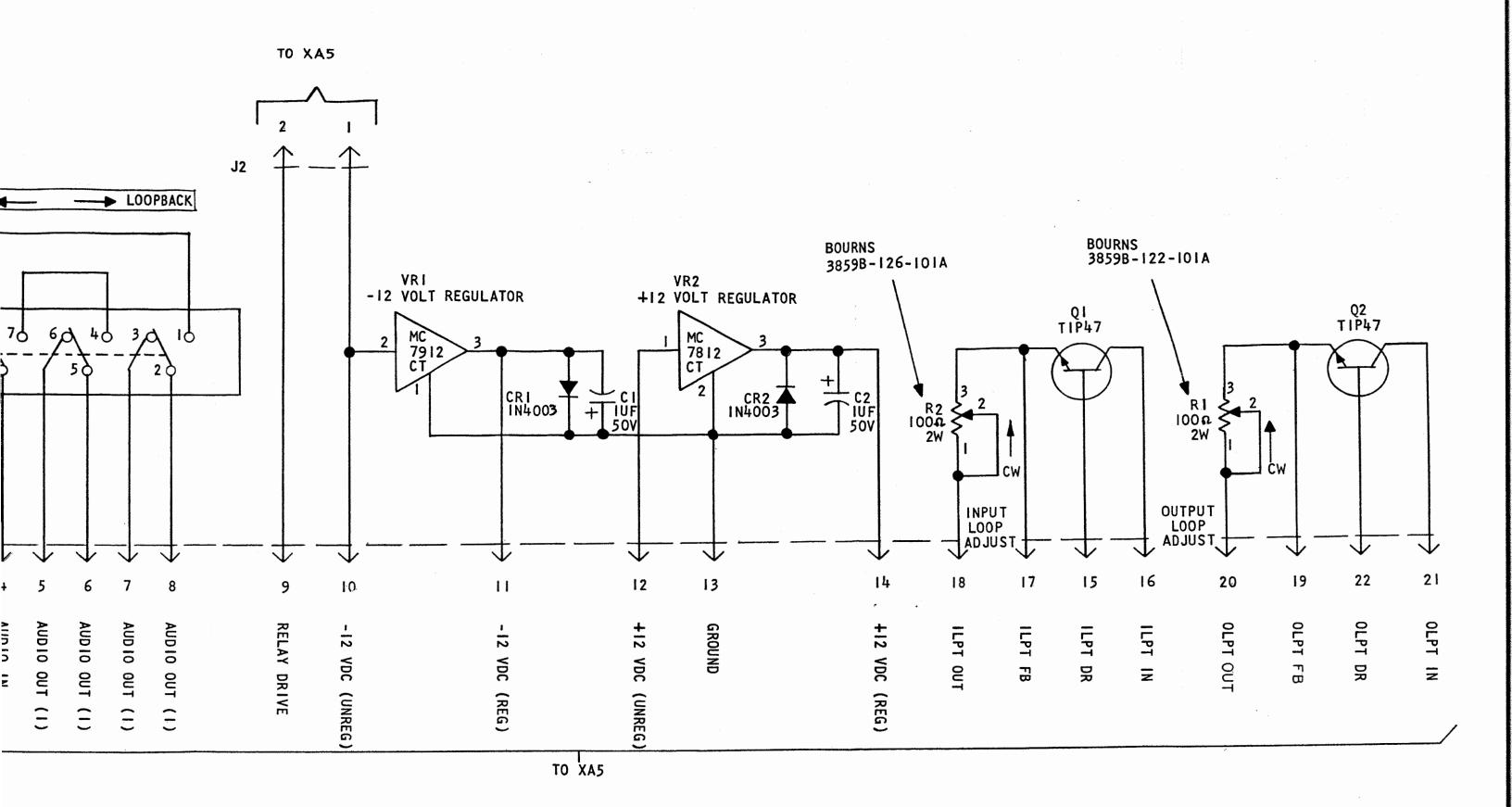

| 4.4.4     | Interface Pwb Assembly A4 Operation Description                                                       |

| 4.4.4.1   | Input Loop Circuitry Description                                                                      |

| 4.4.4.2   |                                                                                                       |

| 4.4.4.3   | Operation in Neutral Mode                                                                             |

| 4.4.4.4   | Operation in Polar Mode                                                                               |

| 4.4.4.5   | Selection of Neutral or Polar Modes - Operation of Multiplexer U5                                     |

| 4.4.4.6   | RS-232 Receive Protocol Description                                                                   |

| 4.4.4.7   | Output Loop Driver Functional Analysis                                                                |

| 4.4.4.8   | Output Loop Current Regulator Operation                                                               |

| 4.4.4.9   | Equipment Interconnection - Theoretical Aspects                                                       |

| 4.4.4.10  | Conversion of CMOS Internal Outputs to RS-232 Outputs                                                 |

| 4.4.4.11  | Auto Start Relay Components                                                                           |

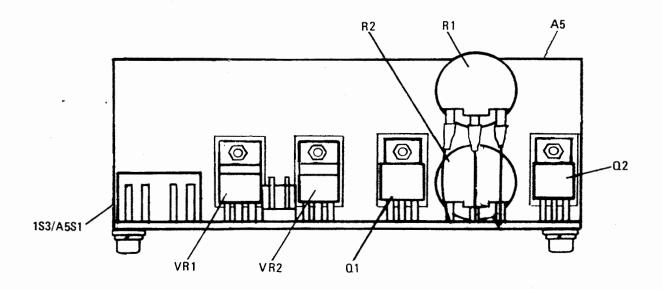

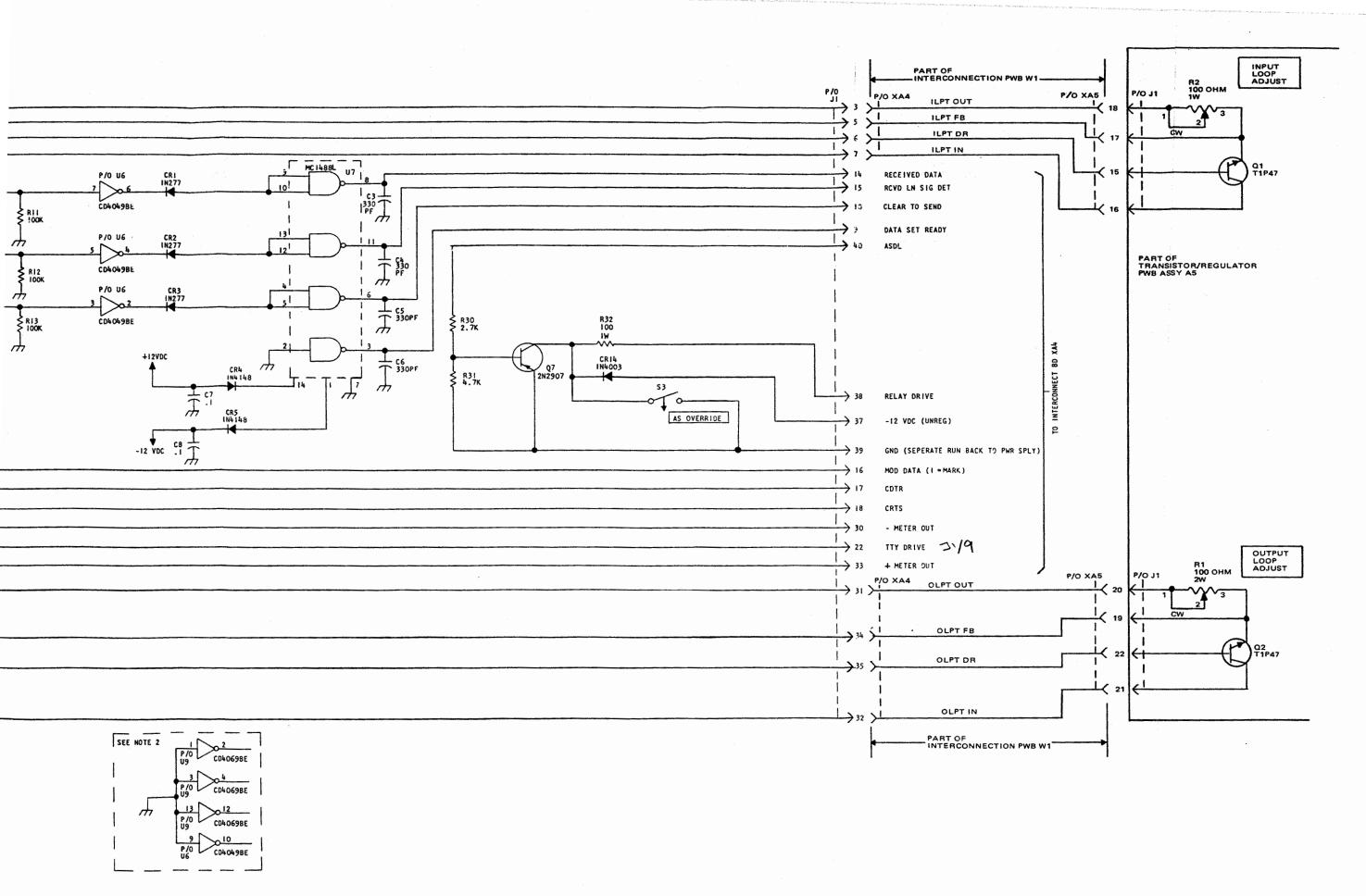

| 4.4.5     | Transistor/Regulator Pwb Assembly A5 Description                                                      |

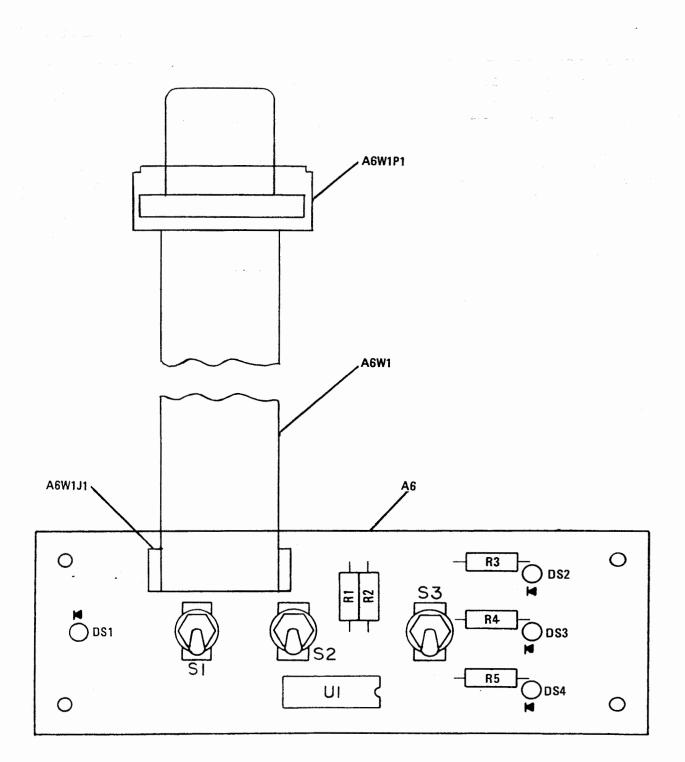

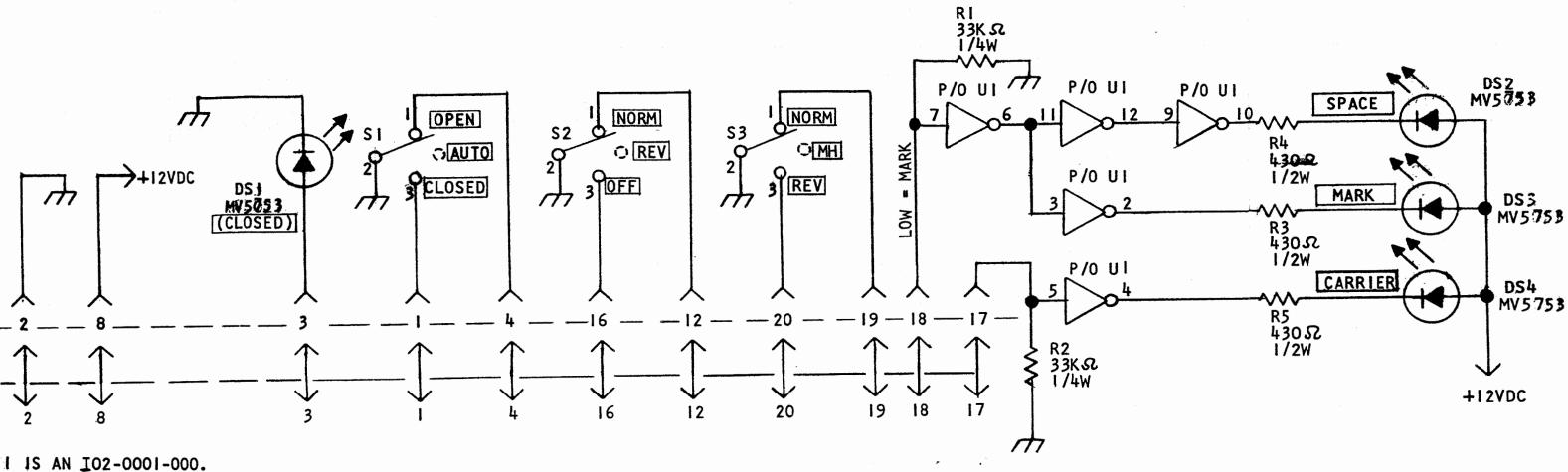

| 4.4.6     | Control and Indicator Pwb Assembly A6 Description                                                     |

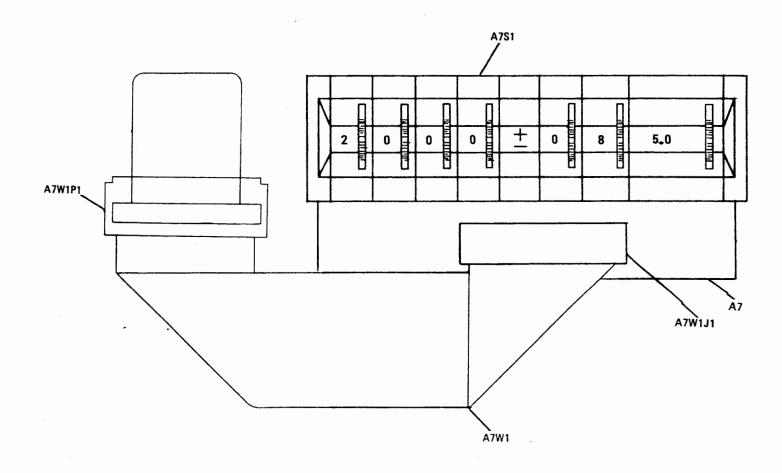

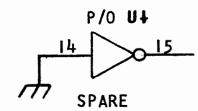

| 4.4.7     | Frequency Control Board Assembly A7 Description                                                       |

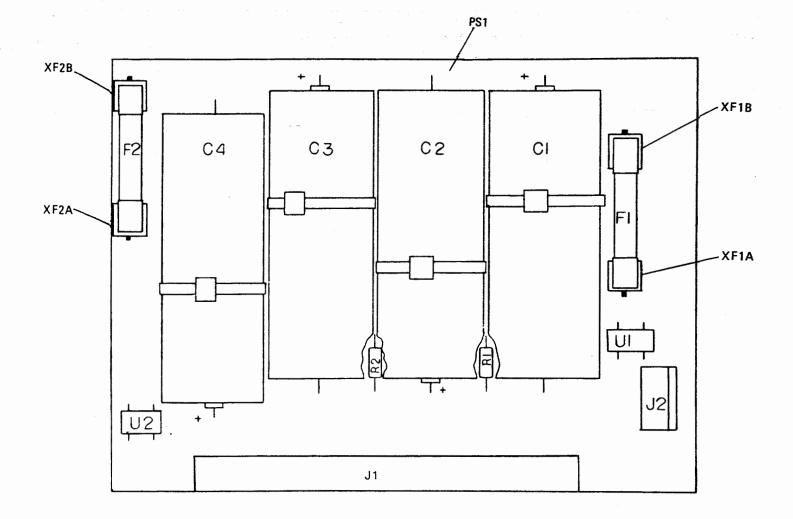

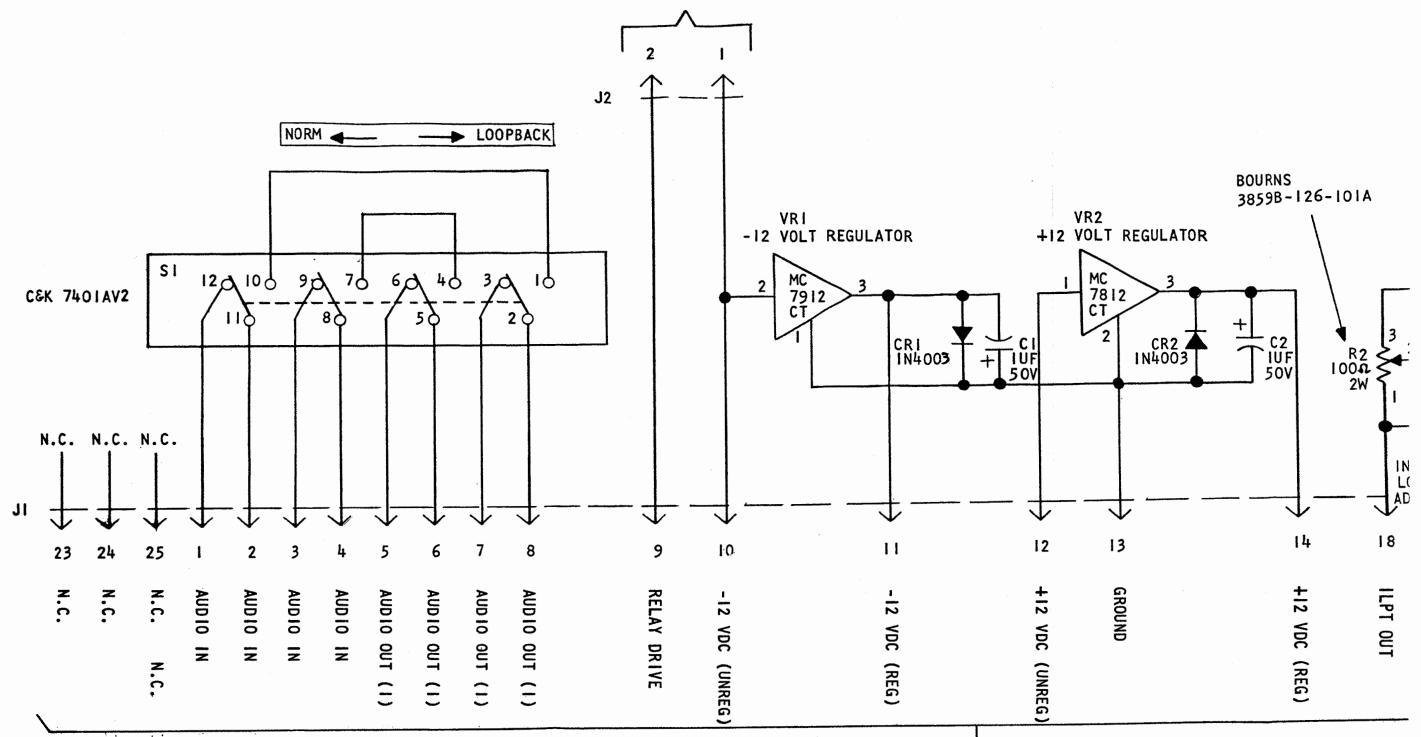

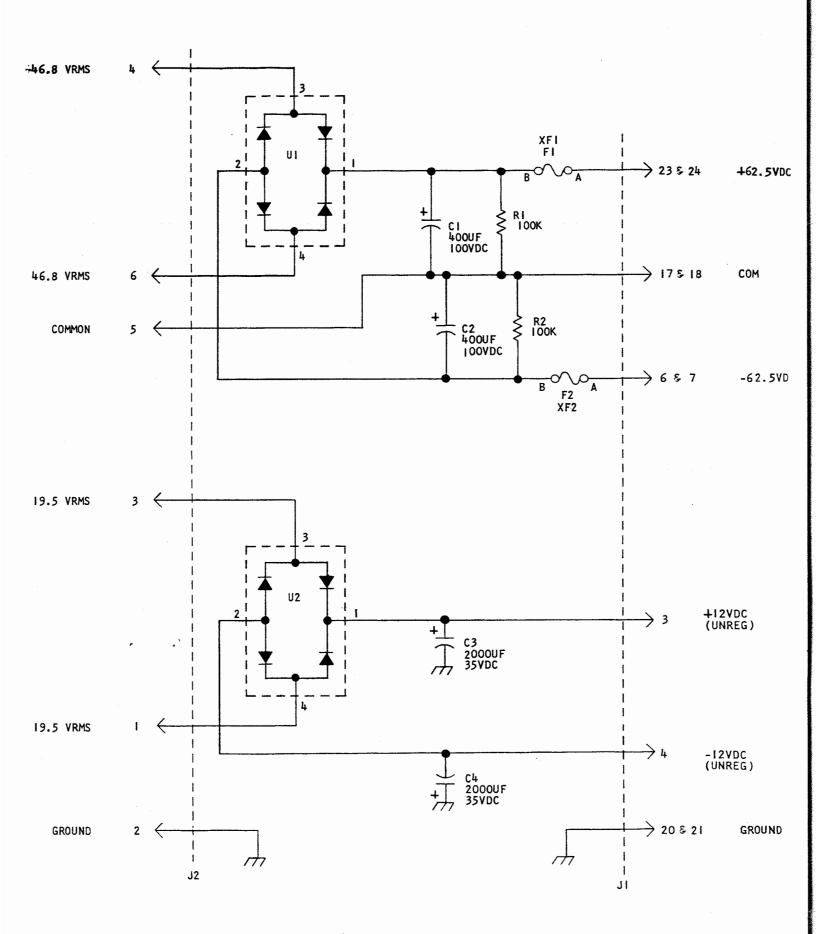

| 4.4.8     | Power Supply Pwb Assembly PS1 Description                                                             |

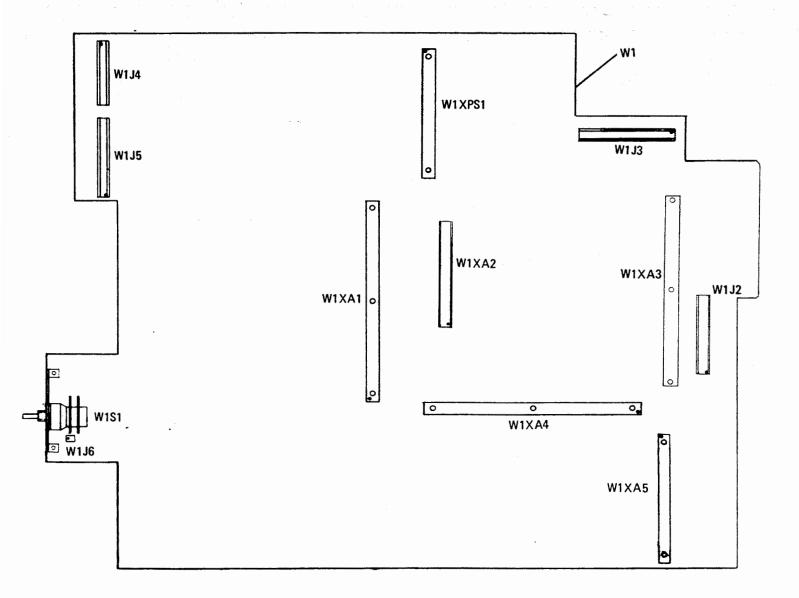

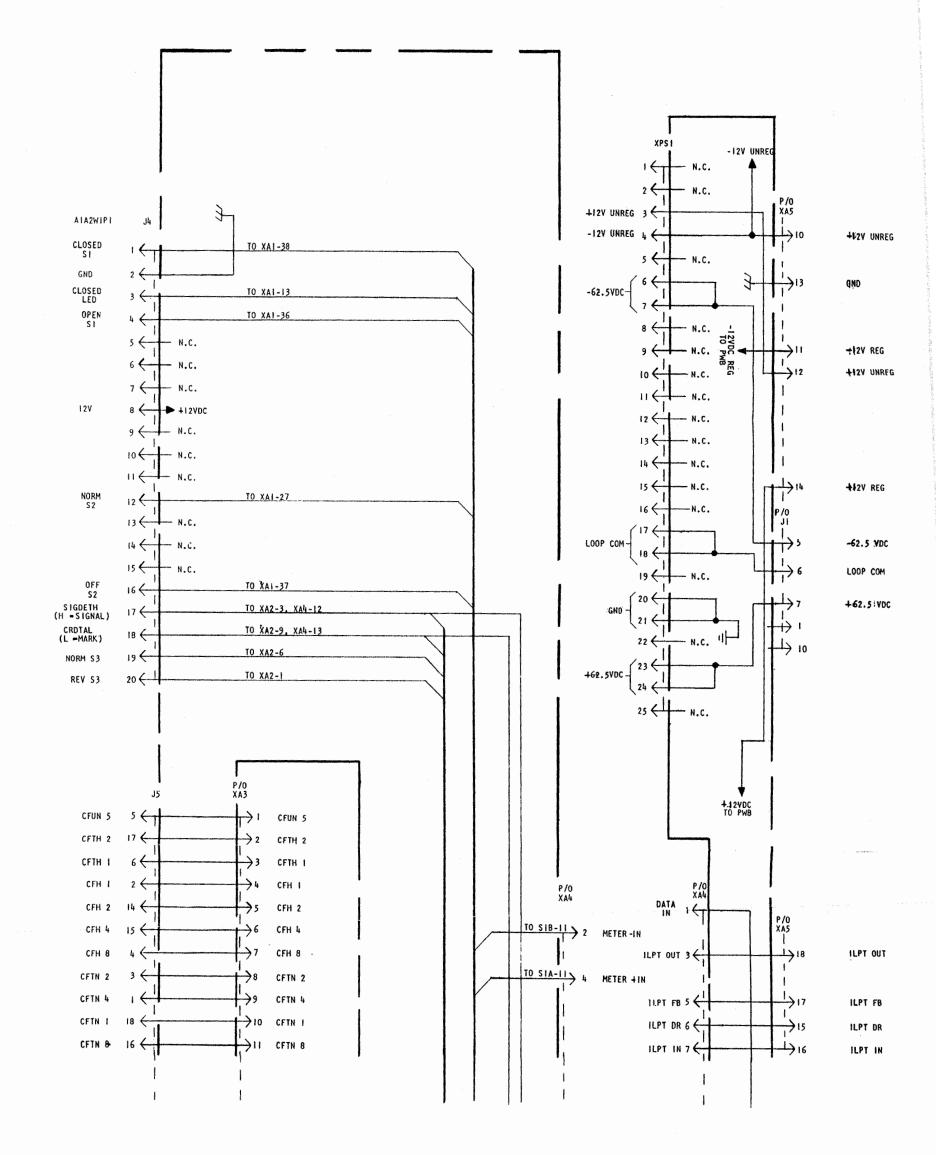

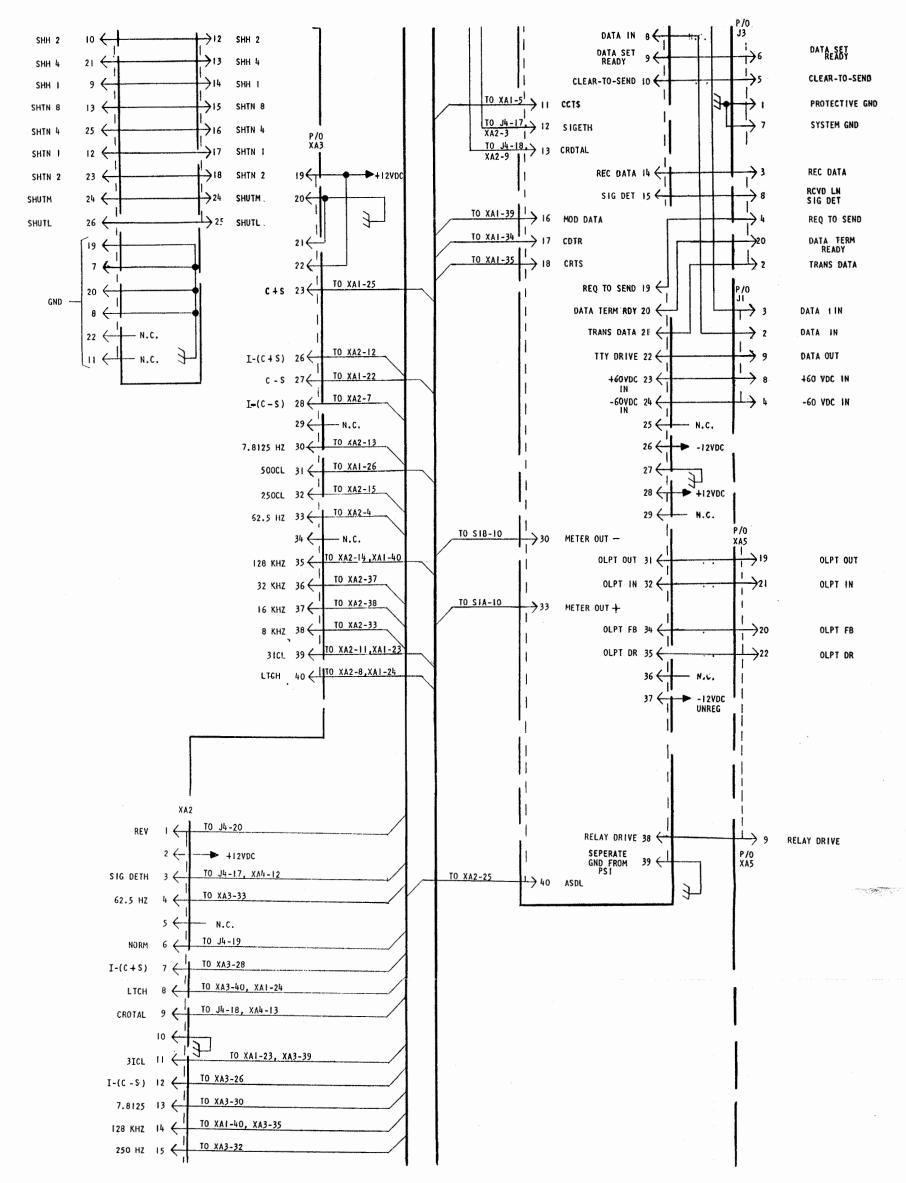

| 4.4.9     | Interconnection Pwb Assembly W1 Description                                                           |

| 4.4.10    | Wiring Assemblies W2 through W4 Details                                                               |

# TABLE OF CONTENTS (Cont.)

# Paragraph

#### Page

#### SECTION 5 MAINTENANCE

| 5.1               | Introduction                                                                                                                                                   |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2               | Troubleshooting and Performance Verification                                                                                                                   |

| 5.3               | Recommended Test Equipment                                                                                                                                     |

| 5.4               | Removal of Modulator Pwb Assembly A1                                                                                                                           |

| 5.5               | Removal of Demodulator Pwb Assembly A2 5-2                                                                                                                     |

| 5.6               | Removal of Timing and Control Pwb Assembly A3                                                                                                                  |

| 5.7               | Removal of Interface Pwb Assembly A4 5-2                                                                                                                       |

| 5.8               | Removal of Transistor/Regulator Pwb Assembly A5                                                                                                                |

| 5.9               | Removal of Power Supply Pwb Assembly PS1                                                                                                                       |

| 5.10              | Removal of Transformer 1T1                                                                                                                                     |

| 5.11              | Removal of Front Panel Assembly                                                                                                                                |

| 5.12              | Removal of Control and Indicator Pwb Assembly A6 5-6                                                                                                           |

| 5.13              | Removal of Frequency and Control Board Assembly A7 5-8                                                                                                         |

| 5.14              | Removal of Meter 1M1 and Circuit Breaker 1CB1 5-8                                                                                                              |

| 5.15              | Removal of Interconnector Pwb Assembly W1                                                                                                                      |

| 5.16              | Pwb Replacement - Special Instructions 5-9                                                                                                                     |

| 5.17              | RF-3352 FSK Terminal Voltage Source Data                                                                                                                       |

| 5.18              | RF-3352 FSK Terminal Adjustment, Control and Test Point Locations 5-9                                                                                          |

| 5.19              | Test Point Typical Data Tables                                                                                                                                 |

| 5-20              | RF-3352 FSK Terminal Alignment Procedures                                                                                                                      |

| 5.20.1            | Modulator PWB Assembly A1 Alignment Procedures                                                                                                                 |

| 5.20.2            | Demodulator PWB Assembly A2 Alignment Procedures                                                                                                               |

| 5.20.3            | Alignment Procedures - Timing and Control PWB A3, Transistor (Regulator PWB A5, Control and Indicator PWB A6, Frequency Control Board A7, and Power Supply PWB |

|                   | PS1)                                                                                                                                                           |

| 5.20.4            | Interface PWB Assembly A4 Alignment Procedures                                                                                                                 |

|                   | SECTION 6 PARTS LISTS AND COMPONENT LOCATION DRAWINGS                                                                                                          |

| 6.1<br>6.2        | Introduction                                                                                                                                                   |

|                   | SECTION 7 SCHEMATIC DIAGRAMS AND RELATED DATA                                                                                                                  |

| 7.1<br>7.2<br>7.3 | Introduction       7-1         Schematic Diagram List       7-1         Abbreviations and Acronyms       7-1                                                   |

| 74                | Connector Pin, Adjustment and Test Point Reference Data                                                                                                        |

# LIST OF ILLUSTRATIONS

# Figure

.

| 1-1        | Model RF-3352 FSK Terminal 1-0                                                       |

|------------|--------------------------------------------------------------------------------------|

| 2-1        | RF-3352 FSK Terminal/Teletypewriter Interconnection and Operational Discipline -     |

|            | Neutral Mode - Common Loop (Half Duplex)                                             |

| 2-2        | RF-3352 FSK Terminal/Teletypewriter Interconnection - Neutral Mode - Independent     |

|            | Loops (Full Duplex)                                                                  |

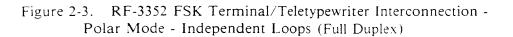

| 2-3        | RF-3352 FSK Terminal/Teletypewriter Interconnection - Polar Mode - Independent Loops |

| <b>-</b> . | (Full Duplex).                                                                       |

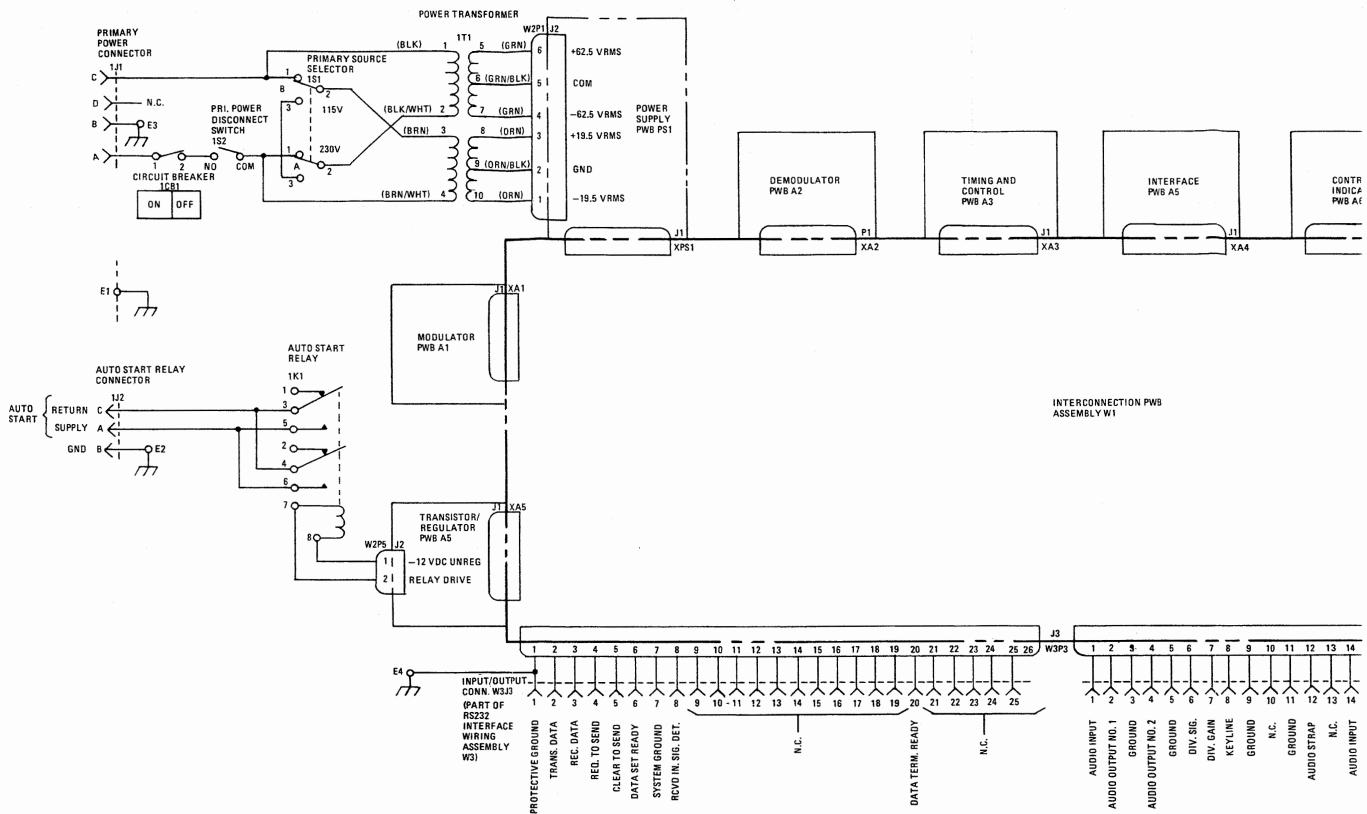

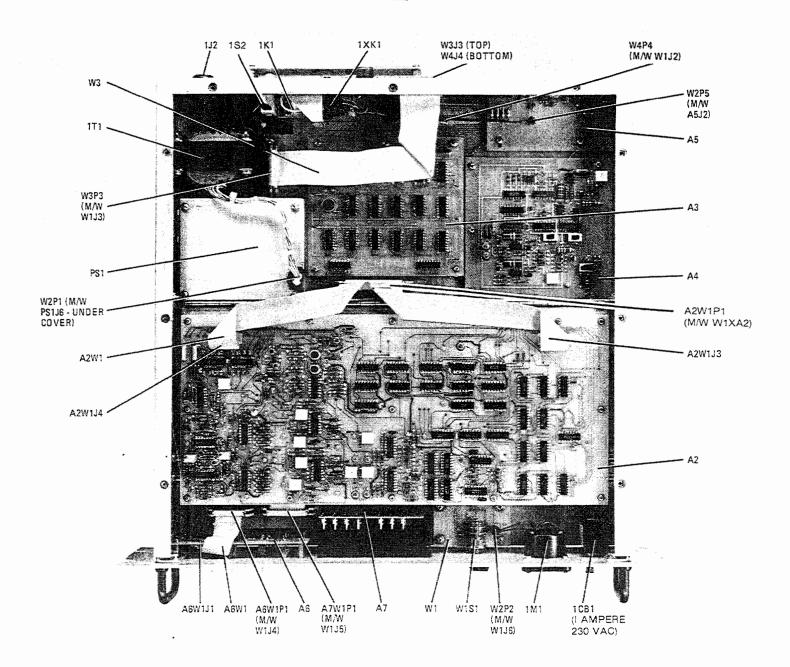

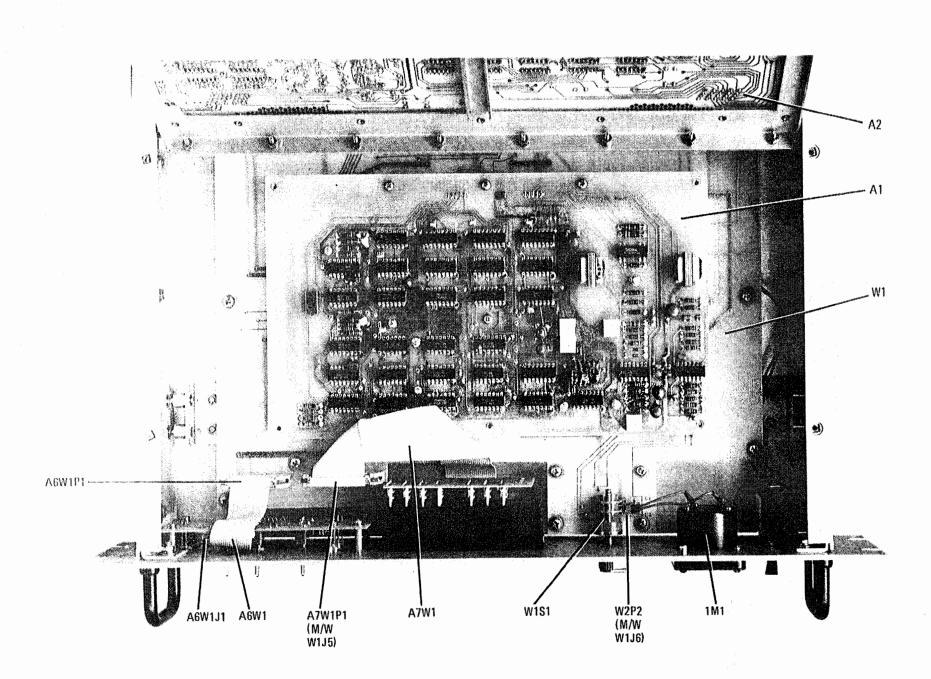

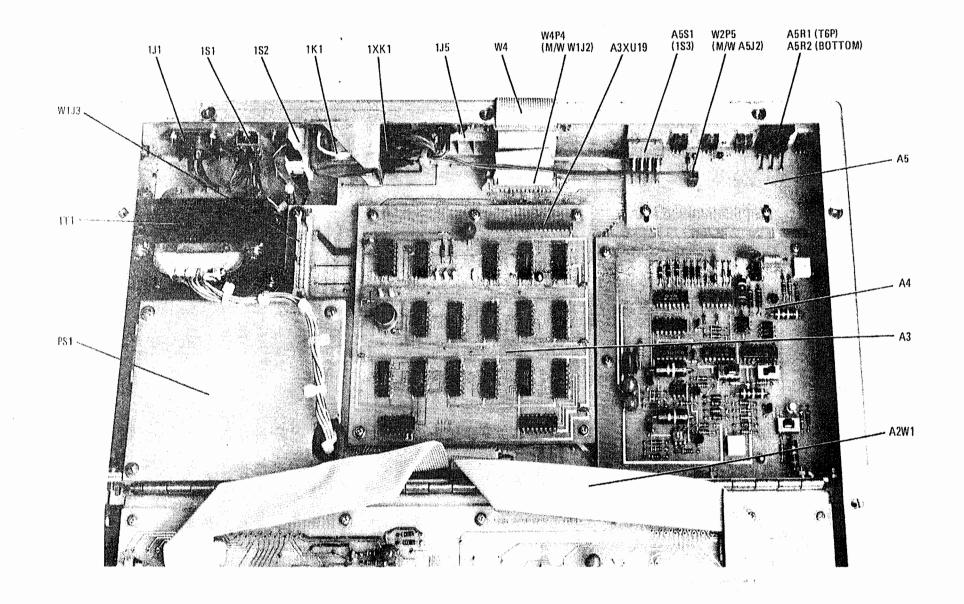

| 2-4        | RF-3352 FSK Terminal Interconnection and Assembly Identification Diagram             |

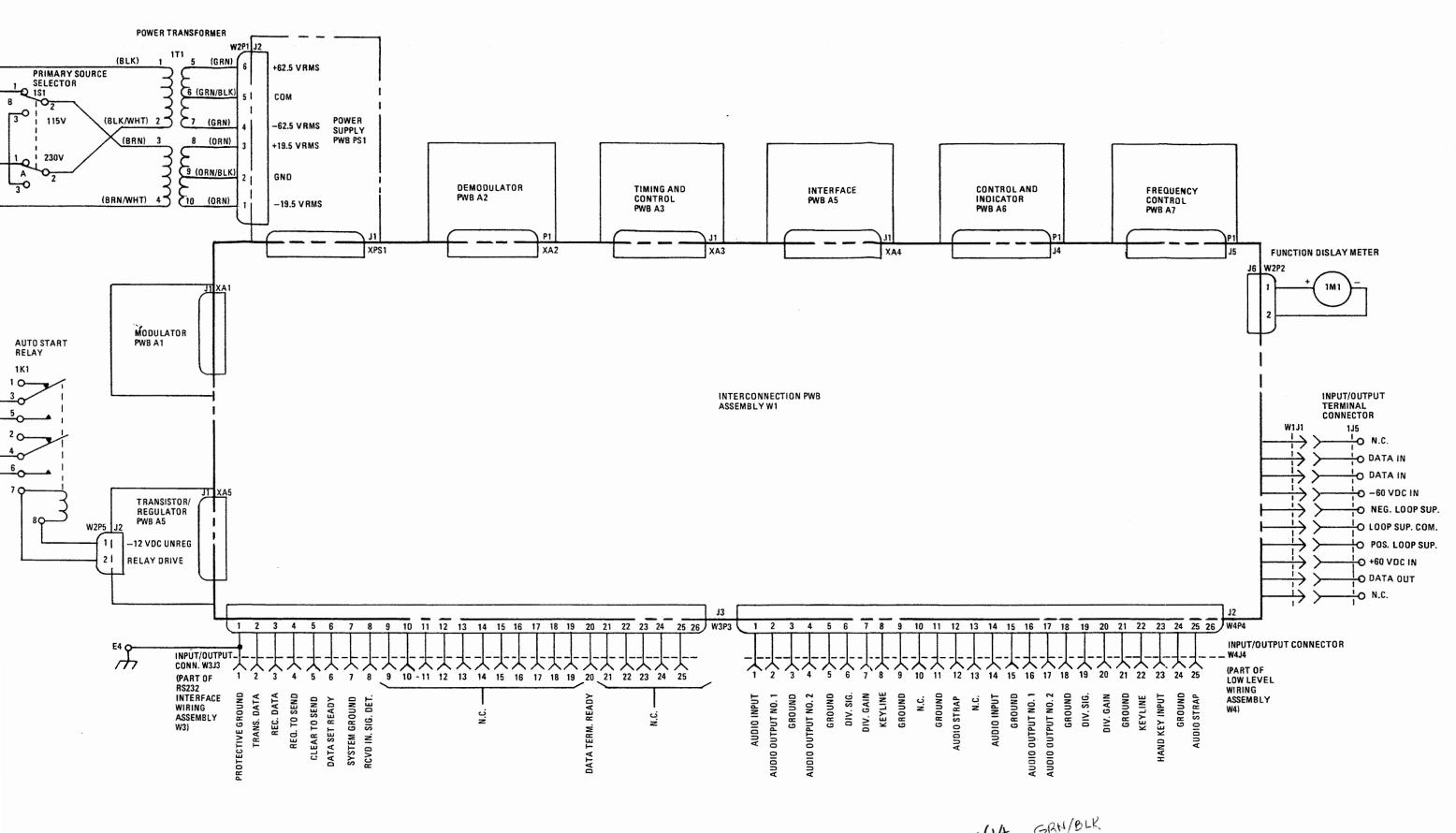

| 3-1        | RF-3352 FSK Terminal Front Panel Controls, Indicators and Switches                   |

| 3-2        | RF-3352 FSK Terminal Rear Panel Connectors, Controls and Switches                    |

| 4-1        | Modulator Pwb Assembly A1 Functional Block Diagram                                   |

| 4-2        | Demodulator Pwb Assembly A2 Functional Block Diagram                                 |

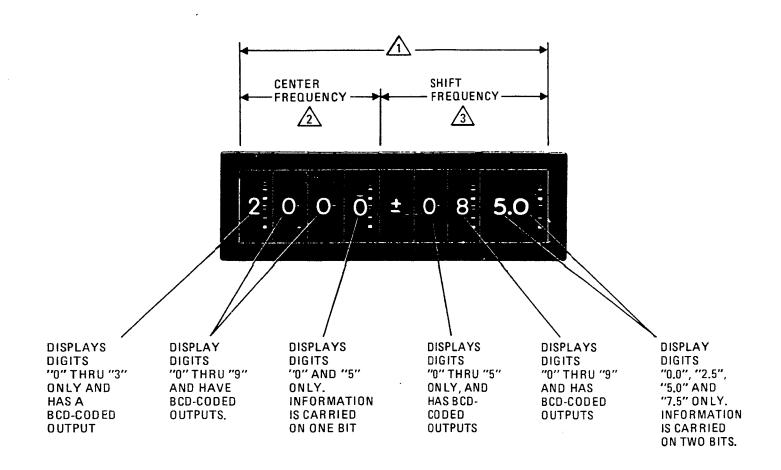

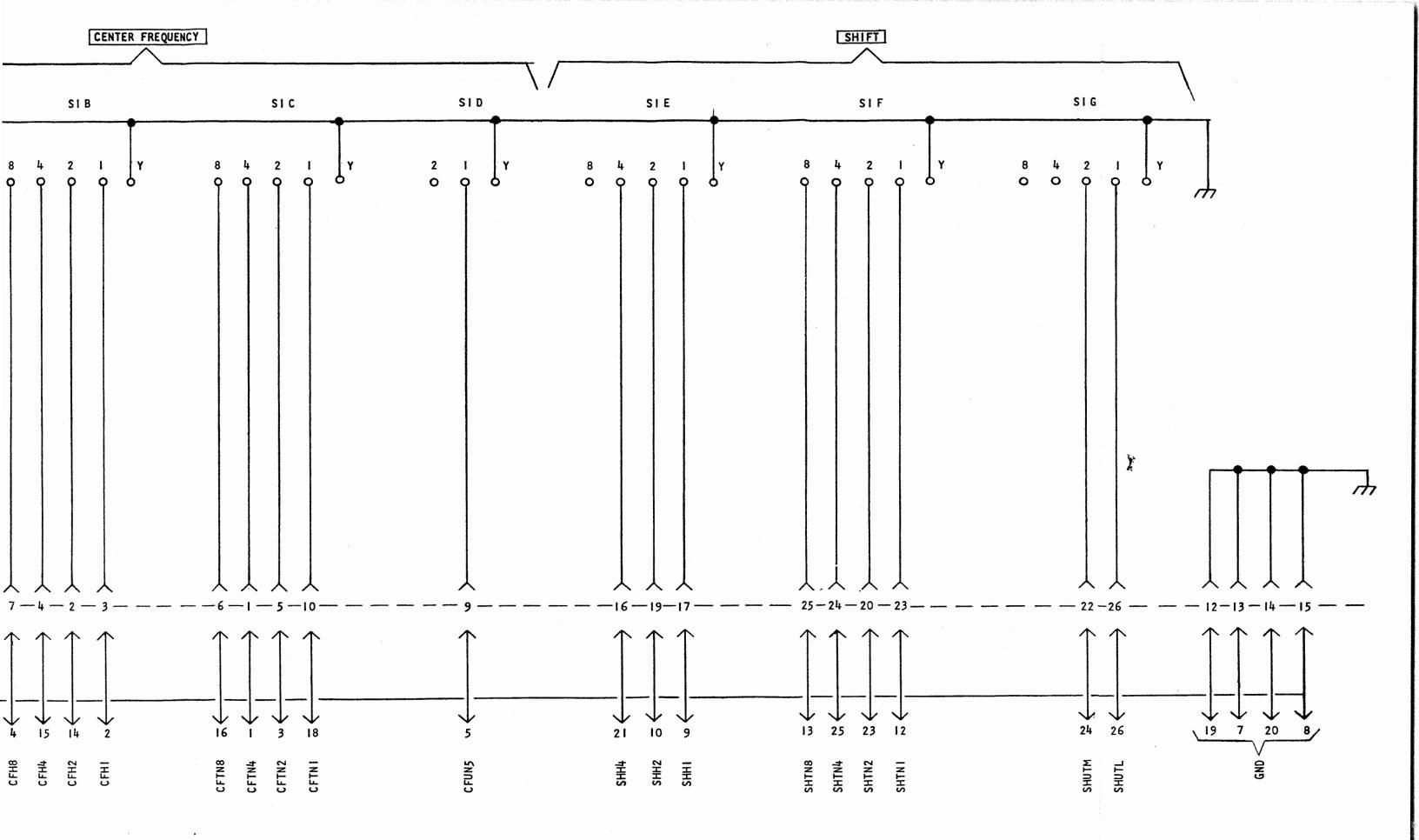

| 4-3        | Frequency Selector Switch Technical Parameters                                       |

| 4-4        | Timing and Control Pwb Assembly A3 Functional Block Diagram                          |

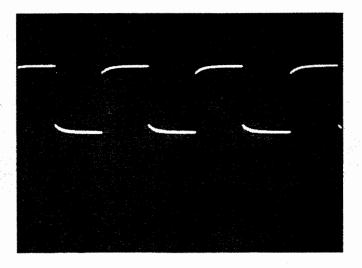

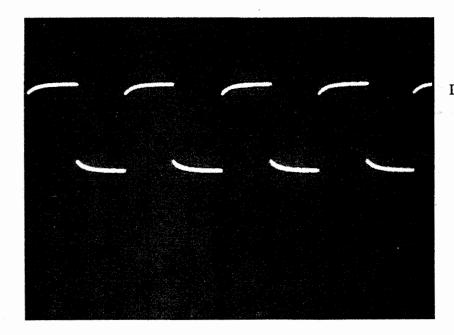

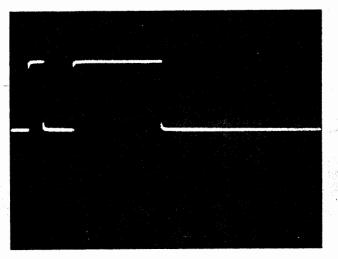

| 4-5        | Conversion Process Waveform Data                                                     |

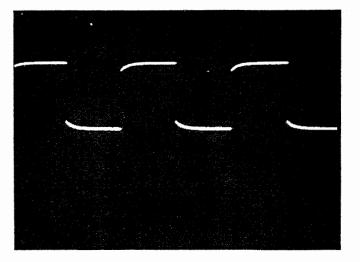

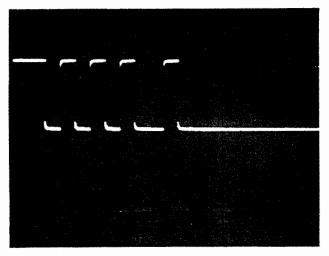

| 4-6        | Typical Data Output and Its Interpretation During Read Period                        |

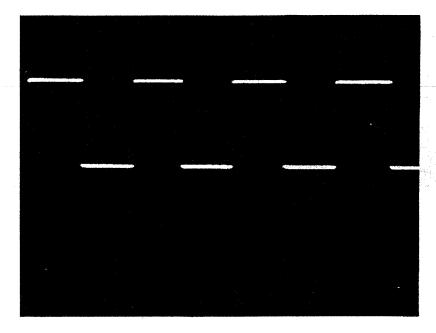

| 4-7        | Latch Timing Relationships                                                           |

| 4-8        | Production and Interpretation of the 8 kHz (Local Oscillator) Frequency              |

| 4-9        | Interface Pwb Assembly A4 Functional Block Diagram                                   |

| 4-10       | Interface Pwb A4 Input Loop Circuitry                                                |

| 4-11       | Interface Pwb A4 Output Loop Driver Circuitry                                        |

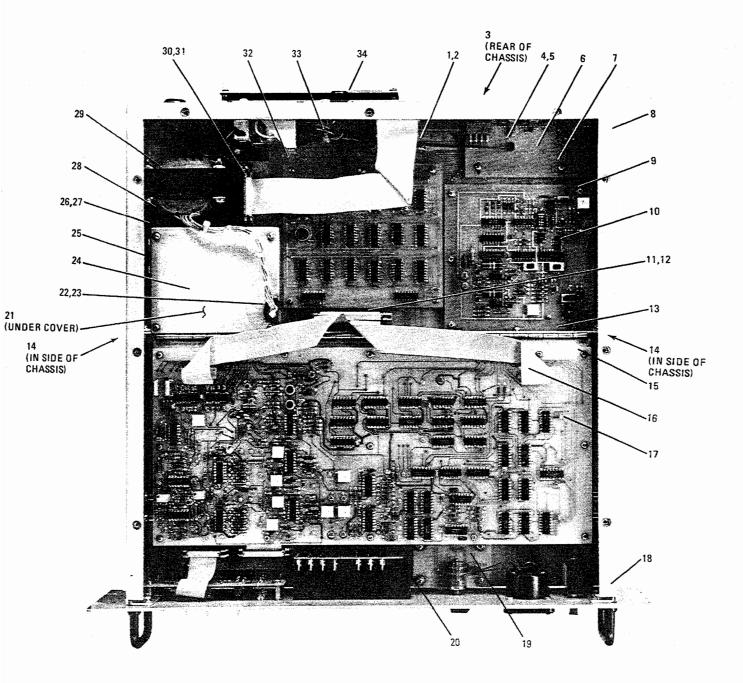

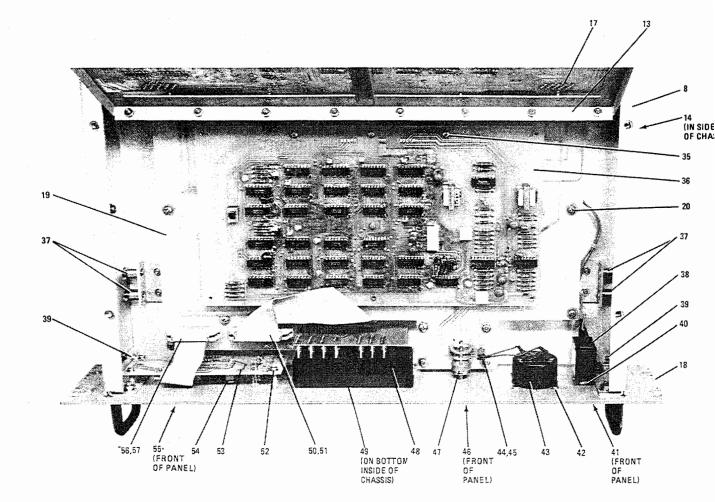

| 5-1        | RF-3352 FSK Terminal Disassembly Details. 5-3                                        |

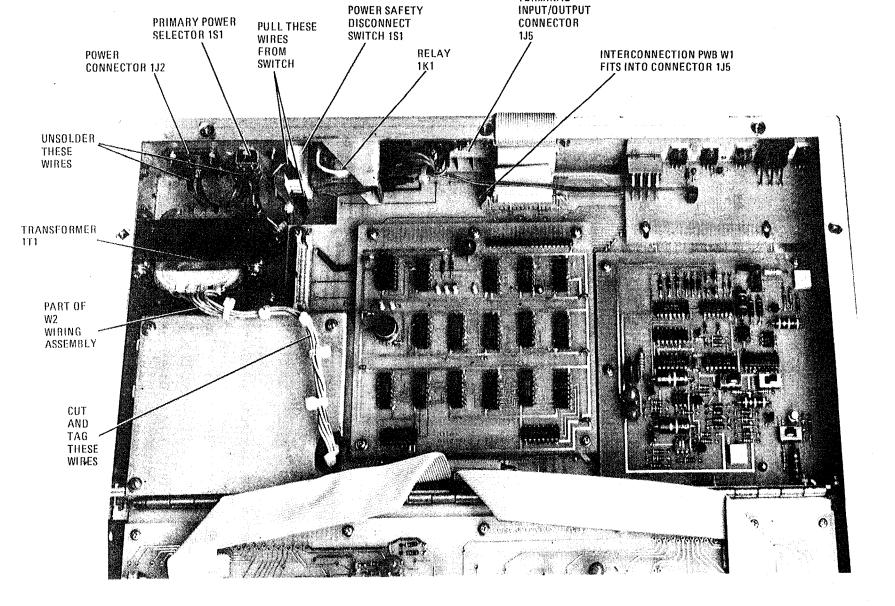

| 5-2        | RF-3352 FSK Terminal - Transformer 1T1 and Inside Rear Panel Component Replacement   |

|            | Details                                                                              |

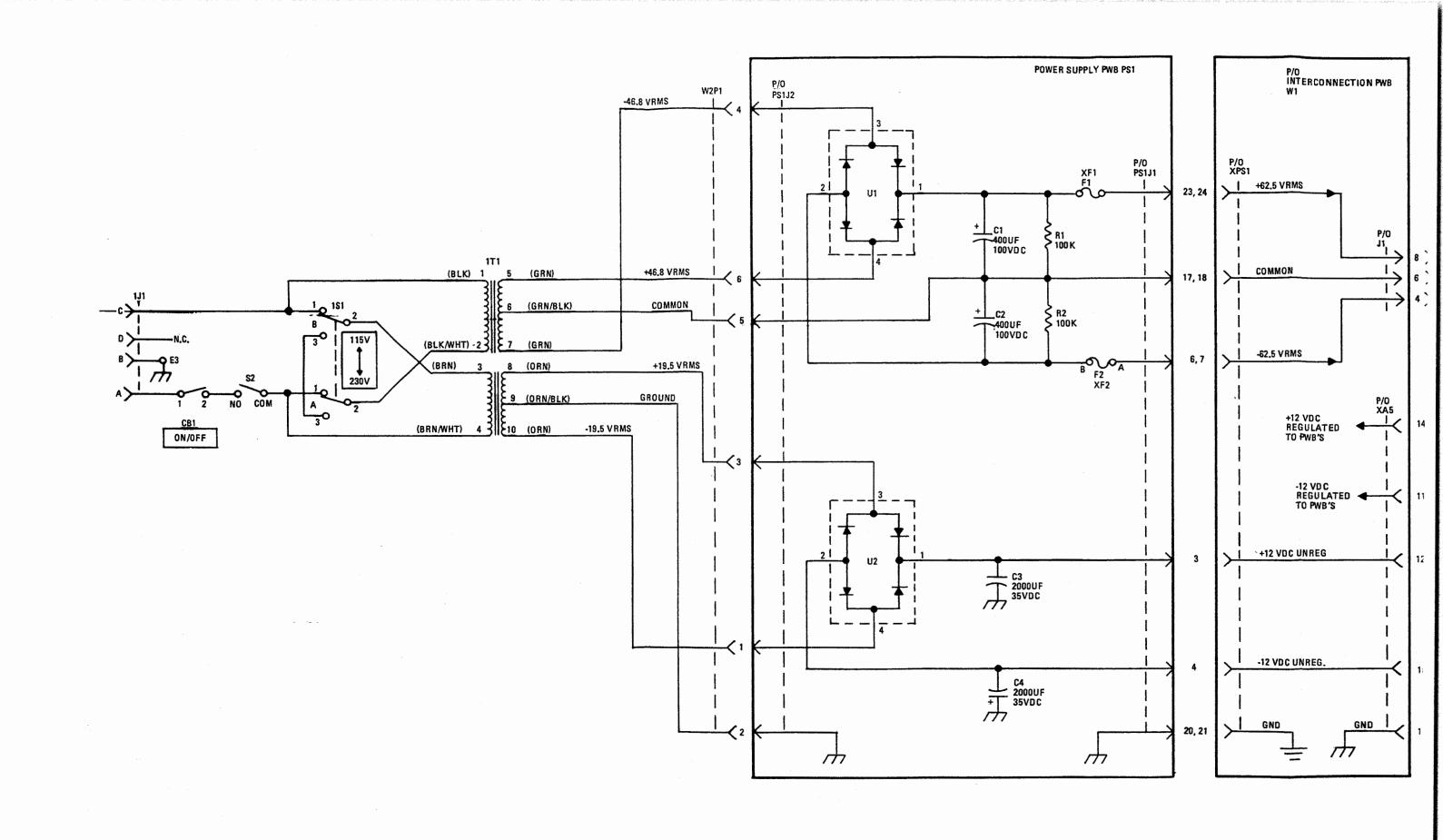

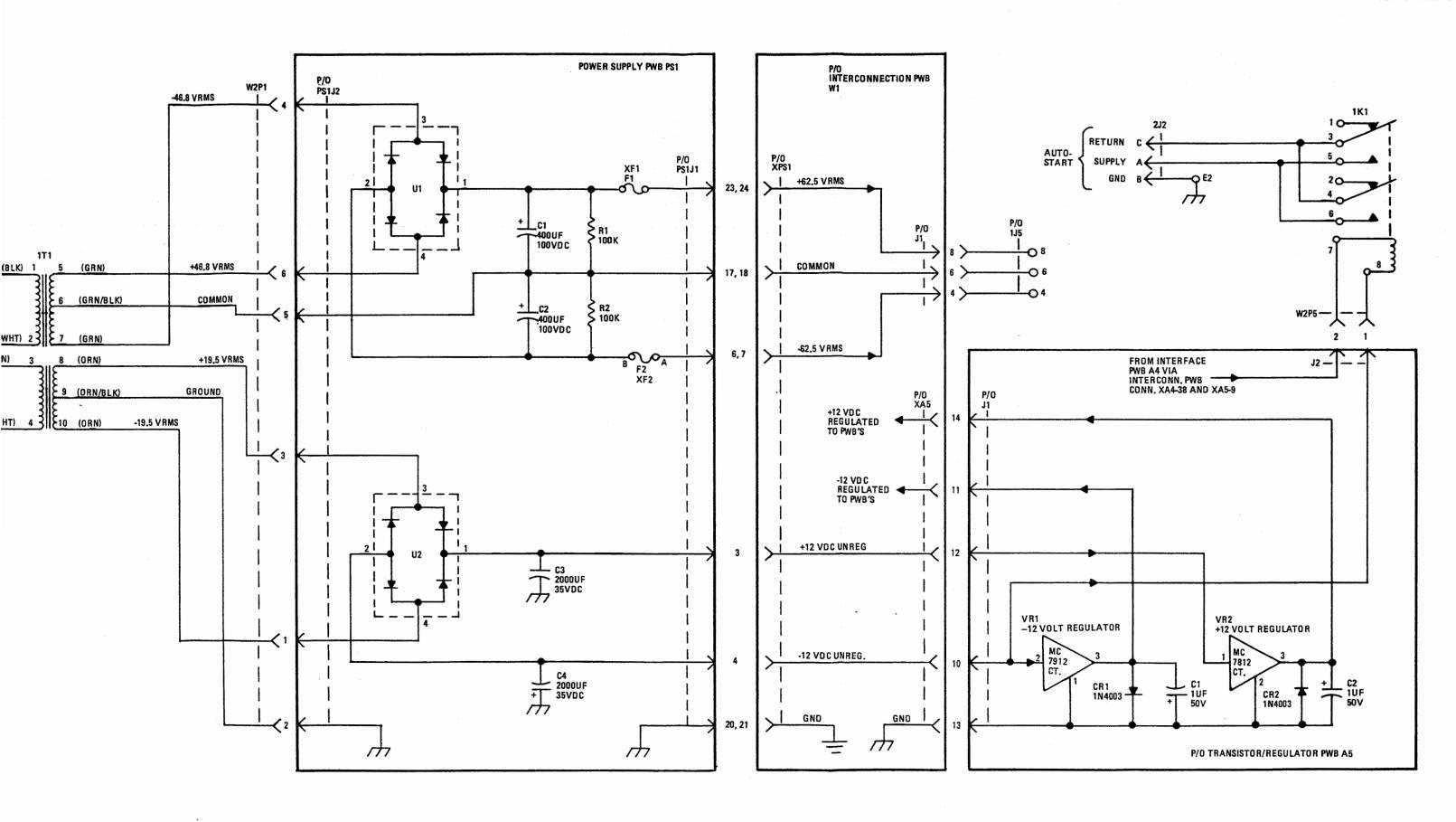

| 5-3        | RF-3352 FSK Terminal Voltage Source Diagram                                          |

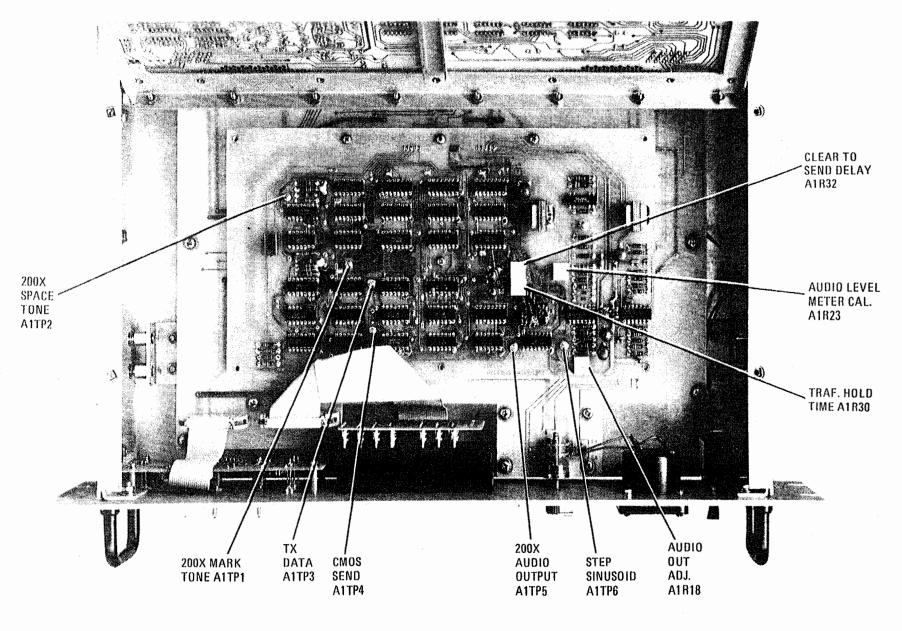

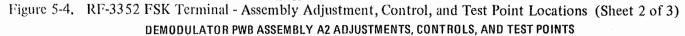

| 5-4        | RF-3352 FSK Terminal - Assembly Adjustment, Control and Test Point Locations         |

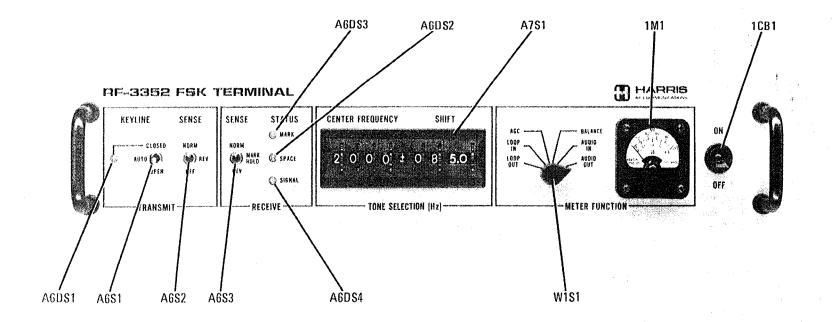

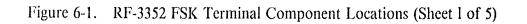

| 6-1        | RF-3352 FSK Terminal Component Locations                                             |

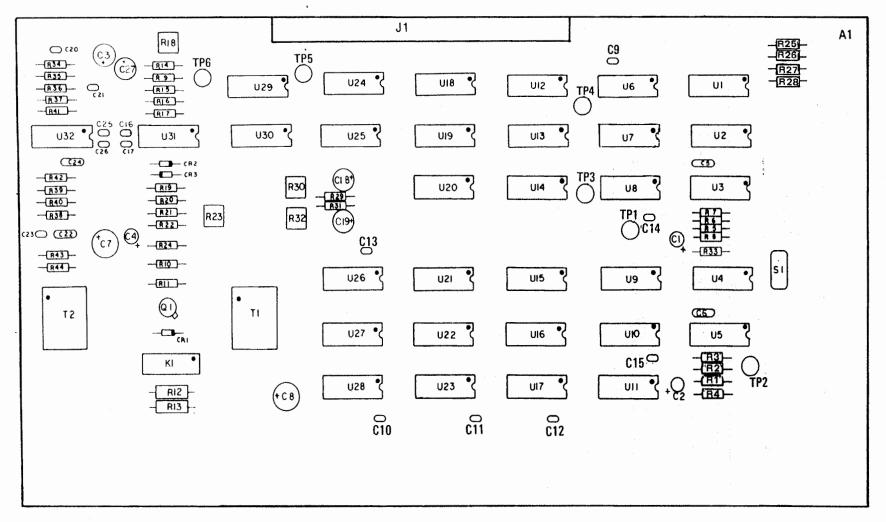

| 6-2        | Modulator Pwb A1 Component Locations                                                 |

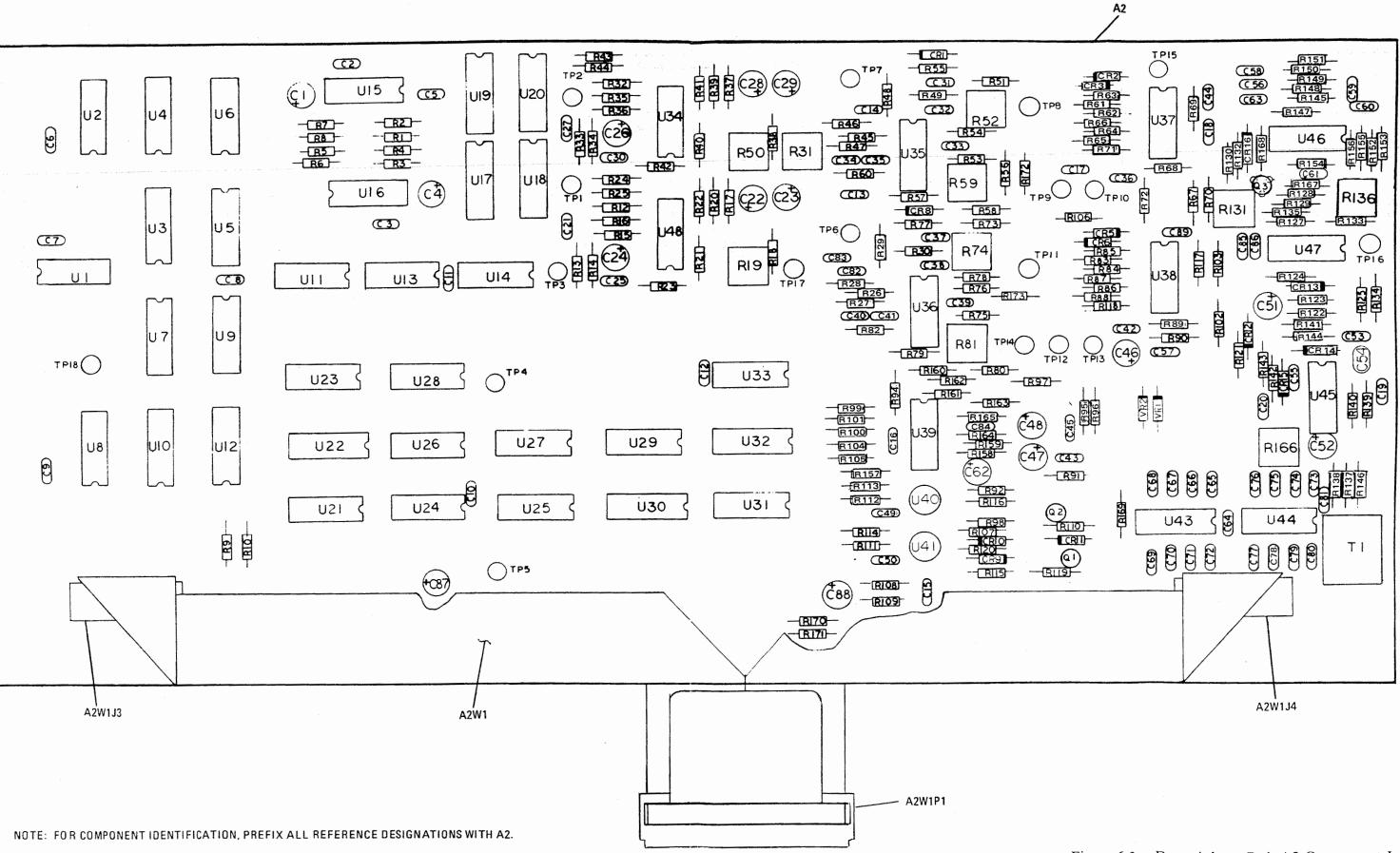

| 6-3        | Demodulator Pwb A2 Component Locations                                               |

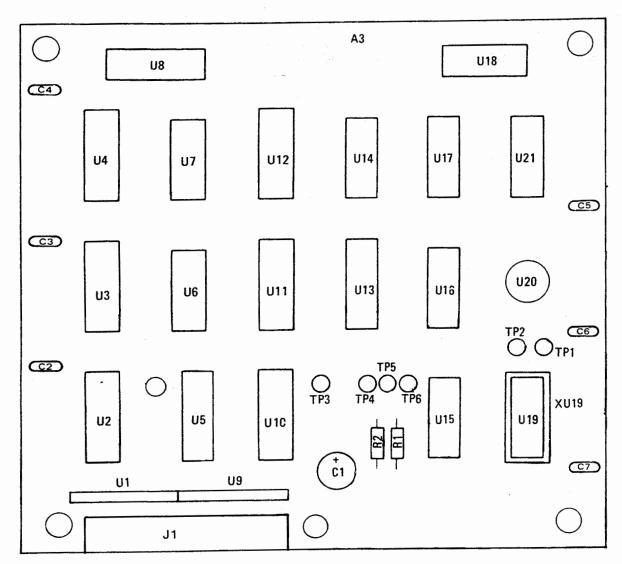

| 6-4        | Timing and Control Pwb A3 Component Locations                                        |

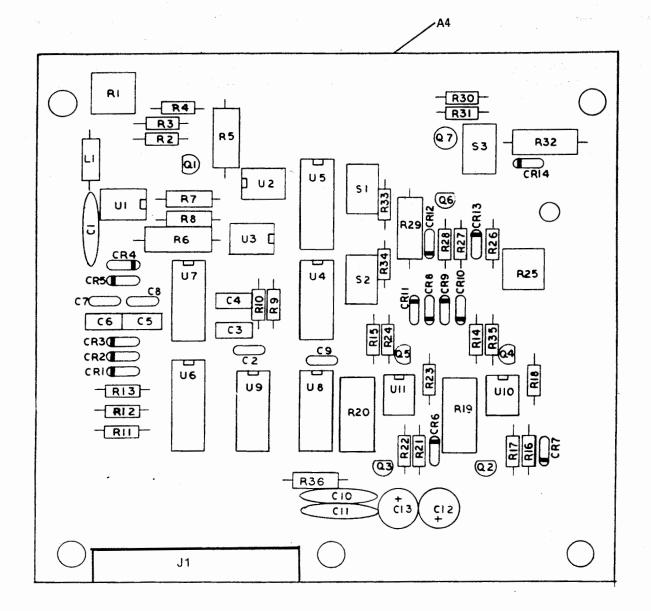

| 6-5        | Interface Pwb A4 Component Locations                                                 |

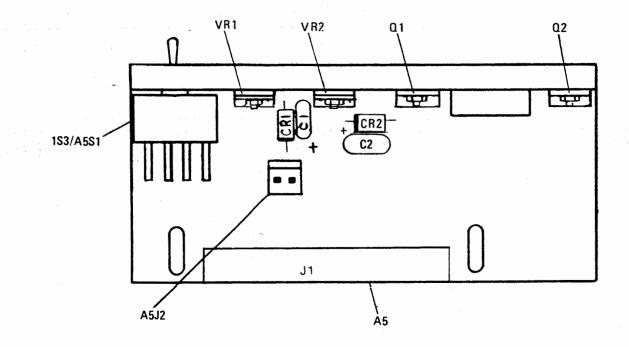

| 6-6        | Transistor/Regulator Pwb A5 Component Locations                                      |

| 6-7        | Control and Indicator Pwb A6 Component Locations                                     |

| 6-8        | Frequency Control Board A7 Component Locations                                       |

| 6-9        | Power Supply Pwb PS1 Component Locations                                             |

| 6-10       | Interconnection Pwb A1 Component Locations                                           |

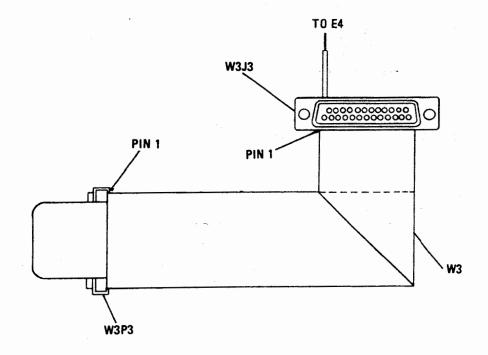

| 6-11       | RS-232 Interface Wiring Assembly W3 Component Locations                              |

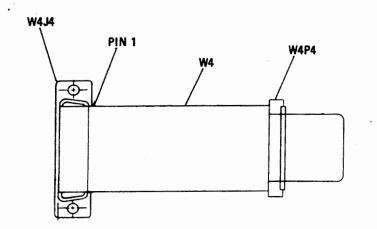

| 6-12       | Low Level Wiring Assembly W4 Component Locations                                     |

| 7-1        | RF-3352 FSK Terminal Chassis and Panel Assembly Schematic Diagram                    |

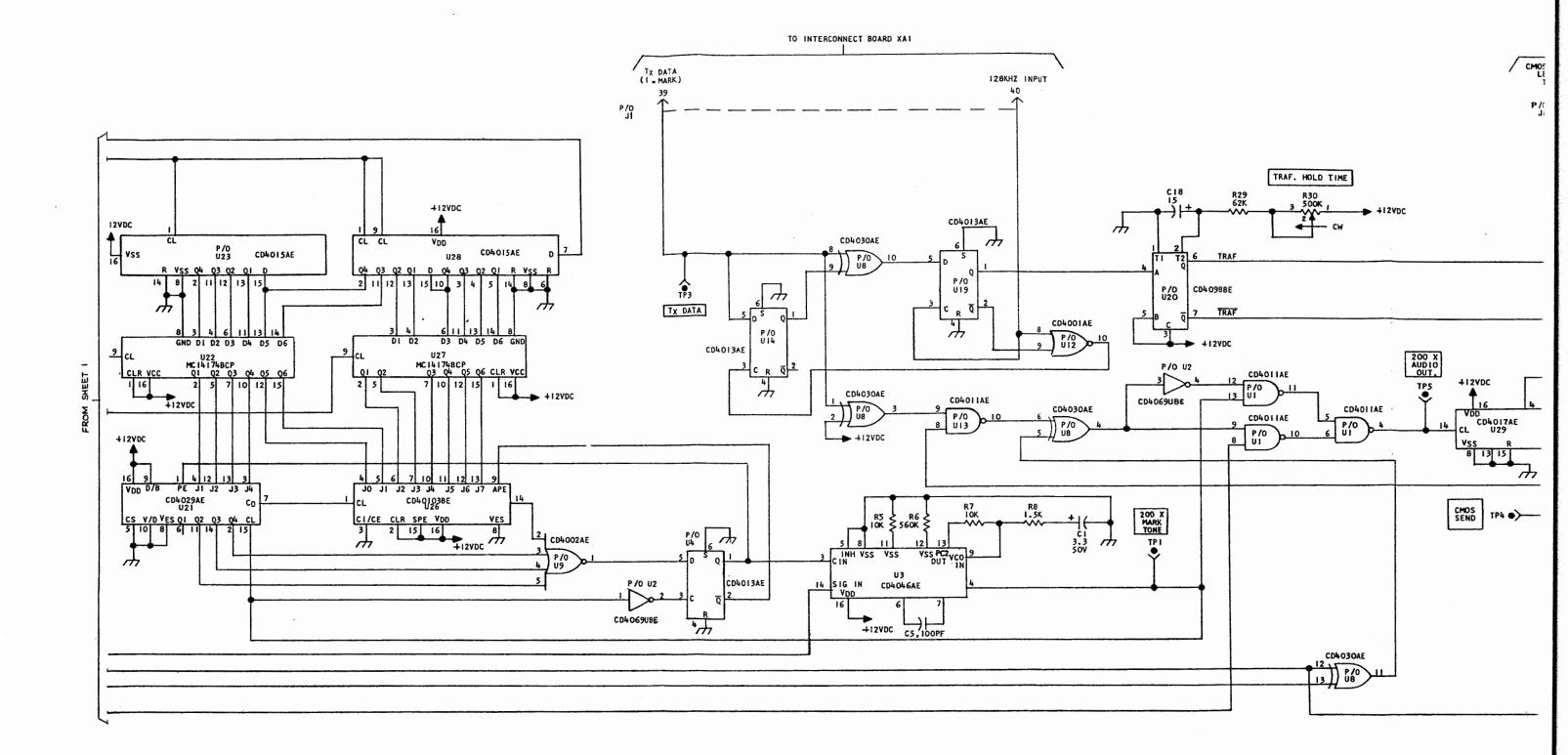

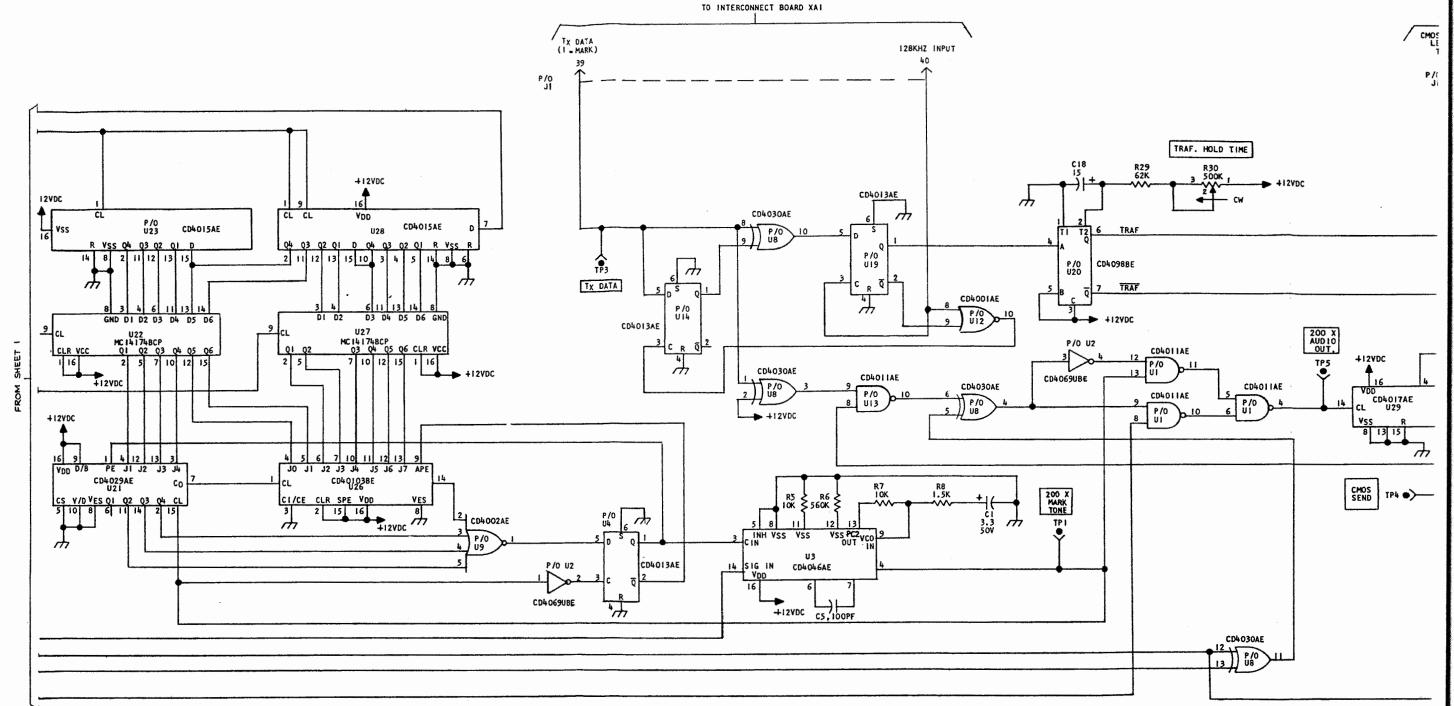

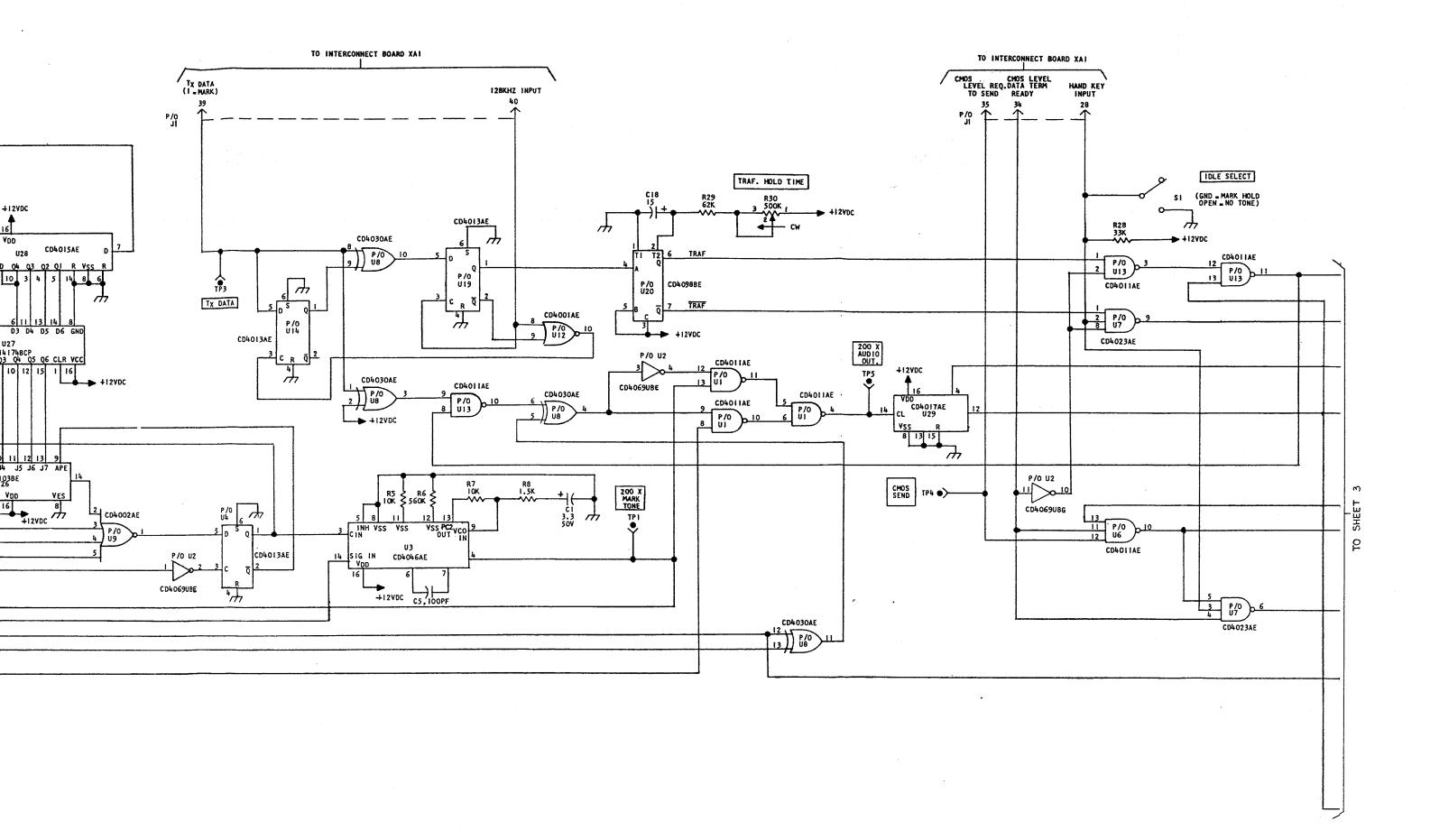

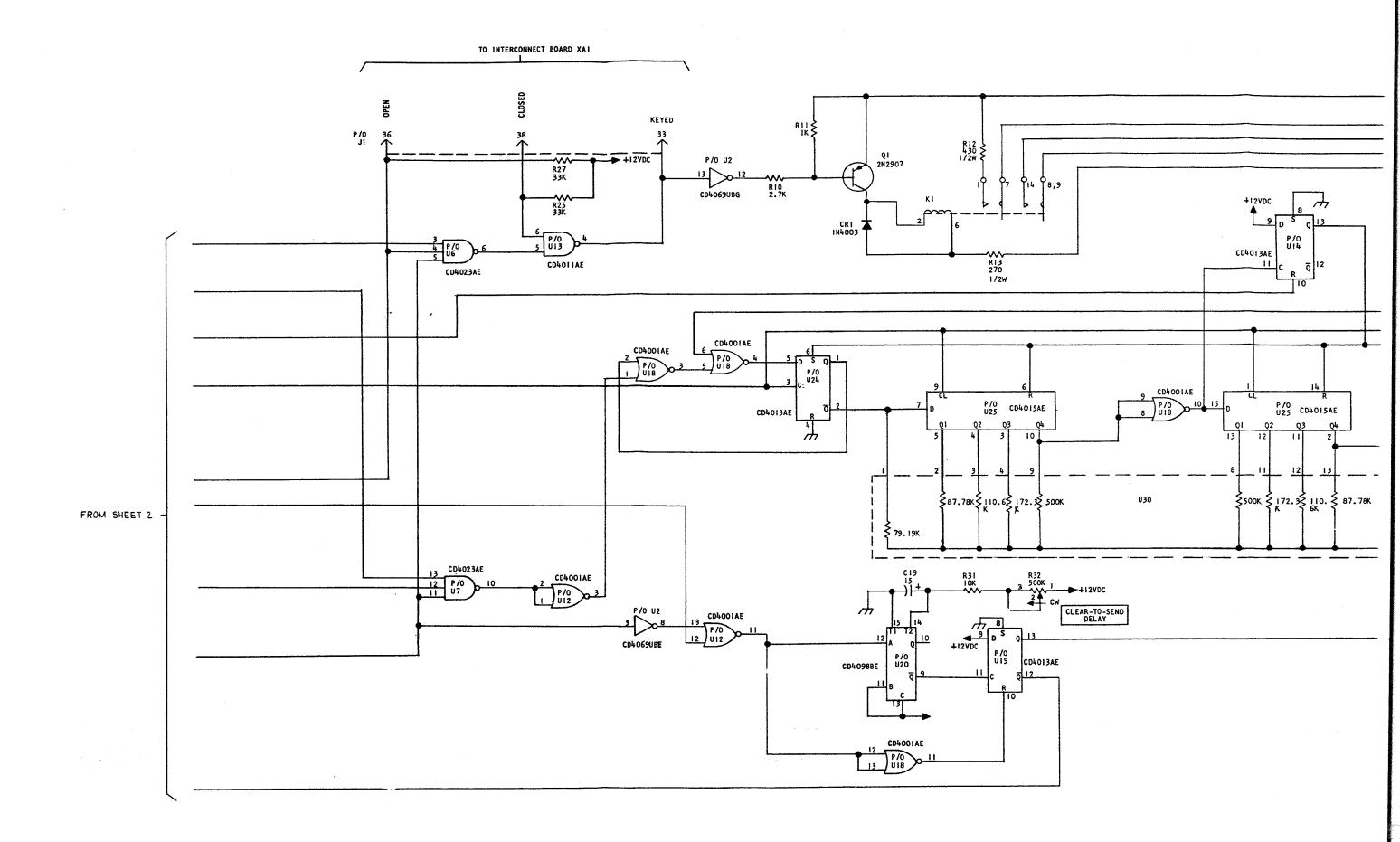

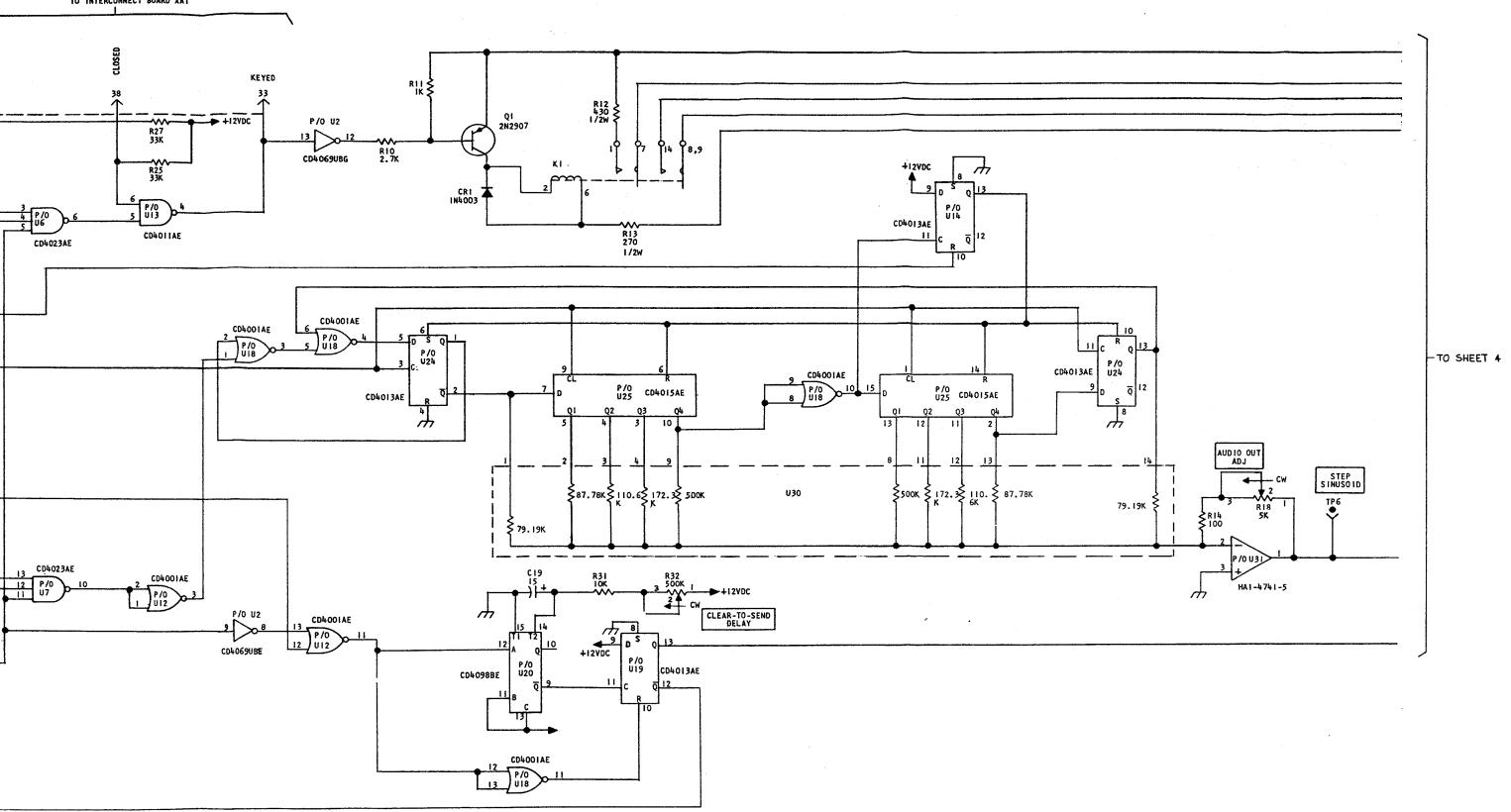

| 7-2        | Modulator Pwb A1 Schematic Diagram                                                   |

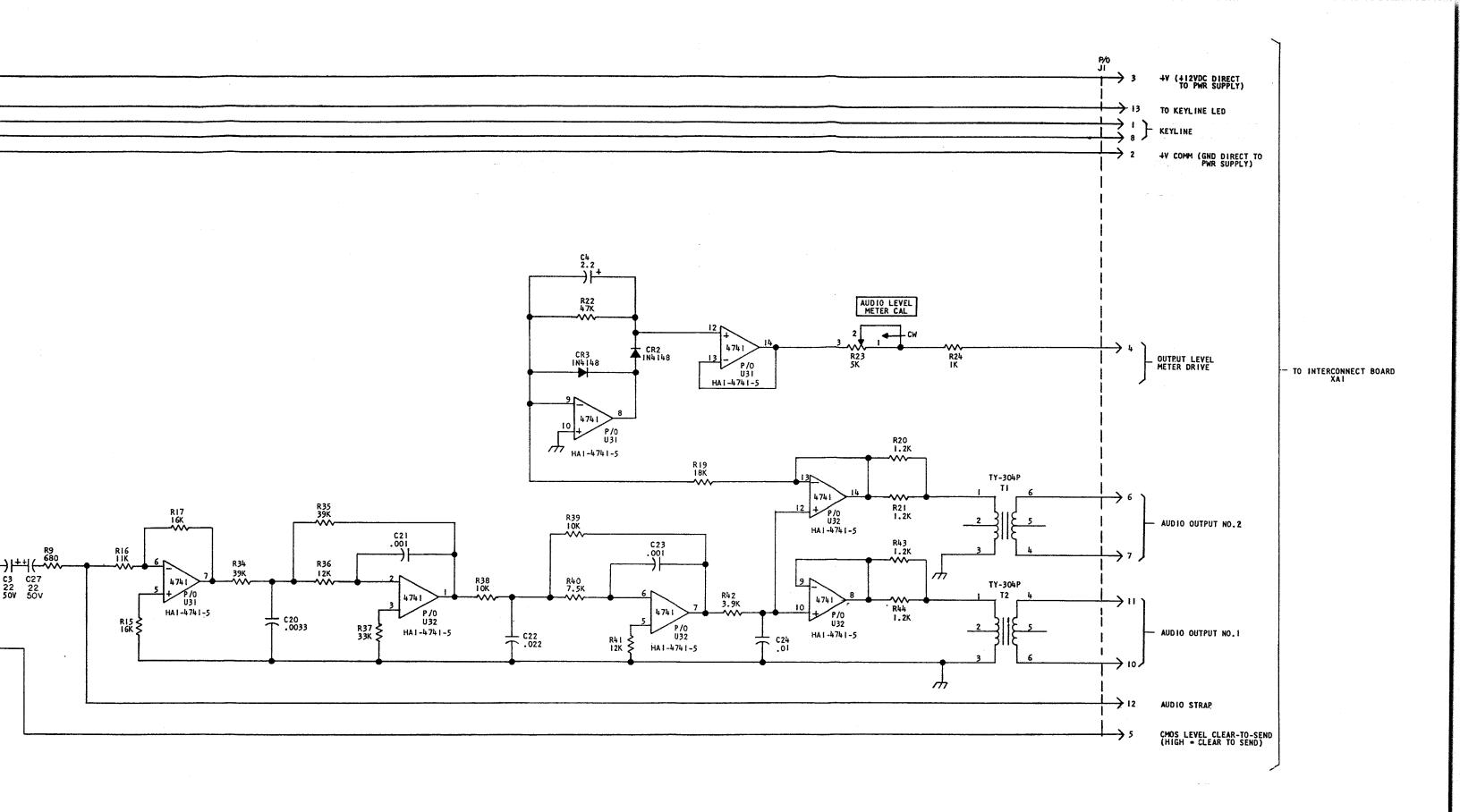

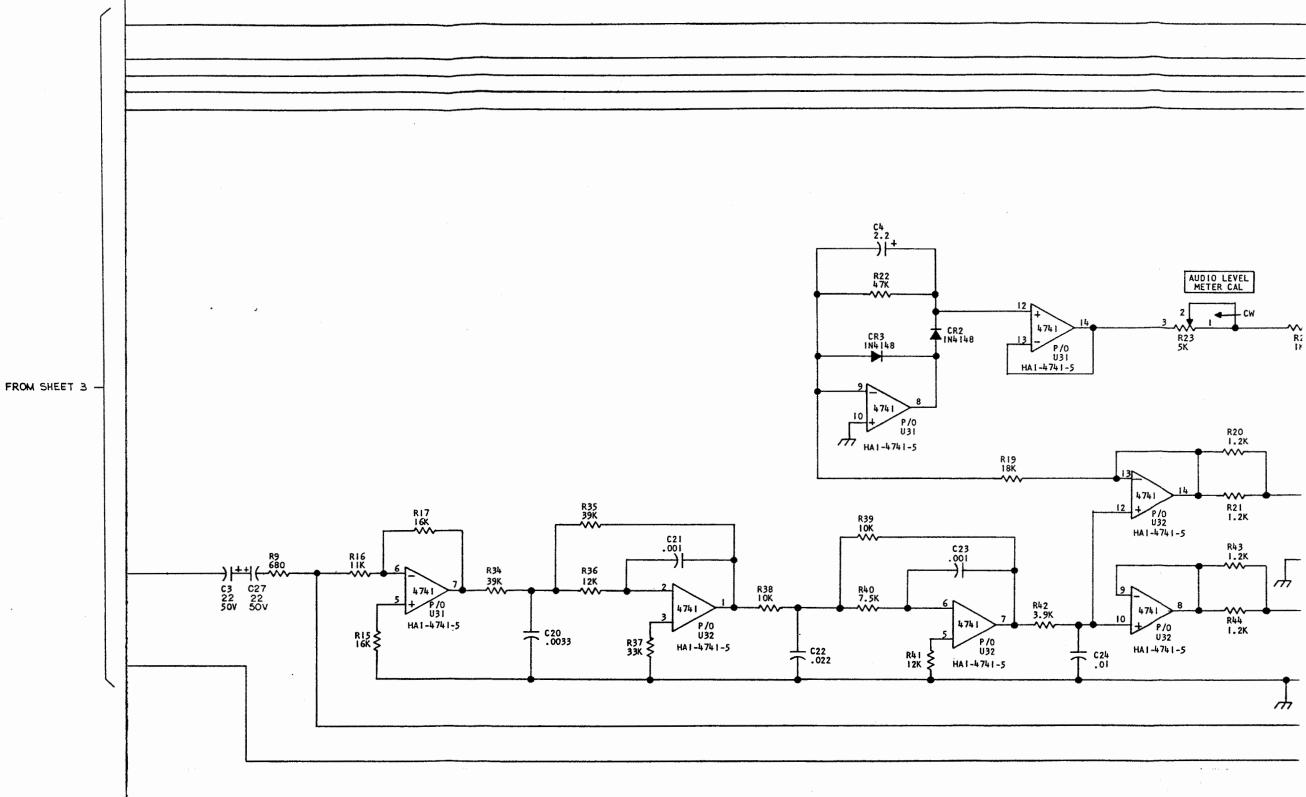

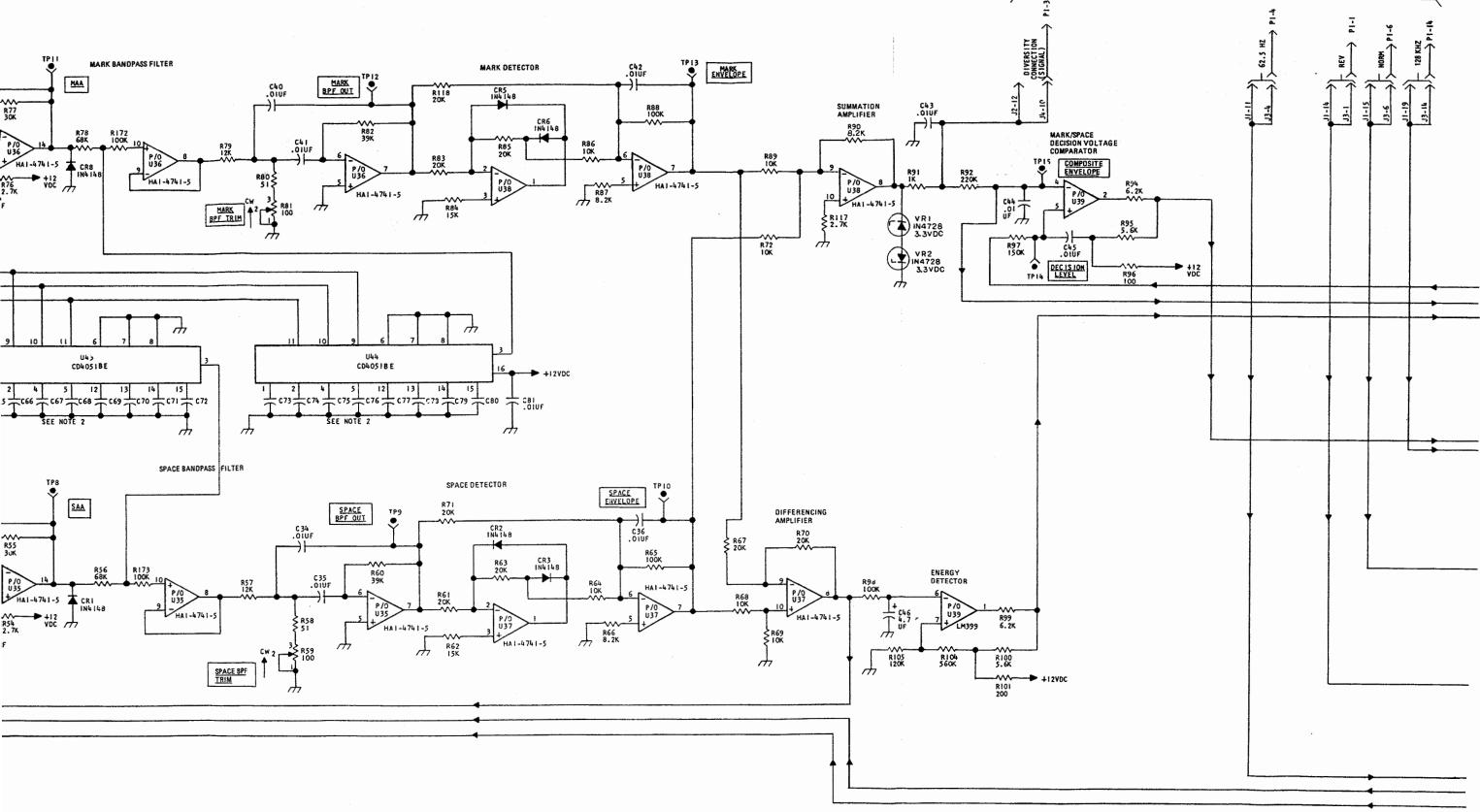

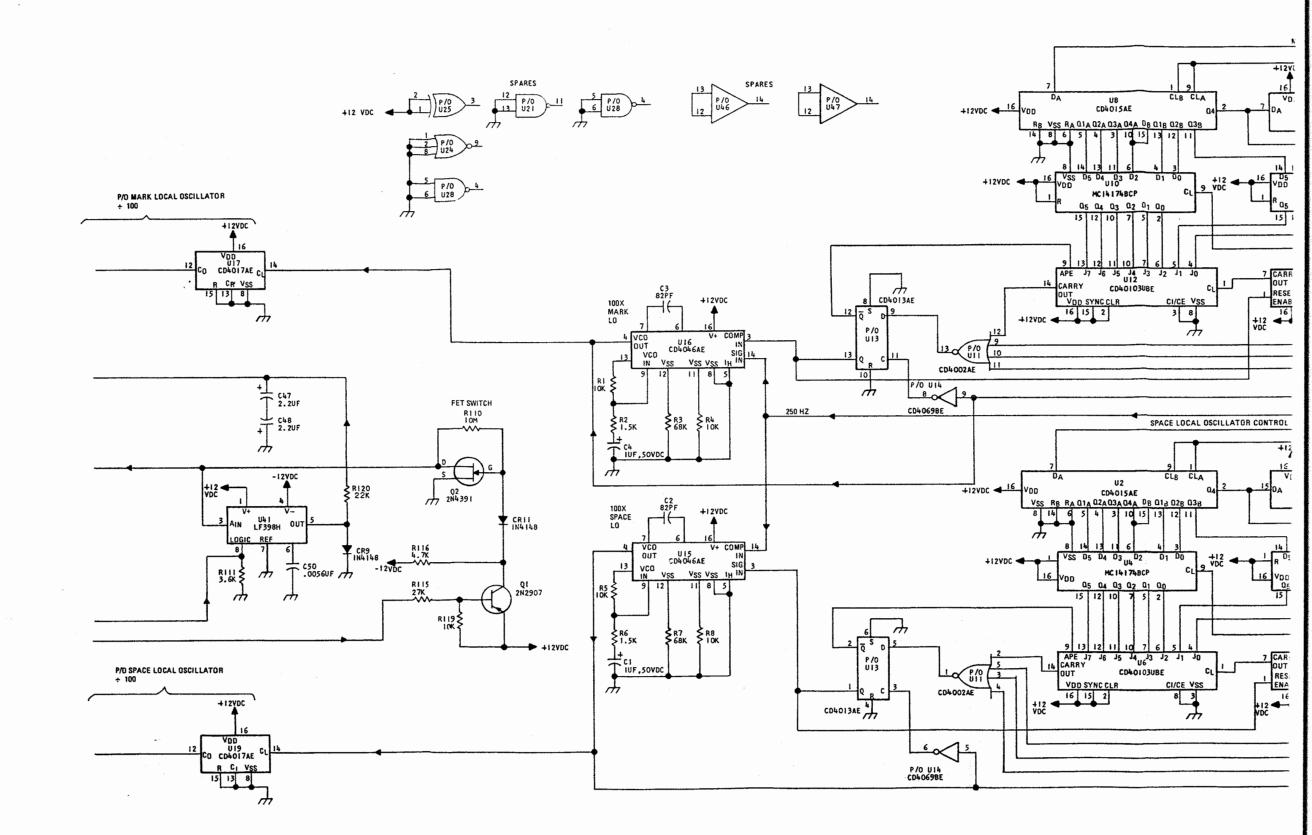

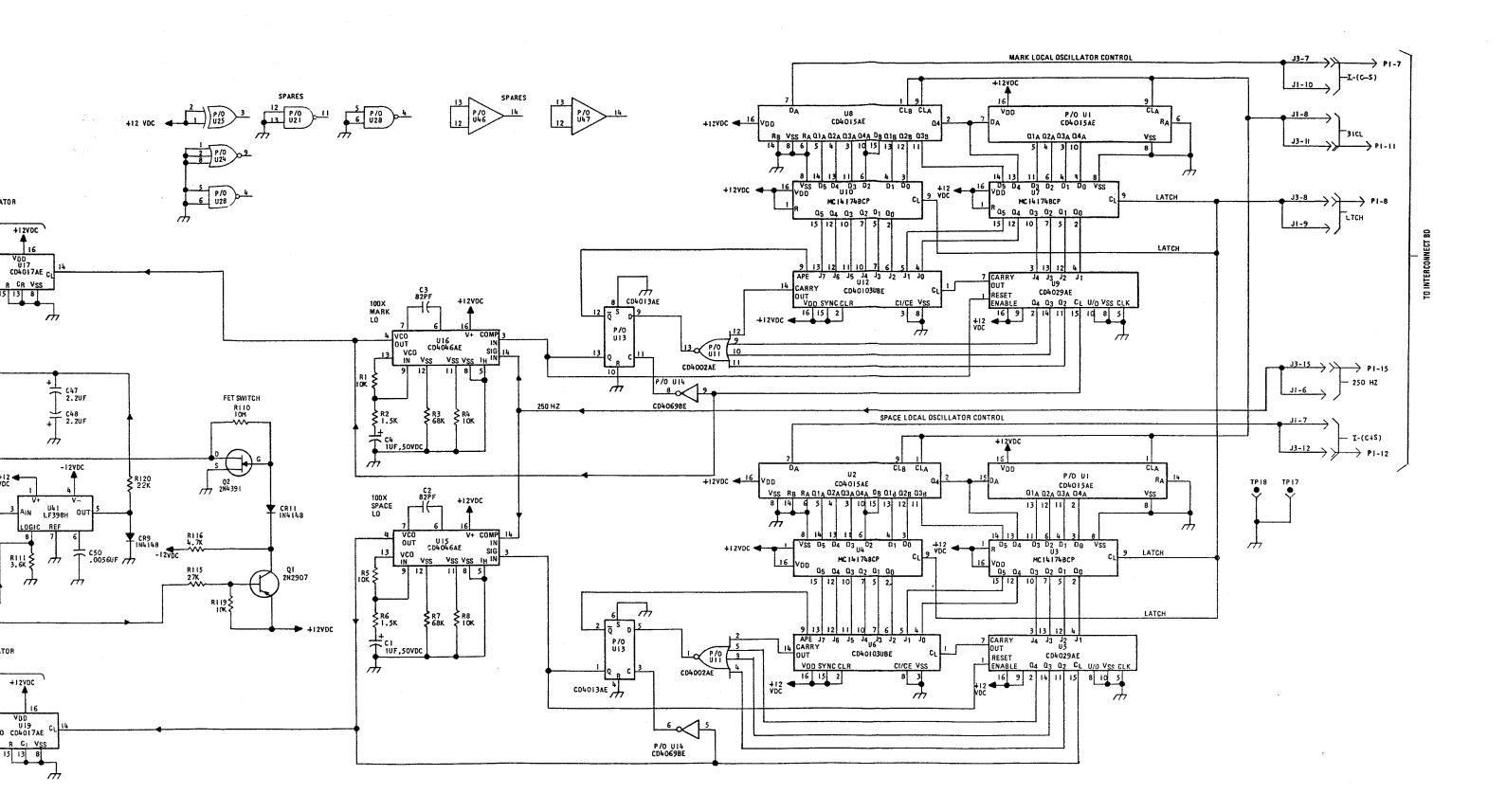

| 7-3        | Demodulator Pwb A2 Schematic Diagram                                                 |

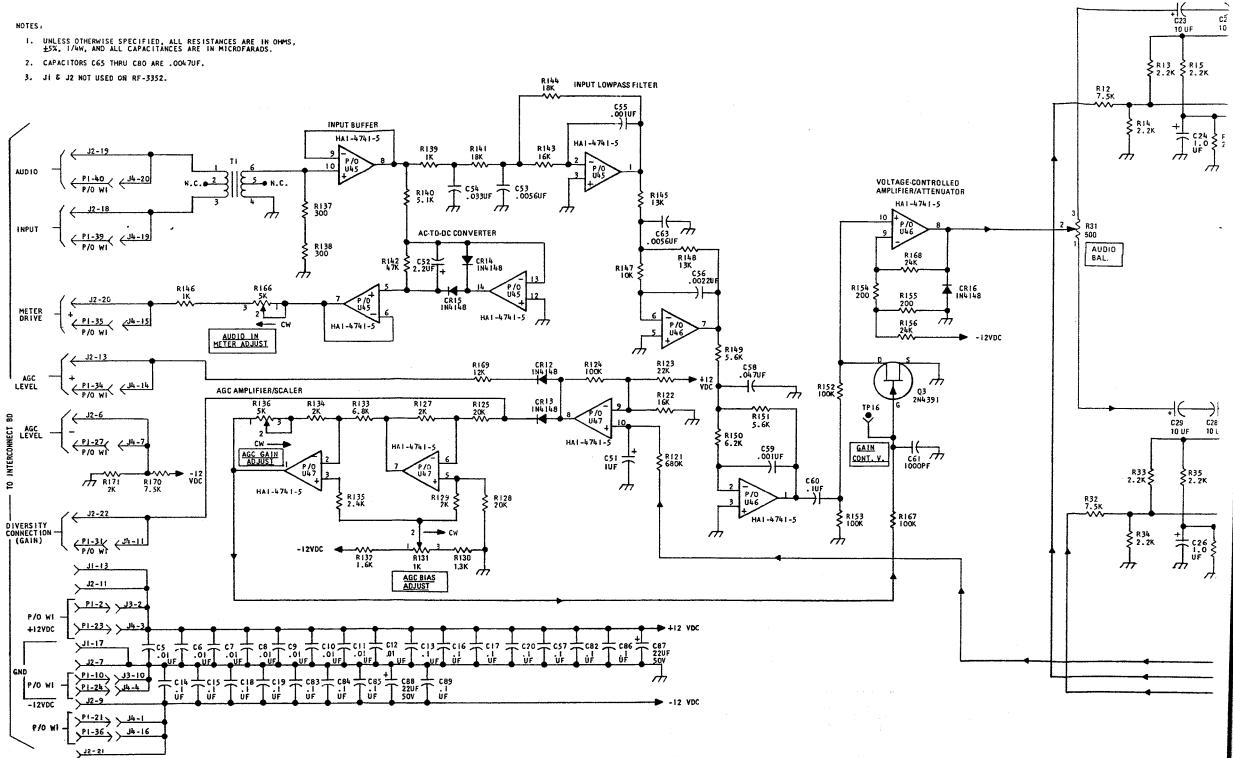

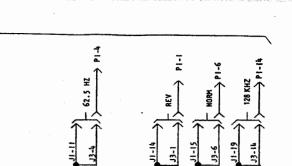

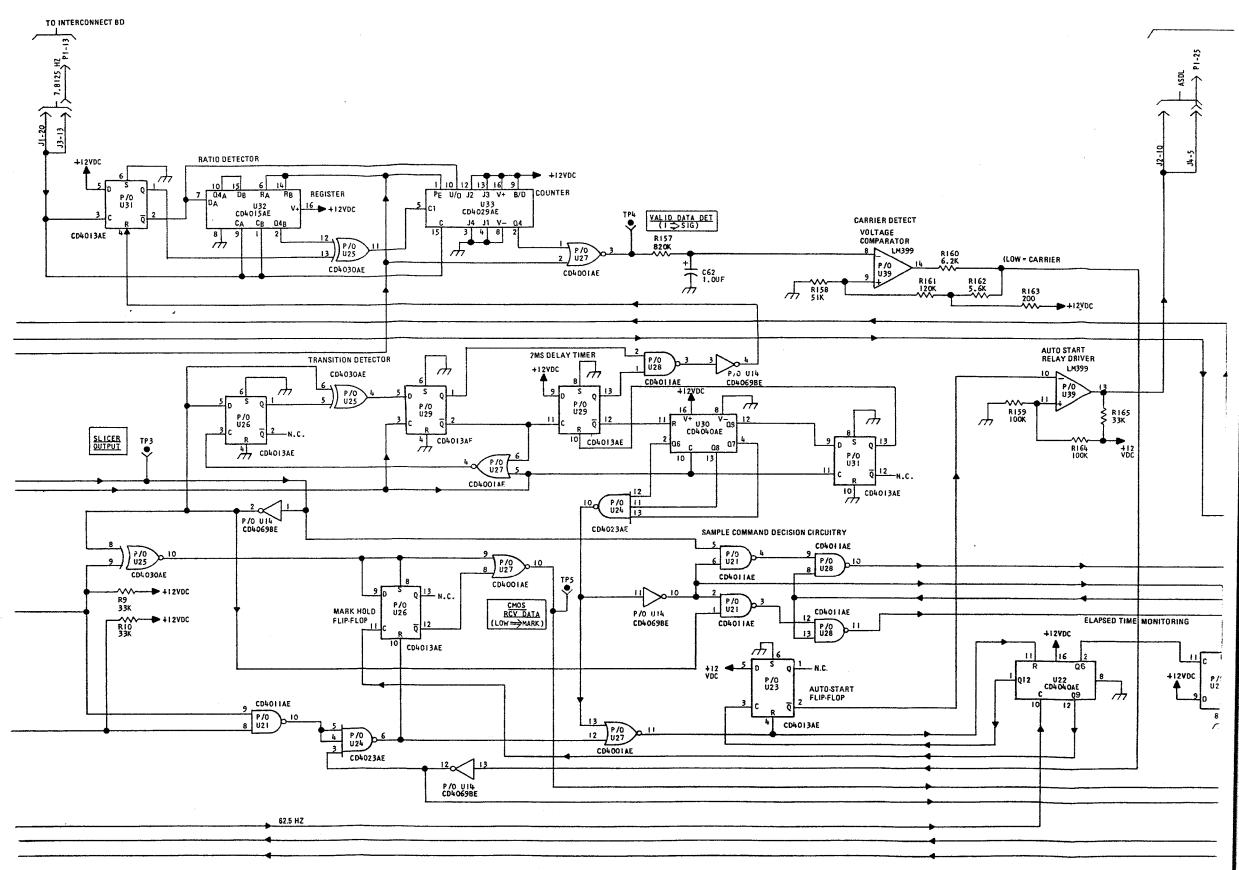

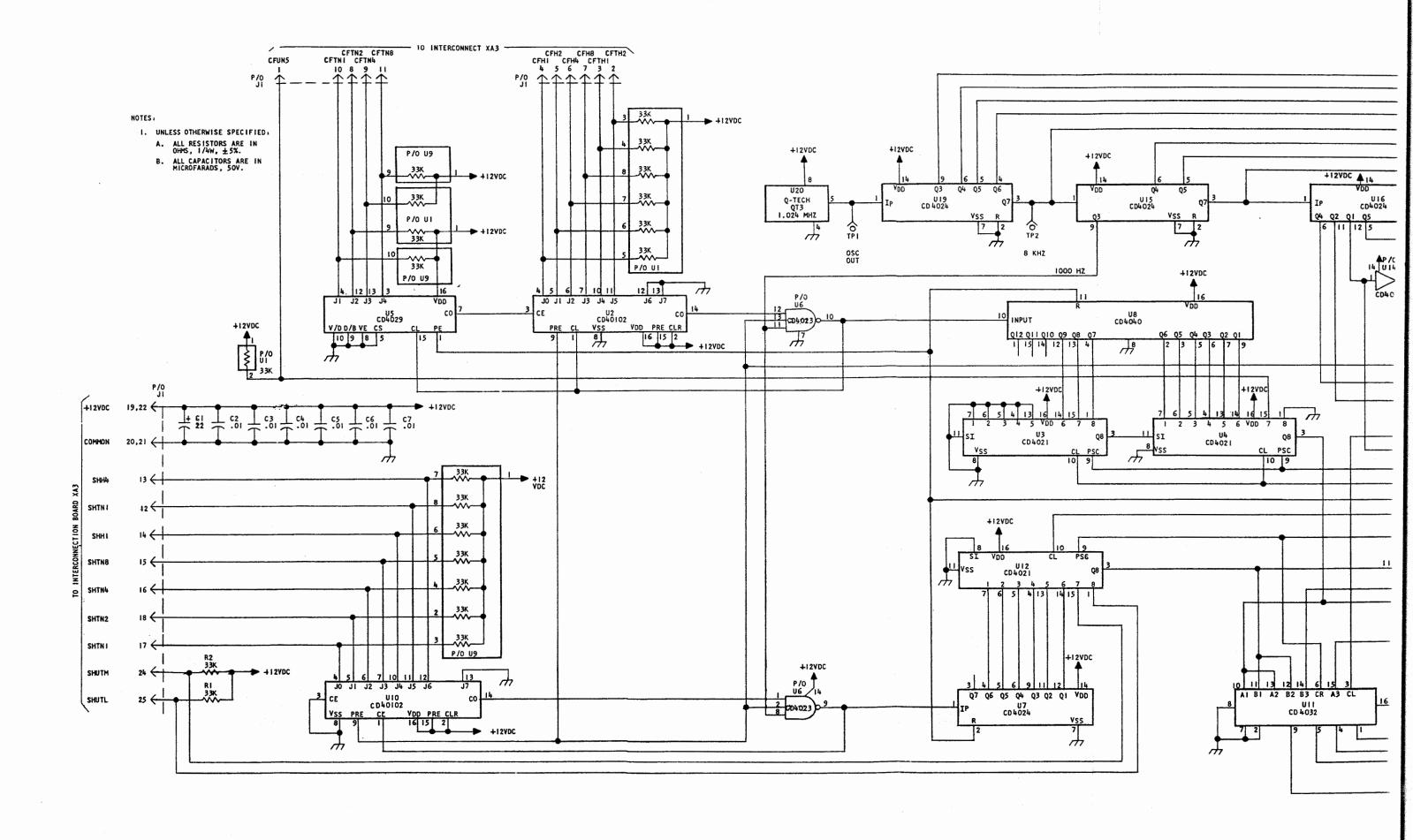

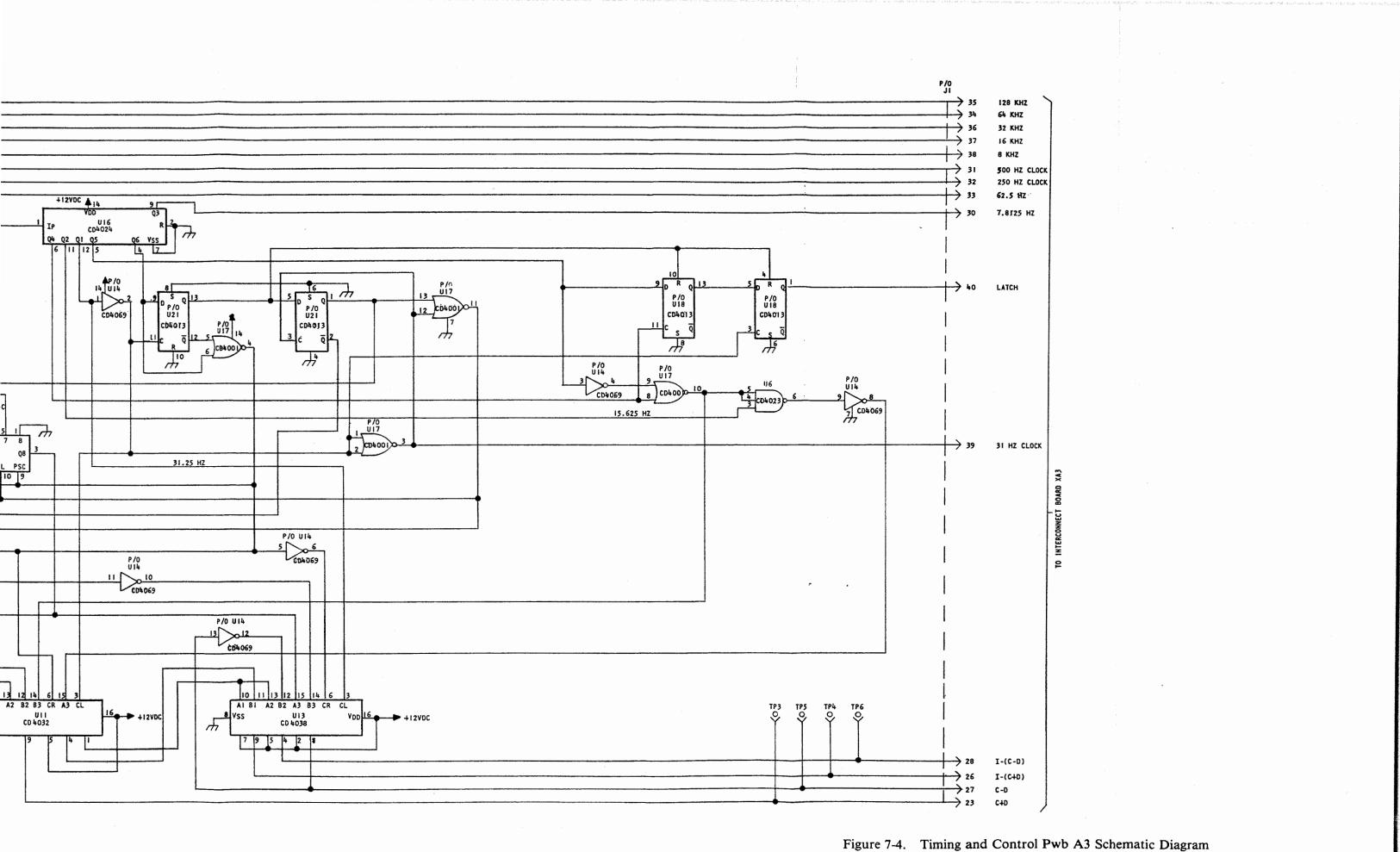

| 7-4        | Timing and Control Pwb A3 Schematic Diagram                                          |

| 7-5        | Interface Pwb A4 Schematic Diagram                                                   |

| 7-6        | Transistor/Regulator Pwb A5 Schematic Diagram                                        |

| 7-7        | Control and Indicator Pwb A6 Schematic Diagram                                       |

| 7-8        | Frequency Control Board Assembly A7 Schematic Diagram                                |

| 7-9        | Power Supply Pwb PS1 Schematic Diagram                                               |

| 7-10       | Interconnection Pwb W1 Schematic Diagram                                             |

# LIST OF TABLES

#### Table

| 1-1          | RF-3352 FSK Terminal Technical Characteristics.                                     | 1-1  |

|--------------|-------------------------------------------------------------------------------------|------|

| 2-1          | Accessories Shipped with the RF-3352 FSK Terminal                                   | 2-5  |

| 3-1          | RF-3352 FSK Terminal - External Connector, Control, Indicator, and Switch Functions | 3-4  |

| 4-1          | Modulator Pwb A1 Control Logic Truth Table                                          | 4-7  |

| 4-2          | Demodulator Pwb A2 Functional Circuit Component Identification                      |      |

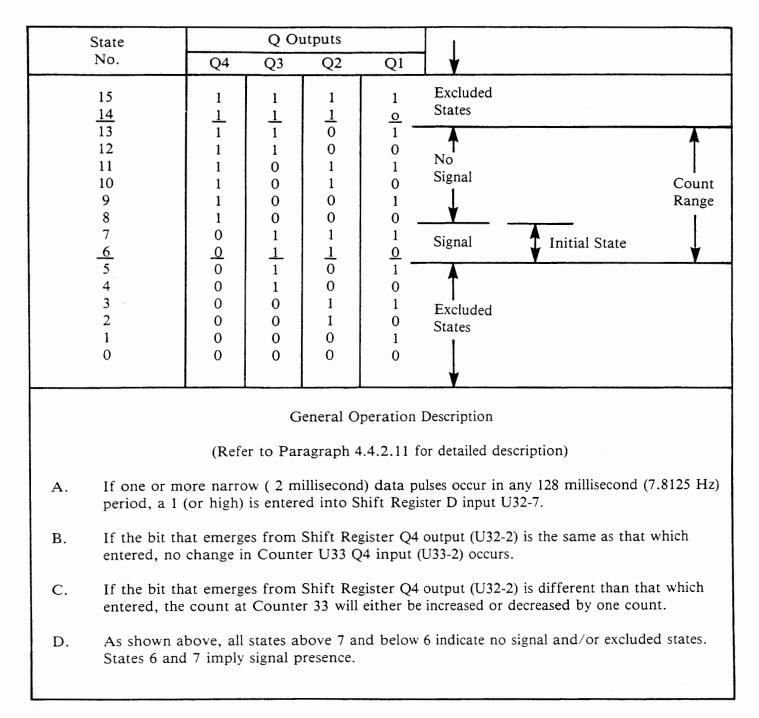

| 4-3          | Operation of Shift Register A2U32/Counter A2U33.                                    |      |

| 5-1          | A1TP1 - Modulator 200X MARK TONE Test Point Typical Data.                           |      |

| 5-2          | A1TP2 - Modulator 200X SPACE TONE Test Point Typical Data                           |      |

| 5-3          | A1TP3 - Modulator TX DATA Test Point Typical Data                                   |      |

| 5-4          | A1TP4 - Modulator CMOS SEND Test Point Typical Data                                 | 5-28 |

| 5-5          | A1TP5 - Modulator 200X AUDIO OUTPUT Test Point Typical Data -<br>Measurement No. 1  | 5-29 |

| 5-6          | A1TP5 - Modulator 200X AUDIO OUTPUT Test Point Typical Data -                       |      |

|              | Measurement No. 2                                                                   | 5-30 |

| 5-7          | A1TP5 - Modulator 200X audio output Test Point Typical Data -                       |      |

|              | Measurement No. 3.                                                                  | 5-31 |

| 5-8          | A1TP5 - Modulator 200X AUDIO OUTPUT Test Point Typical Data -                       | c    |

| • •          | Measurement No. 4.                                                                  | 5-32 |

| 5-9          | A1TP5 - Modulator 200X AUDIO OUTPUT Test Point Typical Data -                       | 6 22 |

| <b>-</b> • • | Measurement No. 5.                                                                  | 5-33 |

| 5-10         | A1TP5 - Modulator 200X AUDIO OUTPUT Test Point Typical Data -                       | 5-34 |

| ~            | Measurement No. 6.                                                                  | 5-34 |

| 5-11         | A1TP6 - Modulator STEP SINUSOID Test Point Typical Data -<br>Measurement No. 1      | 5 25 |

| 5 1 7        | A1TP6 - Modulator STEP SINUSOID Test Point Typical Data -                           | 5-35 |

| 5-12         | Measurement No. 2                                                                   | 5-36 |

| 5-13         | A1TP6 - Modulator STEP SINUSOID Test Point Typical Data -                           | 5-50 |

| 5-15         | Measurement No. 3                                                                   | 5-37 |

| 5-14         | A2TP1 and A2TP2 - Demodulator MARK L.O. FREQ. and SPACE L.O. FREQ. Test             |      |

|              | Points (Respectively) Typical Data                                                  | 5-38 |

| 5-15         | A2TP3 - Demodulator SLICER OUTPUT Test Point Typical Data                           | 5-39 |

| 5-16         | A2TP4 - Demodulator VALID DATA DET. Test Point Typical Data                         | 5-40 |

| 5-17         | A1TP6 - Demodulator CMOS REV DATA Test Point Typical Data                           | 5-41 |

| 5-18         | A2TP6 and A2TP7 - Demodulator MARK MIX OUT. and SPACE MIX OUT Test Points           |      |

|              | (Respectively) Typical Data                                                         | 5-42 |

| 5-19         | A2TP8 - Demodulator SAA Test Point Typical Data                                     |      |

| 5-20         | A2TP9 - Demodulator SPACE BPF OUT Test Point Typical Data                           | 5-44 |

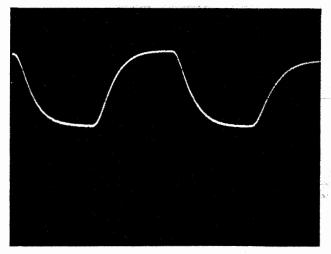

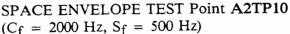

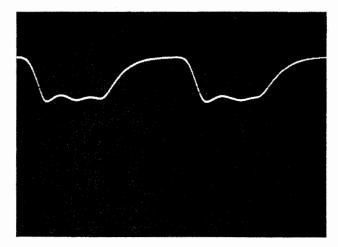

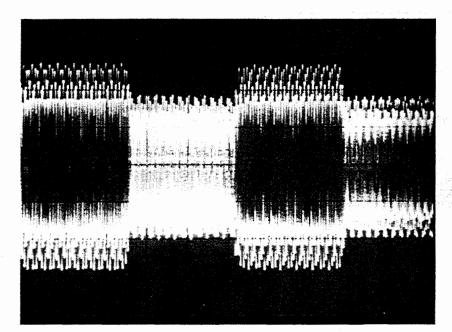

| 5-21         | A2TP10 - Demodulator SPACE ENVELOPE Test Point Typical Data                         | 5-45 |

| 5-22         | A2TP11 - Demodulator MAA Test Point Typical Data                                    | 5-46 |

| 5-23         | A2TP12 - Demodulator MARK BPF OUT Test Point Typical Data                           | 5-47 |

| 5-24         | A2TP13 - Demodulator MARK ENVELOPE Test Point Typical Data                          | 5-48 |

| 5-25         | A2TP14 - Demodulator DECISION LEVEL Test Point Typical Data                         | 5-49 |

| 5-26         | A2TP15 and A2TP16 - Demodulator COMPOSITE ENVELOPE and GAIN Cont. V Test            |      |

|              | Points (Respectively) Typical Data.                                                 | 5-50 |

| 5-27         | A3TP1 - Timing and Control OSC. OUT Test Point Typical Data                         | 5-51 |

| 5-28         | A3TP2 - Timing and Control 8 KHZ Test Point Typical Data                            | 5-52 |

| 5-29         | A3TP3 - Timing and Control C + S Test Point Typical Data                            | 5-53 |

| 5-30         | A3TP4 - Timing and Control I - (C + S) Test Point Typical Data                      | 5-54 |

# LIST OF TABLES (CONT.)

## Table

| 5-31 | A3TP5 - Timing and Control C - S Test Point Typical Data                           | 5-35 |

|------|------------------------------------------------------------------------------------|------|

| 5-32 | A3TP6 - Timing and Control I - (C - S) Test Point Typical Data                     | 5-56 |

| 6-1  | Chassis/Panel Assembly Parts List                                                  | 6-2  |

| 6-2  | Modulator Pwb A1 Parts List                                                        | 6-8  |

| 6-3  | Demodulator Pwb A2 Parts List                                                      |      |

| 6-4  | Timing and Control Pwb A3 Parts List                                               | 6-21 |

| 6-5  | Interface Pwb A4 Parts List                                                        |      |

| 6-6  | Transistor/Regulator Pwb A5 Parts List                                             | 6-26 |

| 6-7  | Control and Indicator Pwb A6 Parts List                                            | 6-28 |

| 6-8  | Frequency Control Board Assembly A7 Parts List                                     | 6-30 |

| 6-9  | Power Supply Pwb PS1 Parts List                                                    |      |

| 6-10 | Interconnection Pwb W1 Parts List                                                  |      |

| 6-11 | Chassis and Panel Wiring Assembly W2 Parts List                                    |      |

| 6-12 | RS-232 Interface Wiring Assembly W3 Parts List                                     | 6-37 |

| 6-13 | Low Level Wiring Assembly W4 Parts List                                            |      |

| 7-1  | RF-3352 FSK Terminal Schematic Diagram List                                        |      |

| 7-2  | Abbreviations and Acronyms Used In The Schematic Diagrams                          | 7-2  |

| 7-3  | Modulator Pwb Assembly A1, PN 6918-1120 Connector Pin, Adjustment Pot., and Test   |      |

|      | Point Reference Data                                                               | 7-3  |

| 7-4  | Demodulator Pwb Assembly A2, PN#18-1130 Connector Pin, Adjustment Pot., and Test   |      |

|      | Point Reference Data                                                               | 7-4  |

| 7-5  | Timing and Control Pwb Assembly A3, PN 6918-1140 Connector Pin and Test Point      |      |

|      | Reference Data                                                                     | 7-7  |

| 7-6  | Interface Pwb Assembly A4, PN 6918-1150 Connector Pin, Adjustment Pot., and Switch |      |

|      | Reference Data                                                                     | 7-8  |

| 7-7  | Transistor/Regulator Pwb Assembly A5, PN 6918-1190 Connector Pin, Adjustment Pot., |      |

|      | and Switch Reference Data                                                          | 7-9  |

| 7-8  | Control and Indicator Pwb Assembly A6, PN6918-1210 Connector Pin, LED, and Switch  |      |

|      | Reference Data                                                                     | 7-10 |

| 7-9  | Reference Data                                                                     |      |

|      | Reference Data                                                                     | 7-11 |

| 7-10 | Power Supply Pwb Assembly PS1, PN 6918-1160 Connector Pin and Fuse Reference Data. | 7-12 |

| 7-11 | Interconnection Pwb Assembly W1, PN 6918-1110 Connector Pin Reference Data         | 7-13 |

| 7-12 | Chassis and Panel Wiring Assembly W2, PN 6918-0110 Connector Pin Reference Data    | 7-20 |

| 7-13 | RS-232 Interface Wiring Assembly W3, PN 6918-0130 Connector Pin Reference Data     |      |

| 7-14 | Low Level Wiring Assembly W4, PN 6918-0140 Connector Pin Reference Data            | 7-22 |

Page

|             |         | HARRIS |

|-------------|---------|--------|

| RF-3352 FSK | RECEIVE |        |

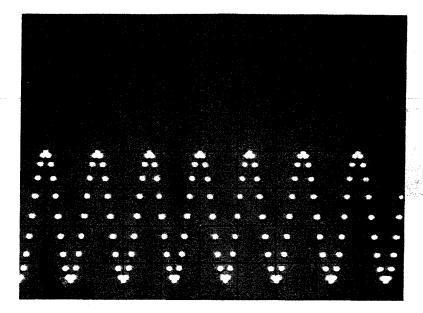

Figure 1-1. Model RF-3352 FSK Terminal

# **SECTION 1**

## INTRODUCTION

#### 1.1 MANUAL SCOPE AND GENERAL DESCRIPTION

This technical publication provides the instructions required to operate and maintain the Model RF-3352 FSK Terminal, Part No. 6918-1100 (see Figure 1-1). This equipment is manufactured by the Harris Corporation, RF Communications Division, 1700 University Avenue, Rochester, New York 14610, United States of America.

The RF-3352 FSK Terminal provides for two-way operation of radio teleprinter equipment over a radio link. The unit contains three major functional sections, a Modulator (Keyer), a Demodulator (Converter), and a data Interface Pwb Assembly.

For modulation, Serial NRZ (No Return Zero) data, in either RS-232 or Current Loop format, is accepted by the Interface Pwb, converted to internal logic levels, and transferred to the Modulator Pwb. The modulator encodes the data into two FSK audio subcarriers which are then transmitted via radio.

The Demodulator Pwb transforms similar FSK subcarriers into a Serial NRZ data stream and, via the Interface Pwb, makes the data available to terminal equipment in either RS-232 or Current Loop format.

The Current Loop Drivers can be operated with either internal or external loop supplies. The internal loop supply output is available at the unit's rear connector.

#### 1.2 TECHNICAL CHARACTERISTICS

Table 1-1 is a list of Technical Characteristics applicable to the RF-3352 FSK Terminal.

#### 1.3 SPARE PARTS KITS AND MOUNTING OPTIONS

Refer to the front of this manual for a listing of spare parts kits and mounting options for the RF-3352 FSK Terminal.

| Teletypewriter Input (Current Loop Receiver) | EIA RS-232C<br>CCITT V.24/V.28<br>20 mA to 80 mA, Neutral<br>20 mA to 60 mA, Polar |

|----------------------------------------------|------------------------------------------------------------------------------------|

| Teletypewriter Output (Current Loop Driver)  | EIA RS-232C<br>CCITT V.24/V.28<br>20 mA to 80 mA Neutral<br>20 mA to 60 mA Polar   |

#### Table 1-1. RF-3352 FSK TERMINAL TECHNICAL CHARACTERISTICS

# Table 1-1. RF-3352 FSK TERMINAL TECHNICAL CHARACTERISTICS (Cont)

| Radio Interface                       | Center Frequency:<br>270 Hz to 3400 Hz in 5 Hz steps<br>Shift Frequency:<br>0 to ±597.5 Hz in ±2.5 Hz steps<br>Stability: Better than 0.1%<br>Level: 0 dBm to -30 dBm, transmit<br>±10 dBm to -40 dBm, receive<br>Impedence: 600 ohms, balanced |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Baud Rate                             | 50 to 150 Baud                                                                                                                                                                                                                                  |

| Clear To Send Delay                   | Continually adjustable over a 0.1 second to 2.5 seconds range. Factory set at 1.0 second.                                                                                                                                                       |

| Traffic Detector Release Time         | Adjustable from 0.4 second to 2.5 seconds following the final data state transmission. Factory set at 1.0 second.                                                                                                                               |

| LED Indicators                        | RECEIVE STATUS—MARK<br>RECEIVE STATUS—SPACE<br>RECEIVE STATUS—SIGNAL<br>TRANSMIT KEYLINE—CLOSED                                                                                                                                                 |

| Tone Selection                        | TONE SELECTION (Hz) CENTER<br>FREQUENCY<br>TONE SELECTION (Hz)—SHIFT                                                                                                                                                                            |

| Meter Functions (Operator Selectable) | LOOP OUT<br>LOOP IN<br>AGC<br>BALANCE<br>AUDIO IN<br>AUDIO OUT                                                                                                                                                                                  |

| Power Requirements                    | 115 VAC/230 VAC ±10%; 47 to 63<br>Hz, Single Phase<br>25 Volt-Amperes                                                                                                                                                                           |

| Operating Temperature                 | Operation:<br>O°C to 50°C (32°F to 122°F)<br>Storage:<br>30°C to 70°C (75.6 to 158°F                                                                                                                                                            |

| Physical Dimensions                   | 8.9 cm H x 48.3 cm W x 47 cm D<br>(3.5 in. H x 19 in. W x 18.5 in. D)                                                                                                                                                                           |

| Weight                                | 6.8 kg (15 lb.)                                                                                                                                                                                                                                 |

|                                       |                                                                                                                                                                                                                                                 |

Table 1-1. RF-3352 FSK TERMINAL TECHNICAL CHARACTERISTICS (Cont.)

| Additional Characteristics | Reverse Sensing                                                       |

|----------------------------|-----------------------------------------------------------------------|

|                            | RS-232 Override (permits RS-232 data<br>entry without full handshake) |

|                            | Auto-start (                                                          |

|                            | Auto-start Override                                                   |

|                            | Traffic Detector                                                      |

|                            | Diversity Combining                                                   |

|                            | Full RS-232C Protocol                                                 |

|                            |                                                                       |

|                            |                                                                       |

## **SECTION 2**

#### INSTALLATION

#### 2.1 INTRODUCTION

This section contains installation, electrical interconnection, emergency shutdown and adjustment instructions for the RF-3352 FSK Terminal.

#### 2.2 UNPACKING AND INSPECTION INSTRUCTIONS

No special unpacking instructions apply. Make sure that the accessories shipped with the terminal are present and accounted for (refer to Table 2-1 for a list of the accessories). Inspect equipment for damage incurred during shipment. Report damage to nearest responsible authority for disposition.

#### 2.3 MECHANICAL INSTALLATION/REPLACEMENT OF DAMAGED ASSEMBLIES

No special installation instructions apply. In the event that any of the terminals assemblies have to be replaced, refer to the applicable area of Section 5 of this manual.

#### 2.4 RF-3352 FSK TERMINAL ELECTRICAL INTERCONNECTION

#### NOTE

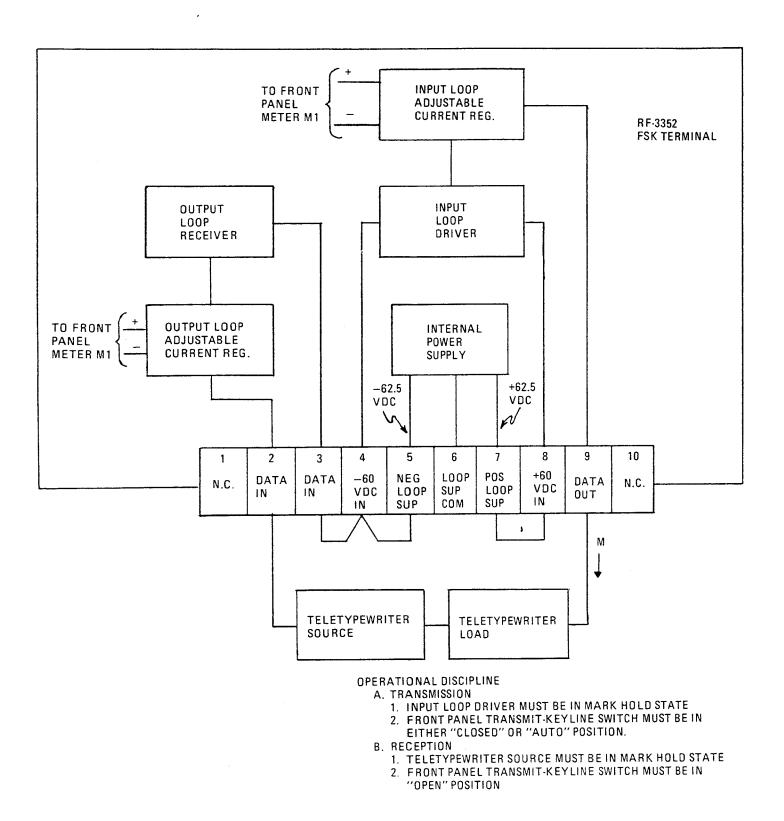

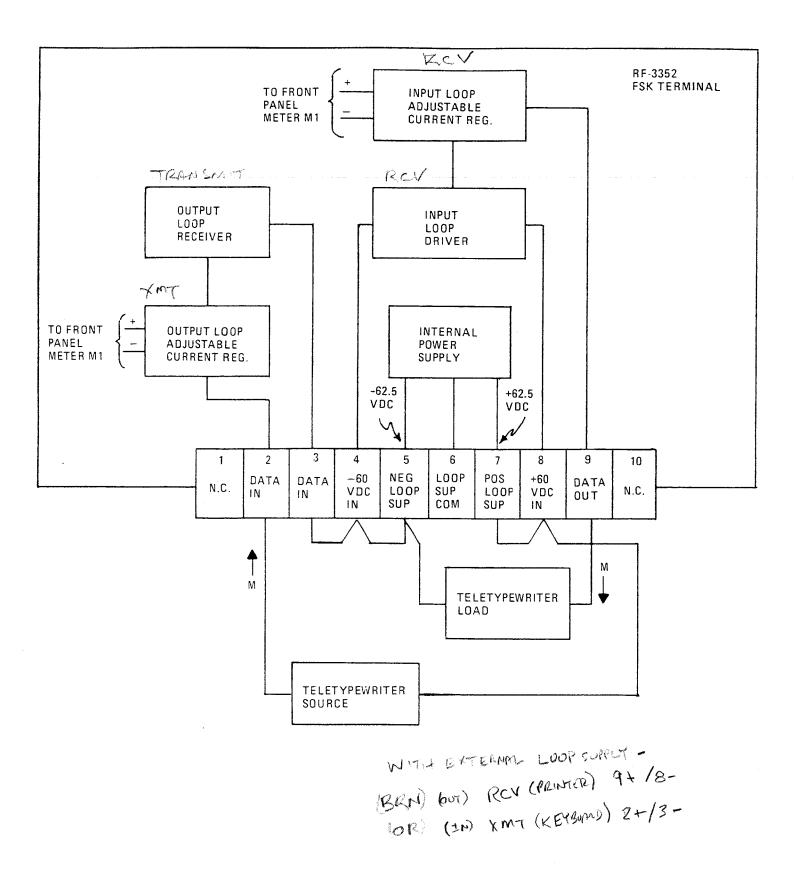

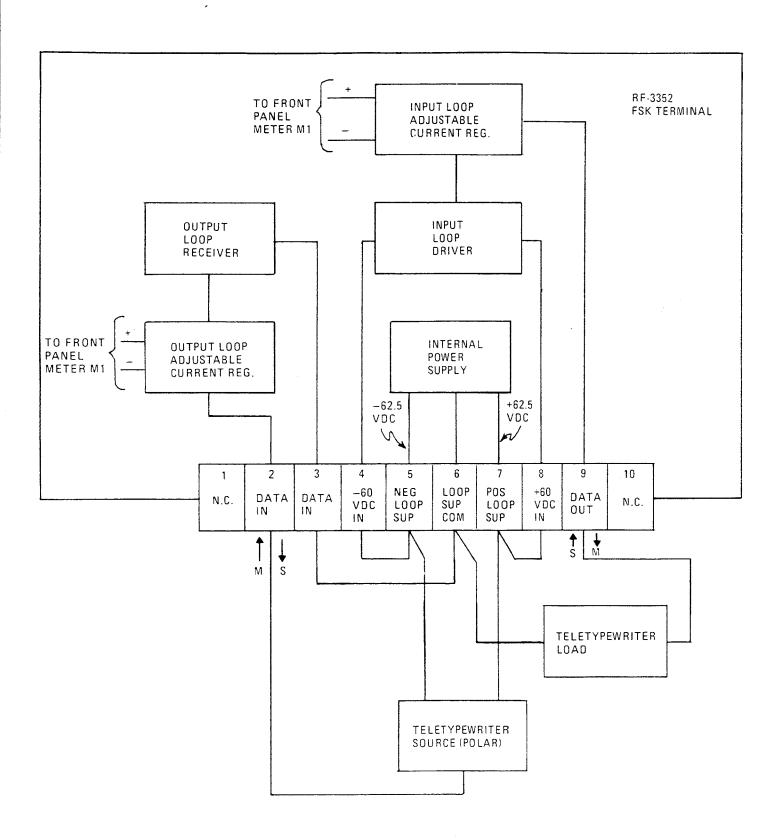

Figures 2-1 through 2-3 comprise various interconnection diagrams. In each illustration, the interconnection is shown using the FSK Terminal's internal loop supply. Since this supply is connected to the terminal's driver and receiver circuits only via external connection. External loop power supplies may be substituted if desired.

Figure 2-1 shows the RF-3352 FSK Terminal interconnection and operational discipline for Neutral Mode-Common Loop (Half Duplex) operation. The operational discipline given must be complied with to ensure proper operation in this mode.

Figure 2-2 shows the RF-3352 FSK Terminal interconnection for Neutral Mode - Independent Loop (Full Duplex) operation.

Figure 2-3 shows the RF-3352 FSK Terminal interconnection for Polar Mode - Independent Loop (Full Duplex) operation.

Figure 2-1. RF-3352 FSK Terminal/Teletypewriter Interconnection and Operational Discipline - Neutral Mode - Common Loop (Half Duplex)

Figure 2-2. RF-3352 FSK Terminal/Teletypewriter Interconnection -Neutral Mode - Independent Loops (Full Duplex)

2-4

#### Table 2-1. Accessories Shipped with the RF-3352 FSK Terminal

| Item<br>No.                                                                                                                                                                                                              | Qty.                        | Part No.                                                                                                         | Name                                                                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                                                                                                                                          | 1<br>1<br>15<br>2<br>1<br>1 | 724-0029<br>J22-0001-001<br>J22-0001-002<br>E60-0001-001<br>K55-0010-003<br>MS 3106A - 10SL - 35<br>MS 3057 - 4B | AC Power Cord<br>RS-232 Connector<br>Low Level Connector<br>Solderless Terminals<br>Connector Clamps<br>Auto-Start Connector<br>Connector Clamp |  |  |  |  |

| NOTE: Model RF-3352 FSK Terminal, ordered as Part No. 6918-0010, includes<br>RF-3352 FSK Terminal Part No. 6918-1100, Accessory Kit Part No.6918-0020<br>and RF-3352 FSK Terminal Instruction Manual Part No. 6918-0100. |                             |                                                                                                                  |                                                                                                                                                 |  |  |  |  |

#### (Accessory Kit Part No. 6918-0020)

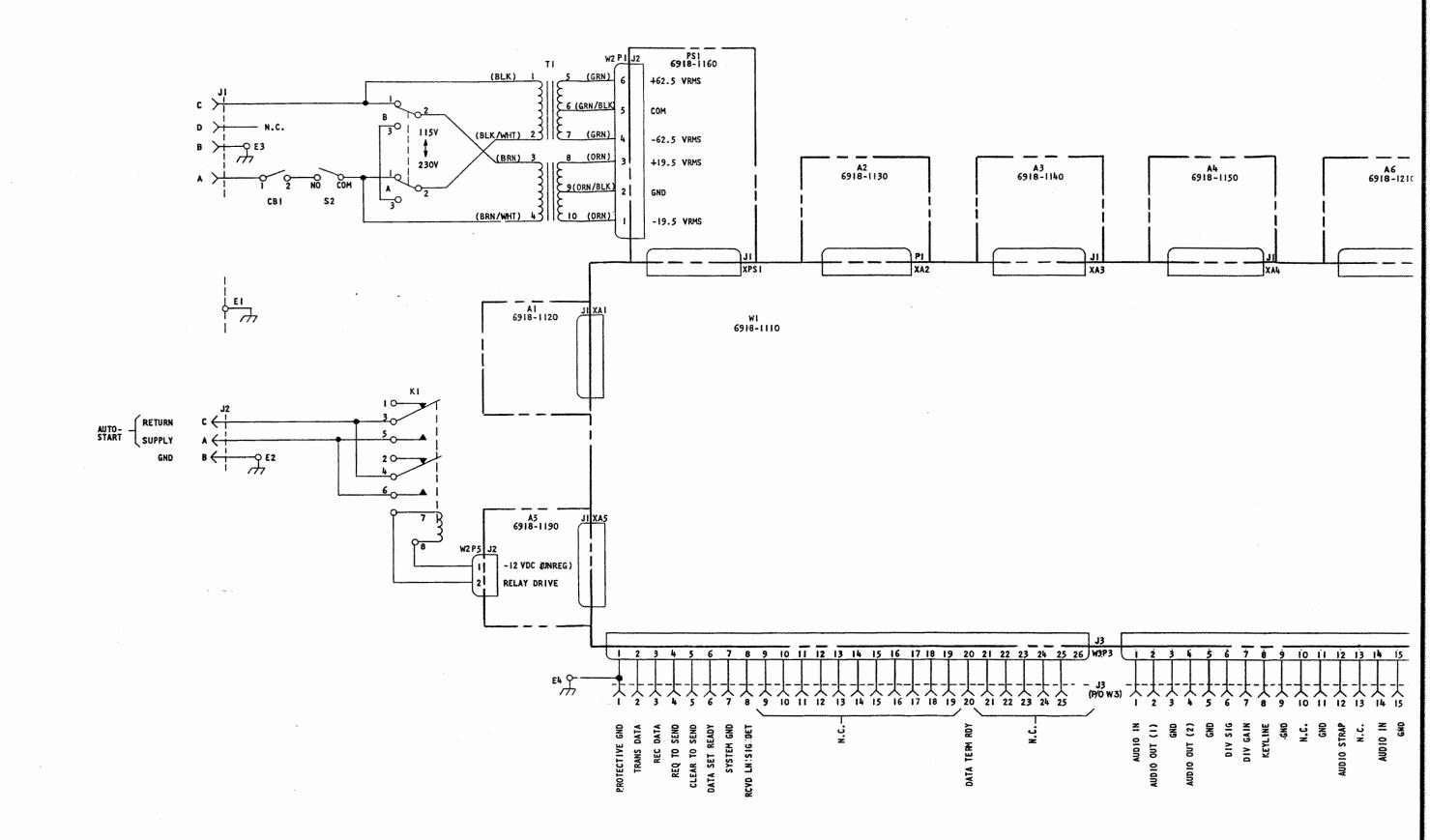

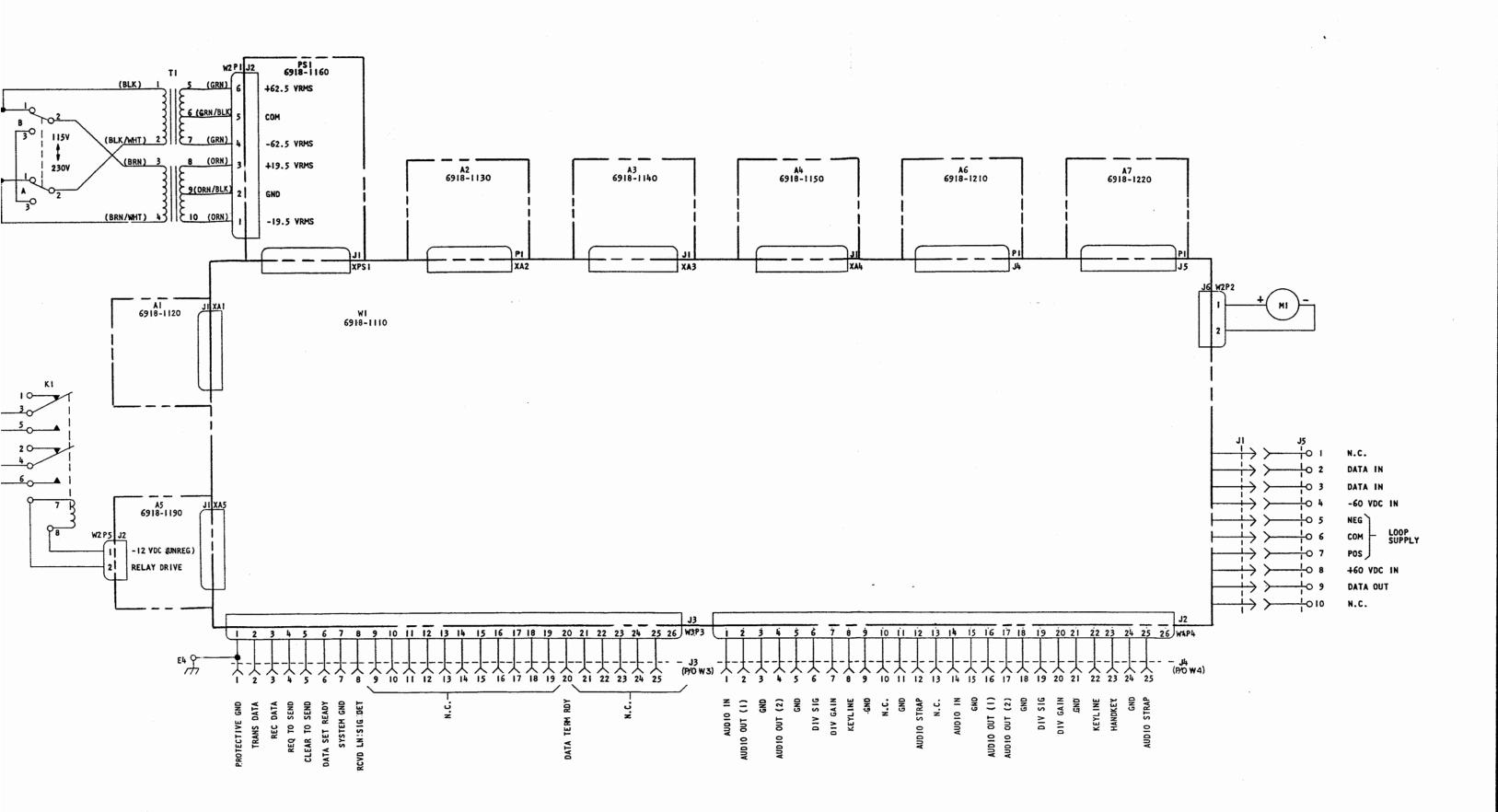

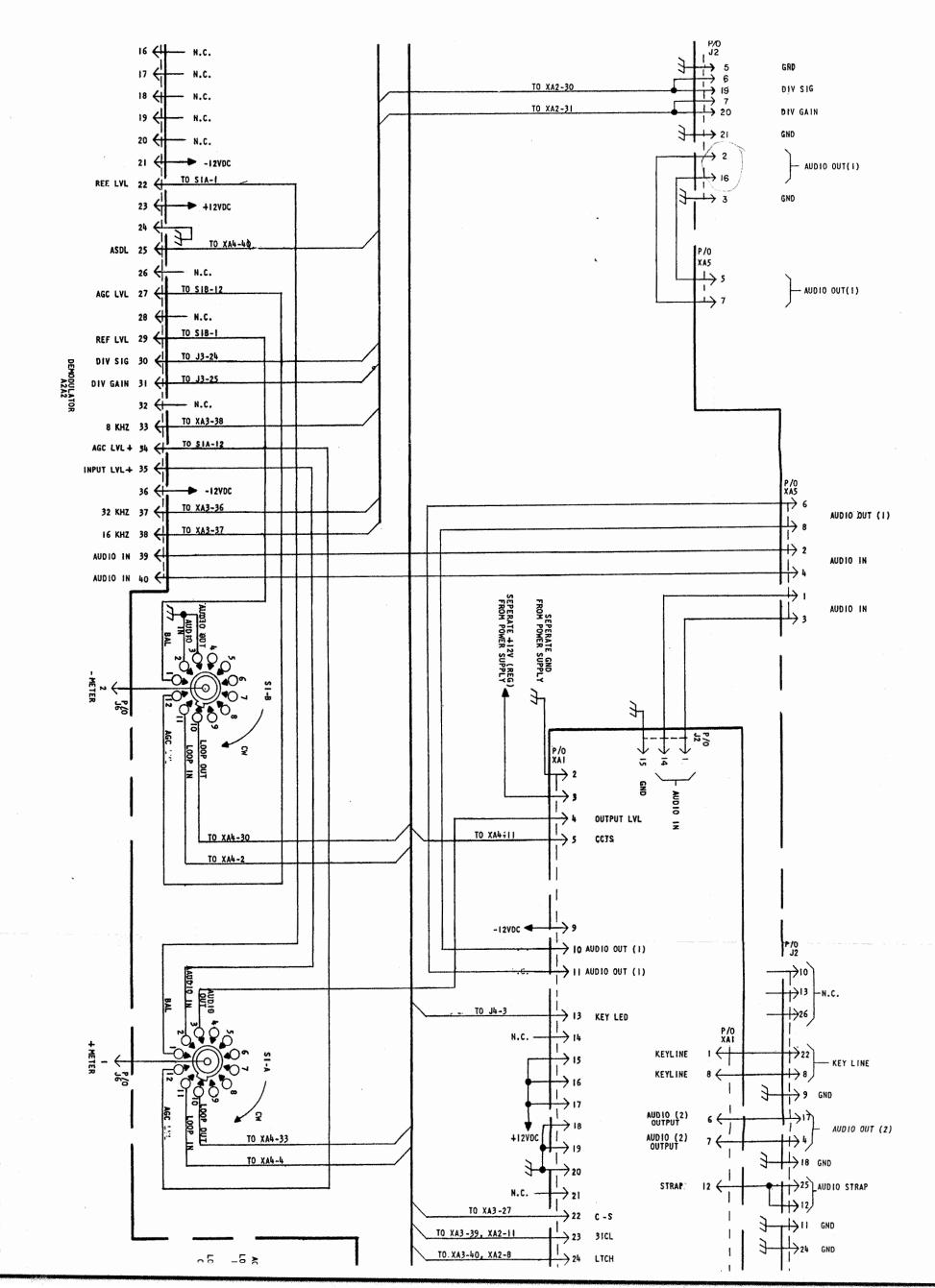

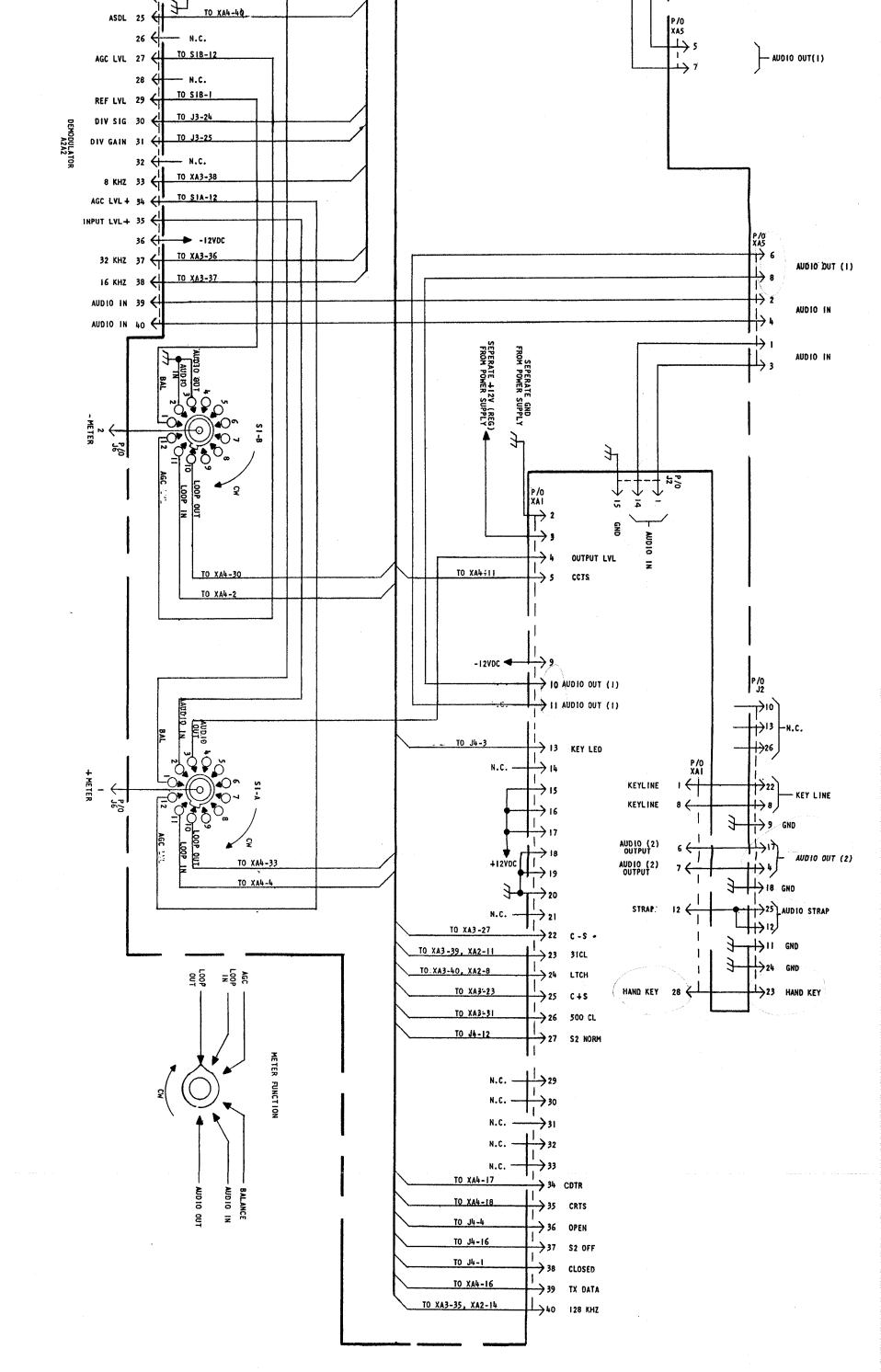

Figure 2-4 shows the RF-3352 FSK Terminal internal interconnection of the unit's assemblies and major components. The identity of assembly connectors and the function of all rear panel connector pins is given.

Examine Input/Output Connector W4J4 in Figure 2-4. Note that there are two sets of audio input and audio output, diversity signal, and diversity gain connections. This scheme allows the connection of two or more equipments to the terminal (this scheme is sometimes referred to as "daisy-chaining"). Provision for a hand key input (W4J4-23) is also provided. An audio strapping capability (the linear combination of two audio signals - one superimposed on the other) is also provided (at W4J4-12 and -25).

#### 2.4.1 PRIMARY POWER SELECTION

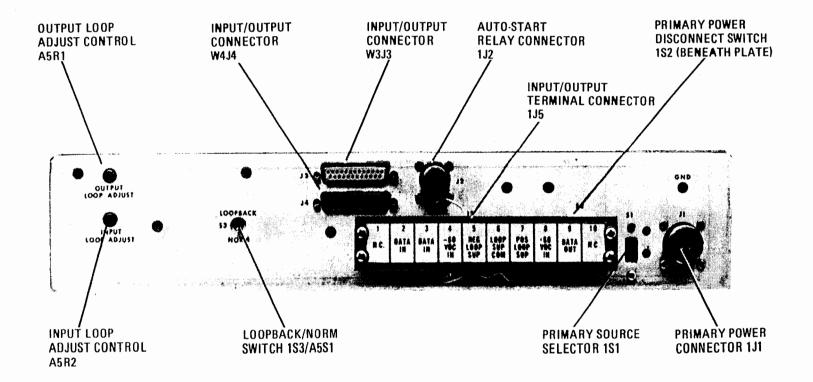

Either 115 Vac or 230 Vac may be selected by placing the rear panel Primary Power Selector (1S1, Figure 3-2) in the desired position.

#### 2.4.2 EMERGENCY SHUTDOWN INSTRUCTIONS

In an emergency, place the front panel power ON/OFF Circuit Breaker (1CB1, Figure 3-1) in OFF position. Disconnect primary power.

#### 2.5 INITIAL POSITION OF CONTROLS AND SWITCHES

The following is the suggested initial position of controls and switches, and is to be used as a guide prior to applying power to the terminal. Individual control and switch positions may vary from this guide as individual system requirements dictate. Refer to Figures 3-1 and 3-2 for control and switch locations.

#### NOTE

If Neutral Mode - Common Loop (Half Duplex) is to be used, refer to the operational discipline in Figure 2-1.

TRANSMIT-KEYLINE CLOSED/AUTO/OPEN Switch A6S1: CLOSED

TRANSMIT-SENSE-NORM/REV/OFF Switch A6S2: NORM

RECEIVE-SENSE-NORM/MARK HOLD/REV Switch A6S3: NORM

TONE SELECTION (Hz)-CENTER FREQUENCY Switch Selection (A7S1): To desired center frequency

TONE SELECTION (Hz)-SHIFT FREQUENCY Switch Section (A7S1): To Desired shift frequency

METER FUNCTION Selector W1S1: AUDIO IN

Rear Panel Primary Power Selector Switch 1S1: To applicable primary power source

Rear Panel LOOPBACK/NORM Switch 1S3/A5S: NORM

#### 2.6 LOOP CURRENT ADJUSTMENTS

The input and output loop currents can be adjusted between 20mA and 60 mA (Polar Mode) or 20 mA and 80 mA (Neutral Mode) in the following manner: Place METER FUNCTION Selector W1S1 in either LOOP IN or LOOP OUT position and adjust either INPUT LOOP ADJUST Control A5R2 or OUTPUT LOOP ADJUST Control A5R1, respectively, to obtain the desired loop current. (Refer to Figures 3-1 and 3-2 for selector and control locations.)

#### NOTE

To avoid reading errors caused by the averaging effect of the meter movement (for example, Mark/Space data in Neutral Mode), it is recommended that loop currents be adjusted while constant current is flowing (when terminal is in Mark Hold).

#### 2.7 OPERATIONAL ADJUSTMENTS

Certain adjustments that allow the terminal to be operated in accordance with specific user requirements can be accomplished. The following defines the applicable control nomenclature and adjustment characteristics. The location of these controls is shown in Figures 5- through 5-.

a. Receiver Loop NEUTRAL/POLAR Switch A4S1 — Place this switch in the desired position.

b. PSDTR (Pseudo Data Terminal Ready) Switch A4S2 — Allows data to be input at RS-232 levels without going through the RS-232 protocol. Place switch in desired position.

#### NOTE

The PSDTR Switch will override the current loops. Make sure switch is at the proper position prior to energizing unit.

- c. AS OVERRIDE Switch A4S3 Placing this switch ON causes the Auto-Start Relay to remain closed.

- d. IDLE SELECT Switch A1S1 Allows the terminals output to be a Mark Tone (high or low, depending on the setting of the front panel TRANSMIT-SENSE-NORM/REV Switch A6S2) or no tone.

- e. TRAF. HOLD TIME Potentiometer A1R30 Adjustable between 0.4 second and 2.5 seconds following the final data state transmission. It is factory set at 1.0 second.

- f. CLEAR TO SEND DELAY Potentiometer A1R32 Adjustable between 0.1 second and 2.5 seconds. It is factory set at 1.0 second.

#### 2.8 REPACKING AND SHIPPING INSTRUCTIONS

If the terminal or any of its subassemblies are to be shipped or returned to the factory, or shipped elsewhere, standard packing instructions for electronic equipment apply. For example, careful wrapping of electronic parts and assemblies and correct marking of containers and applicable destination instructions and codes are all included in standard packing procedures. Follow the instructions of the nearest responsible authority.

.

,

AUDIO IN 1/14 GRN/BLK OUT(1) 2/16 GUT(2) 4/17 RED/BLK KEYLINE 2/22 NO. RCV WH/BLK

Figure 2-4. RF-3352 FSK Terminal Interconnection and Assembly Identification Diagram

2-9/2-10

# SECTION 3

### OPERATION

#### 3.1 INTRODUCTION

This section contains or references the information necessary to operate the RF-3352 FSK Terminal.

# 3.2 FRONT AND REAR PANEL CONNECTOR CONTROL, INDICATOR AND SWITCH LOCATIONS AND FUNCTIONS

Figures 3-1 and 3-2 show the location of all RF-3352 FSK Terminal front and rear panel connectors, controls, indicators and switches. The function of these components is described in Table 3-1.

#### 3.3 OPERATION

The RF-3352 FSK Terminal responds to, and functions in accordance with, signal data applied to it from other system components (such as radio transmitters, receivers, and teletypewriter/teleprinter equipment). The terminal, when interconnected as shown in Figures 2-1 through 2-3, will operate in the manner prescribed. Under normal circumstances, no further adjustment or repositioning of controls will be necessary.

When transmitting or receiving on Upper Sideband (USB), the transmit and receive sensing switches (TRANSMIT-SENSE NORM/REV/OFF Switches A6S2 and RECEIVE-SENSE NORM/MARK HOLD/REV Switch A6S3, respectively) are generally placed in NORM position. When Lower Sideband (LSB) is used, the switches are normally placed in REV position. Intermixing the sensing switch positions may cause a garbled or distorted output at the teletypewriter equipment.

#### 3.4 DETERMINING THE UNKNOWN CENTER AND SHIFT FREQUENCIES

In the event that it is desired to determine unknown center and shift frequencies, the following method can be used.

#### NOTE

The following procedure assumes that the terminal is connected in the link and operating normally.

- a. Refer to Figure 3-1. Place METER FUNCTION Selector W1S1 in AGC position.

- b. While slowly rotating the TONE SELECTION (Hz)-CENTER FREQUENCY Switches A7S1, observe and record the lowest (below zero) and highest (above zero) pointer deflections of the Function Display Meter 1M1. (These points will correspond to  $f_L$  and  $f_H$ , respectively, in subsequent step c.)

3-2

Figure 3-2 RF-3352 FSK Terminal Rear Panel Connectors, Controls, and Switches

3-3

# Table 3-1.RF-3352 FSK TERMINAL - EXTERNAL CONNECTOR, CONTROL,<br/>INDICATOR AND SWITCH FUNCTIONS

.

| (Note: | Refer to | Figure 3-1 | and 3-2 fe | or component | locations.) |

|--------|----------|------------|------------|--------------|-------------|

|--------|----------|------------|------------|--------------|-------------|

| Name and Reference Designator                          | Purpose and/or Function                                                                                                                                                                 |  |  |  |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Front Panel:                                           |                                                                                                                                                                                         |  |  |  |  |

| TRANSMIT-KEYLINE-CLOSED<br>Indicator A6DS1             | Indicates that the system transmitter is operating through the terminal.                                                                                                                |  |  |  |  |

| TRANSMIT-KEYLINE-CLOSED/<br>OPEN/AUTO Switch A6S1      | Allows closing and opening of the transmit path<br>through the terminal; also allows terminal auto<br>matic response to the transmitted signal.                                         |  |  |  |  |

| TRANSMIT-SENSE-NORM/REV/<br>OFF Switch A6S2            | Allows selection of normal or inverted signal transmission; when switch is OFF, allows an audio strapped input to be monitored by the system independent of terminal-generated signals. |  |  |  |  |

| RECEIVE-SENSE-NORM/MARK<br>HOLD/REV Switch A6S3        | Allows selection of normal or inverted signal reception; also allows terminal to be maintained in a steady Mark Hold state.                                                             |  |  |  |  |

| RECEIVE-STATUS-MARK Indicator<br>A6DS3                 | Indicates the presence of a received signal with Mark characteristics.                                                                                                                  |  |  |  |  |

| RECEIVE-STATUS-SPACE Indicator<br>A6DS2                | Indicates the presence of a received signal with Space characteristics.                                                                                                                 |  |  |  |  |

| RECEIVE-STATUS-SIGNAL Indicator<br>A6DS4               | Indicates the presence and terminal decoding of a received signal.                                                                                                                      |  |  |  |  |

| TONE SELECTION (Hz)-CENTER<br>FREQUENCY Switches A7S1  | Allows selection of any center frequency betweer 270 Hz and 3400 Hz.                                                                                                                    |  |  |  |  |

| TONE SELECTION (Hz)-SHIFT Fre-<br>quency Switches A7S1 | Allows selection of any shift frequency between 0.0 Hz and 597.5 Hz.                                                                                                                    |  |  |  |  |

| METER FUNCTION Selector W1S1:                          |                                                                                                                                                                                         |  |  |  |  |

| LOOP OUT Position                                      | Allows Function Display Meter 1M1 to indicate system output loop current.                                                                                                               |  |  |  |  |

| LOOP IN Position                                       | Allows Function Display Meter 1M1 to indicate system input loop current.                                                                                                                |  |  |  |  |

| AGC Position                                           | Allows Function Display Meter 1M1 to indicate the automatic gain control voltage level.                                                                                                 |  |  |  |  |

# Table 3-1.RF-3352 FSK TERMINAL EXTERNAL CONNECTOR, CONTROL,<br/>INDICATOR AND SWITCH FUNCTIONS (Cont.)

(Note: Refer to Figures 3-1 and 3-2 for component locations.)

| Name and Reference Designator                                              | Purpose and/or Function                                                                                                         |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Front Panel (Cont.)                                                        |                                                                                                                                 |

| BALANCE Position                                                           | Allows Function Display Meter 1M1 to indicate<br>the amplitude and polarity of the demodulator<br>threshold (reference) signal. |

| AUDIO IN Position                                                          | Allows Function Display Meter 1M1 to indicate the strength of the received audio input signal.                                  |

| METER FUNCTION Selector W1S1: (cont.)                                      |                                                                                                                                 |

| AUDIO OUT Position                                                         | Allows Function Display Meter 1M1 to indicate the strength of the terminals audio output signal.                                |

| Function Display Meter 1M1                                                 | Indicates the function selected by METER<br>FUNCTION Selector W1S1. Meter dial indicates<br>0 to 106 mA and -10dB to +3dB.      |

| ON/OFF Circuit Breaker 1CB1                                                | Allows application of primary power to the terminal.                                                                            |

| Rear Panel:                                                                |                                                                                                                                 |

| OUTPUT LOOP ADJUST Control<br>A5R1                                         | Allows adjustment of the output loop current to the desired level.                                                              |

| INPUT LOOP ADJUST Control A5R2                                             | Allows adjustment of the input loop current to the desired level.                                                               |

| LOOPBACK/NORM Switch 1S3/A5S1                                              | Allows evaluation of system components independent of the influence of the radio link.                                          |

| Input/Output Connectors W3J3 and W4J4; Input/Output Terminal Connector 1J5 | Allows terminal functional connections to and from system components.                                                           |

| Auto-start Relay Connector 1J2                                             | Allows system connection to Auto-start Relay 1K1.                                                                               |

| Primary Power Selector 1S1                                                 | Allows selection of either 115 Vac or 230 Vac primary power.                                                                    |

| Primary Power Connector 1J1                                                | Allows connection of primary power source to terminal.                                                                          |

c. Find the unknown center frequency  $(f_c)$  and shift frequency  $f_s$ ) using the method described in the following example:

Example:

$f_L$  (from step b) = 1020 Hz

$f_H$  (from step b) = 1580 Hz

$f_c = Unknown$  Center Frequency

$f_s = Unknown Shift Frequency$

$$f_c = f_L + \frac{f_h}{2} = \frac{1020 \text{ Hz} + 1580 \text{ Hz}}{2} = 1300 \text{ Hz}$$

$f_{S} = f_{h} - f_{c} = 1580 \text{ Hz} - 1300 \text{ Hz} = 280 \text{ Hz}$

also  $f_s = f_c - f_1 = 1300 \text{ Hz} - 1020 \text{ Hz} = 280 \text{ Hz}$

- d. Set TONE SELECTION (Hz) CENTER FREQUENCY Switches A7S1 to 1300 Hz

- e. Set TONE SELECTION (Hz) SHIFT FREQUENCY Switches A7S1 to  $\pm$  280 Hz.

# 3.5 DETERMINING THE UNKNOWN CENTER FREQUENCY WHEN THE SHIFT IS KNOWN

In the event that it is desired to determine an unknown center frequency when the shift frequency is known, the following method can be used.

NOTE

The following procedure assumes that the terminal is connected in the link and operating normally.

- a. Refer to Figure 3-1. Place METER FUNCTION Selector W1S1 in AGC position.

- b. Set TONE SELECTION (Hz) SHIFT Frequency Switches A7S1 to the known shift frequency.

- c. While slowly routing the TONE SELECTION (Hz) CENTER FREQUENCY Switches A7S1, observe the pointer defective on Function Display Meter 1M1. At the first point of maximum pointer defective (either above or below zero), place METER FUNCTION Selector W1S1 in BALANCE position and observe the meter pointer. If the pointer displays an average deflection significantly to the right or left of zero, the frequency indicated by the center frequency switches is incorrect. If the pointer deflection is centered near zero, the set center frequency is the correct center frequency.

#### 3.6 LOOP CURRENT ADJUSTMENT

Refer to paragraph 2.6 for the input and output loop current adjustment procedure.

#### 3.7 EMERGENCY SHUTDOWN INSTRUCTIONS

In an emergency, place the front panel power ON/OFF Circuit Breaker (1CB1, Figure 3-1 in OFF position. Disconnect primary power.

# **SECTION 4**

## THEORY OF OPERATION

#### 4.1 INTRODUCTION

The RF-3352 FSK Terminal comprises Modulator Pwb A1, Demodulator Pwb A2, Timing and Control Pwb A3, Interface Pwb A4, Transistor Regulator Pwb A5, Control and Indicator Pwb A6, Frequency Control Board Assembly A7, and Power Supply Pwb PS1. These major assemblies are electrically connected to or interconnected by Interconnection Pwb W1, Chassis and Panel Wiring Assembly W2, RS-232 Interface Wiring Assembly W3, and Low Level Wiring Assembly W4. The individual and interrelated functions of these components are described in this section. Refer to Table 7-2, Page 7-4, for a description of the abbreviations and acronyms used in this section.

#### 4.2 OVERALL TERMINAL AND SUBASSEMBLY FUNCTIONAL DESCRIPTIONS

The RF-3352 FSK Terminal is a modern (modulator/demodulator) device that provides for two-way operation of radio teleprinter equipment over a radio link. The Interface Pwb (A4) accepts incoming data, in either RS-232 or Current Loop format, converts it to internal logic levels, and routes it to the Modulator Pwb (A1). The Modulator Pwb (A1) encodes the data into two FSK audio subcarriers, which are in turn transmitted via radio. The Demodulator Pwb (A2) decodes or converts received FSK audio subcarriers into serial NRZ and, via Interface Pwb (A4), makes the data available to teleprinter equipment in either RS-232 or Current Loop format.

The Timing and Control Pwb (A3) processes the frequency selected by the front panel frequency selector switches (Frequency Control Board Assembly A7) that is used by the phase locked loop synthesizers of the Modulator Pwb (A1). Timing and Control Pwb (A3) also provides the timing reference frequencies that are used by the other components of the terminal.

The Interface Pwb (A4) contains the input loop receiver circuitry (loop to CMOS), output loop drivers (CMOS to loop), RS-232 receiver (RS-232 to CMOS), RS-232 driver (CMOS to RS-232) and auto start relay driver circuitry. The current loop drivers can be operated from either the internal loop supply (Power Supply Pwb PS1) or from independent external loop supplies.

The Transistor/Regulator Pwb (A5) contains components whose functions are related to other assemblies of the terminal, but whose heat sinking requirements require a remote mounting (except for NORM/LOOPBACK Switch A5S1/1S3, which is mounted to the pwb to allow rear panel access).

The Control and Indicator Pwb (A6) contains the transmit, receive and keyline sensing switches and condition status indicators.

The Frequency Control Board Assembly (A7) contains the center and shift frequency tone selector switches.

The Power Supply Pwb (PS1) provides the dc voltages and loop current required for terminal component operation and, if required, external teleprinter equipment. The Interconnection Pwb (W1) contains the trace wiring and interconnection receptacles that facilitate signal routing and wiring of the terminal's pwb's, and other components.

Wiring Assemblies W2 through W4 facilitate various signal and voltage routings within the terminal, and provide access to various external equipment via rear panel input/output connectors.

#### 4.3 SIGNAL PATH ROUTING FOR VARIOUS OPERATIONAL STATES

Signal path routings for the various operational states of the terminal are shown in Figures 2-1 through 2-3 and described in detail in Paragraph 4.4.4

#### 4.4 MAJOR ASSEMBLY OPERATIONAL ANALYSES

The following subparagraphs describe the operation of each major assembly, their circuits, and their associated components in detail. Reference to applicable tables, functional diagrams, and to the schematic diagrams of Section 7 is made throughout.

#### 4.4.1 MODULATOR PWB ASSEMBLY A1 OPERATION DESCRIPTION

#### 4.4.1.1 Overall Description

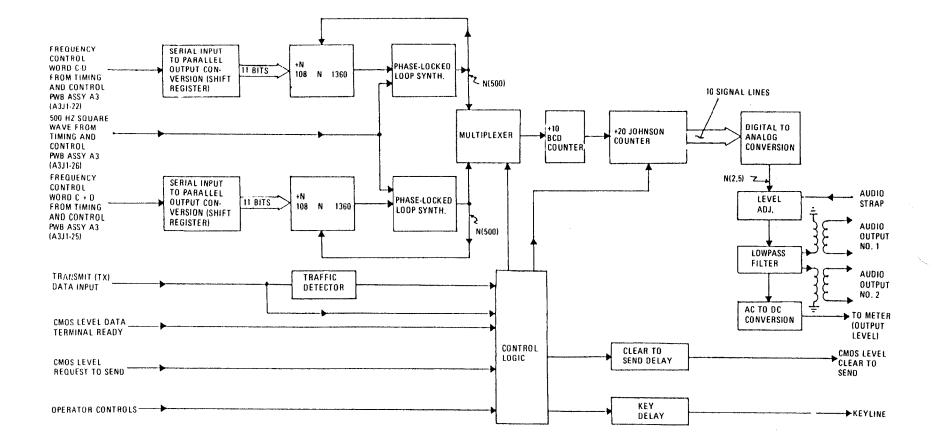

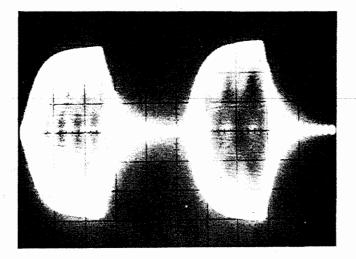

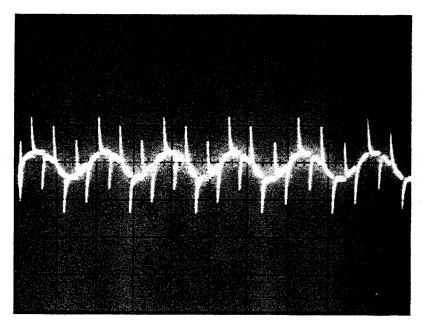

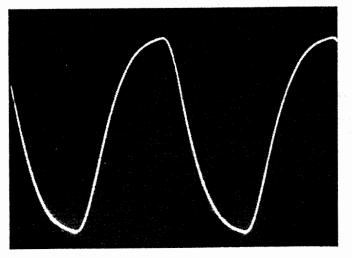

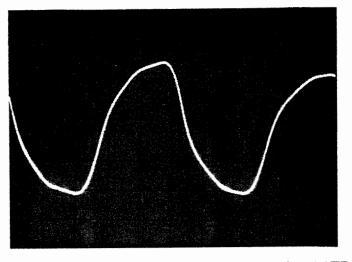

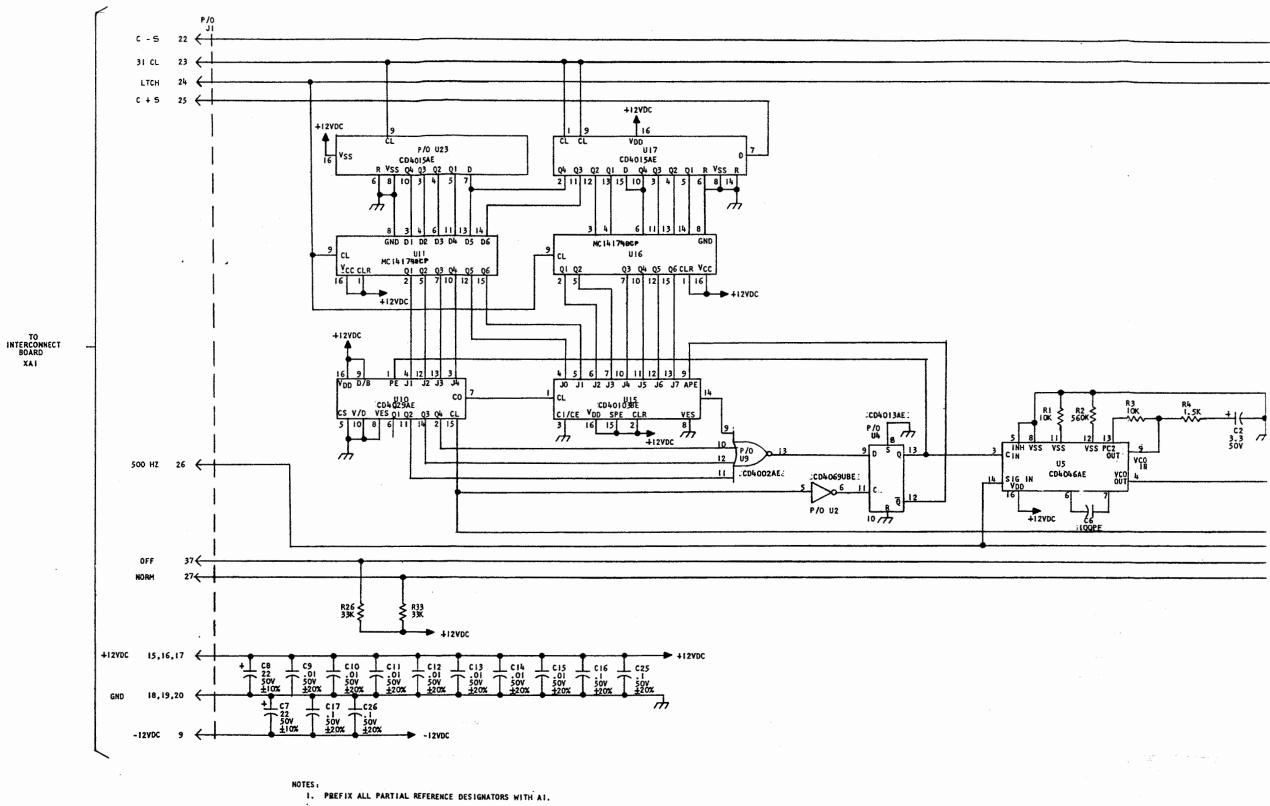

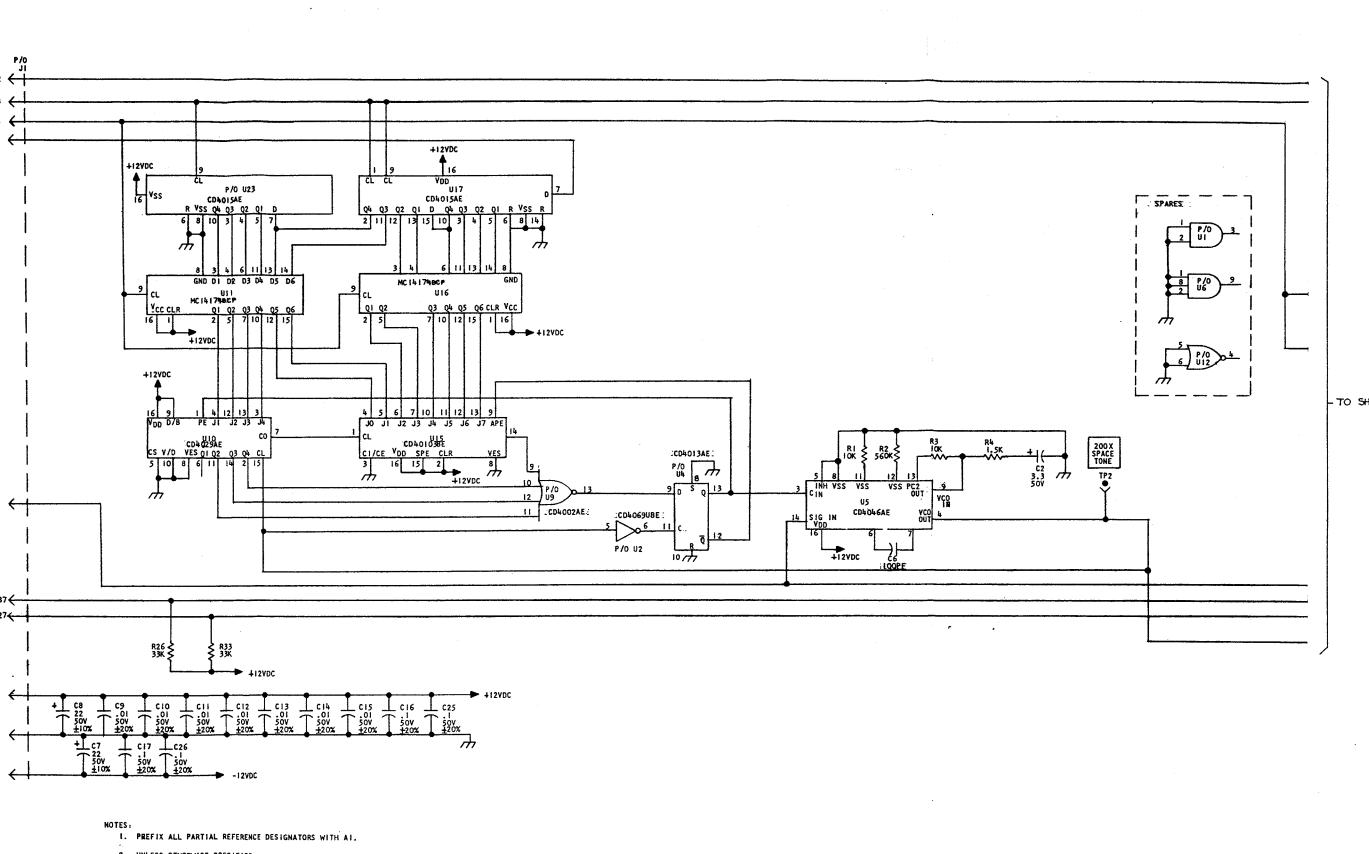

Refer to figure 4-1. Frequency Control Words C-S and C+S (corresponding to the Low and High FSK Tones, respectively) and a 500 Hz square wave input (from Timing and Control Pwb Assembly A3) are applied to two identical Phase-Locked Loop Synthesizers. The synthesizer outputs N (500) are applied to a two-input/one-output Multiplexer. The Multiplexer, controlled by the Control Logic Circuitry, selects one of the synthesizer outputs for subsequent frequency division and conversion to a sinusoid waveform.

The Multiplexer output is applied to a divide-by-200 counter, consisting of the divide-by-10 BCD Counter and divide-by-20 Johnson Counter shown. The counter output, 10 signal lines, is digital-to-analog converted into a 20-step sine wave approximation N (2.5). The sine wave output is level-adjusted, filtered and transformer-coupled, providing two identical audio outputs. The filtered audio is also ac-to-dc converted (rectified) to facilitate terminal front panel meter display and monitoring.

An audio strapping feature is also provided. This allows the linear combination of two or more audio signals.

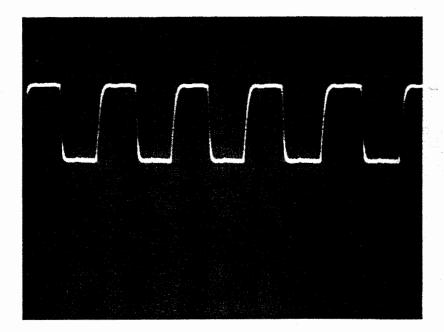

Various operator-controlled and externally-generated signals are combined in the Control Logic Circuitry, allowing operation of the Modulator in a prescribed manner. (The Modulator is capable of operation in accordance with Specification RS-232C requirements, as well as with standard direct teletypewriter interconnections). Automatic keyline closure upon detection of transmitted data, via the Traffic Detection Circuitry, is operator selectable.

In the Normal Mode of terminal operation, the input transmitted data (Tx Data Input) controls the Multiplexer such that a Low tone output corresponds to a Mark level, and a High tone output corresponds to a Space level. In Reverse mode, these relationships are reversed (Low tone corresponds to Space level, High tone corresponds to Mark level). When no transmitted data is present (transmitter is idle), a constant Mark tone will be present. If the operator chooses, the tone may be eliminated.

Figure 4-1. Modulator Pwb Assembly A1 Functional Block Diagram

43

#### 4.4.1.2 Detailed Circuit Description

#### NOTE

#### In the following paragraph, parenthetical references refer to the functionally-identical components of the duplicate circuit, unless indicated otherwise.

The Modulator tone-generating circuits consist of two identical phase-locked frequency synthesizers. Refer to Figure 7-2. These synthesizers comprise phase-locked loop U5 (U3), its associated components, and a presettable down counter. The down counter consists of counters U10 and U15 (U21 and U26), a four-input NOR gate U9-9-10-11-12-13 (U9-2-3-4-5-1), a D-type flip-flop U4-8-9-10-11-12-13 (U4-1-2-3-4-5-6), and an inverter U2-5-6 (U2-1-2).

#### 4.4.1.2.1 Phase-locked Loop Operation

Refer to Figure 7-2. Phase locked loop (U5) (U3) tries to set its input frequency (Pin 4) such that its input frequency (Pin 3) will equal the 500 Hz reference frequency (Pin 14). If the output frequency is divided by an integer (N) to produce the input frequency, and if the input frequency is also equal to the 500 Hz reference frequency applied, the output frequency will equal the reference frequency multiplied by N. Stated symbolically:

If:  $f_{INPUT}$  (Pin 3) =  $\frac{f_{OUTPUT}$  (Pin 4) = f REFERENCE (Pin 14) N

#### Then: fourpur = NxfREFERENCE

N, the required multiplication factor, is provided by a frequency divider (counter) whose input is the square wave at the output of the loop (Pin 4), and whose output frequency equals the reference frequency.

4.4.1.2.2 Divide-by-N Counter Operation

Refer to Figure 7-2. Integrated circuit components U10 and U15 (U21 and U26) comprise a cascaded down counter containing a maximum of 4096 states. Its operation is described in the following sub-paragraphs.

For reference purposes, assume that the counter has just been clocked into State No. 1 at time t = 0. State No. 1 is recognized by NOR Gate U9-9-10-11-12-13 (U9-2-3-4-5-1), which produces a High at the D input of Flip-flop U4 (U4-9 (U4-5). At time T/2 (T being the period of the square wave clock input), U4's Q output U4-13 (U4-1) goes High, forcing the counter into State M. State M is the decimal equivalent of the binary number applied to the counter's Preset (J) inputs.

At the time that the counter is forced into State M (time T/2), Flip-flop U4's D input U4-9 (U4-5) goes Low. Its Q input U4-13 (U4-1) goes Low at time 3T/2. With the forced loading signal now removed, the counter is free to be clocked to State M-1 when timeT2 occurs. At time 3T, the counter will change to State M-2, etc.

In general, the counter state changes to State M - r at time (r + 1)T. Therefore, the counter changes to State No. 1, which is equal to M - (M - 1) at time MT. By making M equal to N, a Divide-by-N counter (modulo) results.

#### 4.4.1.2.3 Binary Number Application to Counter/Latch Operation

Refer to Figure 7-2. The binary numbers that are used to set the counter's division ratio are supplied in a serial bit stream that originates in Timing and Control Pwb A3. In the Modulator, this serial bit stream is applied to a serial input/parallel output shift register U23 and U17 (U23 and U28). The bit stream is shifted into the register by a 31.25 Hz clock. Approximately once each second, when valid data is present at the shift register's parallel outputs, a Latch Pulse is applied to the Clock inputs of Hex D Flip-flops U11 and U16, that is, at U11-9 (U22-9) and U16-9 (U27-9). Thus, the binary number is stored and applied to the Preset (J) inputs of the counter.

#### NOTE

The only time at which C + S or C-S input data is valid is during the half clock cycle occurring immediately before and after the Latch Command. Data either side of this time frame is invalid.

#### 4.4.1.2.4 Synthesizer Output Routing, Divide-By-10 Counter, Divide-By-20 Johnson Counter and Audio Conditioning

The outputs of the two synthesizers are individually selected by the Transmit Data, through the action of NAND Gate U1 (U1-4-5-6; 8-9-10; 11-12-13) and Inverter U2 (U2-3-4). The output is applied to Divide-by-10 Counter U29.

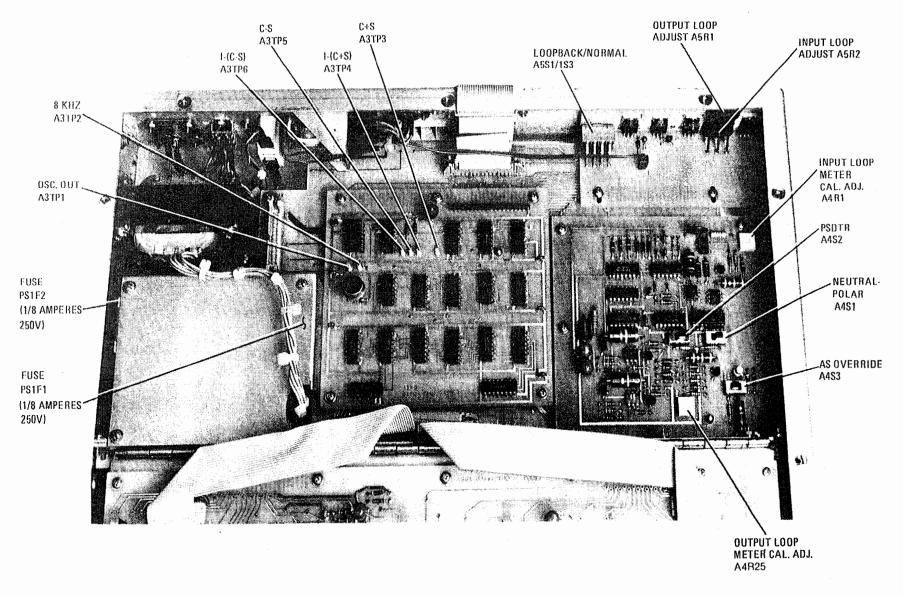

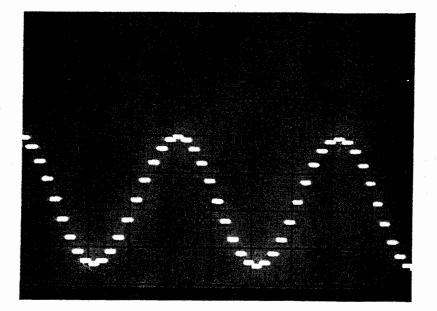

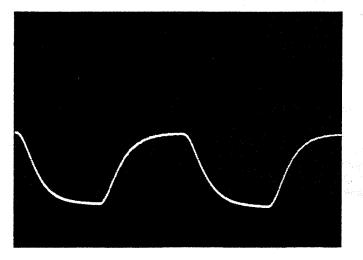

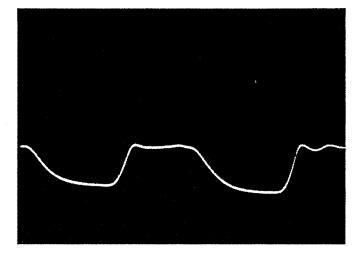

The output of Divide-by-10 Counter U29 is applied to a Divide-by-20 Johnson Counter. This counter consists of Shift Register U25, Flip-flops U24 and U14 (U-14-8-9-10-11-12-13) and NOR Gate U18. Each of the counter's ten output ports supply a square wave at the fundamental tone frequency. Each square wave is shifted by 18° (U18-1-2-3; 4-5-6; -8-9-10) relative to the signal appearing at the adjacent ports.

The current applied to the summing junction of Op Amp U31 (U31-2) is sinusoidally weighted by the resistances of Resistor Pack U30, forming the 20-step sine wave approximation of the desired tone output generated at the output of Op Amp U31 (U31-1).

#### NOTE

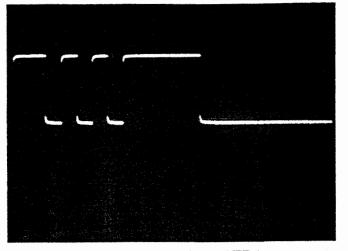

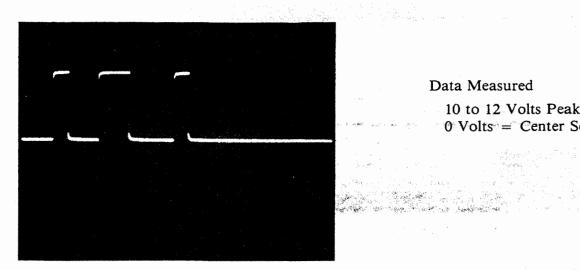

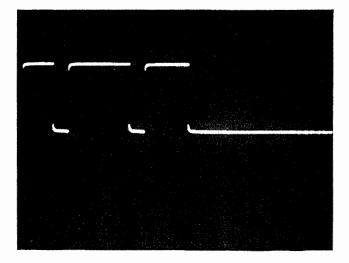

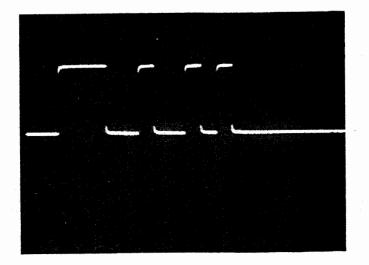

The first harmonic that is theoretically present in this waveform is the 19th harmonic, and is at a level of 25.6dB below the fundamental frequency.