### BELL SYSTEM PRACTICES Plant Series

1.

2.

3.

SECTION 578-500-111 Issue 4, November 1970 AT&TCo Standard

PAGE

# "DATASPEED<sup>®</sup>" PRINTER (RECEIVE-ONLY)

#### ELECTRONIC CIRCUITS

### DESCRIPTION AND PRINCIPLES OF OPERATION

CONTENTS PAGE GENERAL.... 1 COMPONENTS..... 4 4 4 CONTROLS AND INDICATORS . . . . 7 8 A. DAIF1 Serial Interface ..... 14 B. DAIF2 Parallel Interface . . . . . C. Discrete Calling Generator .... 18 CHARACTER GENERATOR . . . . . . 18 Α. General ..... 18 Detailed Circuit Description.... В. 22 26 **A**. General ..... 26 B. Detailed Circuit Description. . . 28 POWER SUPPLY ..... 31 31 Α. General ..... в. Detailed Circuit Description. . . . 34 CONTROL CIRCUIT CARDS . . . . . . 37 Α. Pre-Paper Puller Motor 37 Control (Paper Brake) ..... Line Feed Motor Regulator . . . 38 B. C. Paper Jam/Paper Out Alarm... 39 INK HEATER AND LINE FEED BRACKET ASSEMBLY ..... 40 PAPER WINDER (Optional Feature) ..... 41 DATS1 SIMULATOR ..... 43

|    |                                                | General<br>Detailed Circuit Description |  |

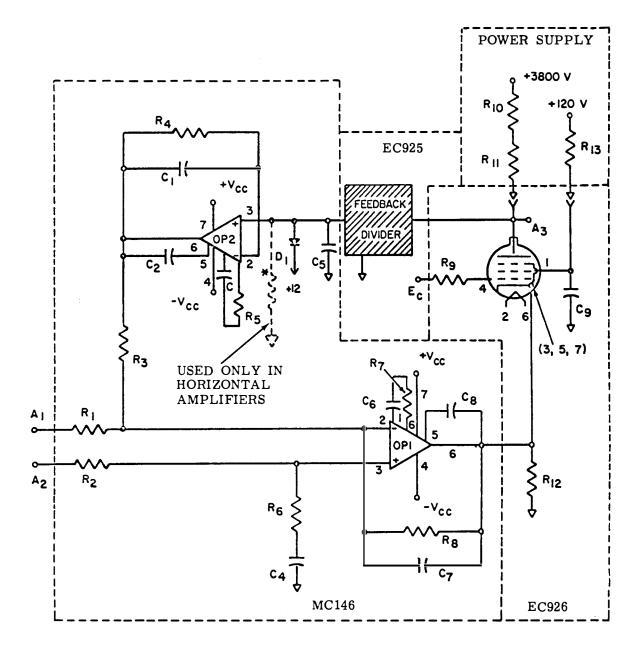

|----|------------------------------------------------|-----------------------------------------|--|

| ł. | APPENDIX - LOGIC SYMBOLS AND<br>CONFIGURATIONS |                                         |  |

CONTENTS

## 1. GENERAL

1.01 This section contains the description and operating principles of the DATASPEED printer operator controls, data set interface, character generator, printer drive, power supply, ink heater and line feed bracket assembly, data simulator, and discrete calling generator modification kit. It is reissued to incorporate recent engineering and technical comments not previously presented. These engineering changes include a new built-in test character generation circuitry, redesign of the paper jam/paper-out alarm circuit to substitute a paper-out switch for detection of a paper-out conditionusing electronic logic, redesign of the line feed motor regulator circuit to allow increasing the fuse valve in the paper brake circuit, redesign of circuitry on the input logic card to reduce noise sensitivity, redesign of circuitry on the output logic card to reduce noise sensitivity and improve operation, redesign of the power supply to shut off the high voltage when the +6 v dc fuse is blown and to permit the high voltage to come on immediately after the interlocks are closed, and redesign of the paper winder circuit card to improve reliability. Since this is a general revision, marginal arrows ordinarily used to indicate changes and additions are omitted.

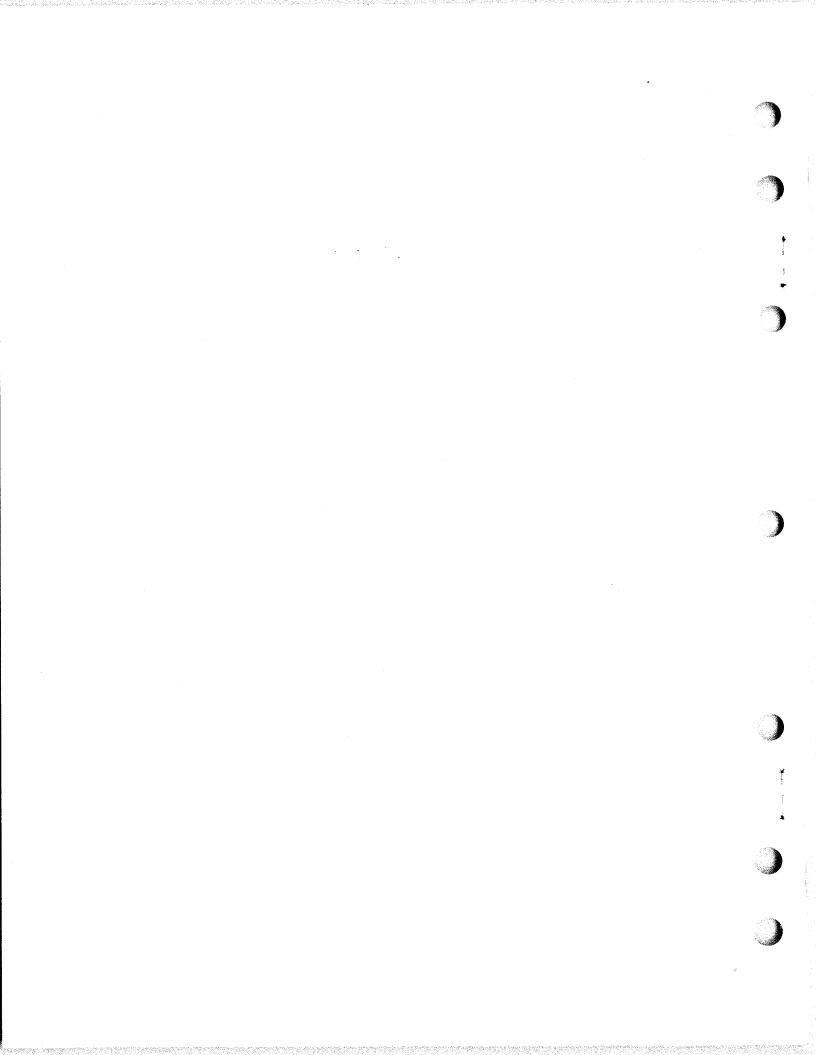

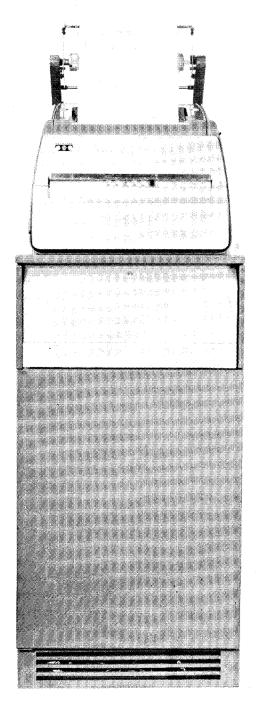

1.02 The DATASPEED printer operates from a signal source at 750, 1050, or 1200 words per minute (75, 105, or 120 characters per second) either directly or over telephone facilities. To interface with telephone facilities it may have its own data set (Figures 1 and 2) or it may be

Prepared for American Telephone and Telegraph Company by Teletype Corporation © 1968 and 1970 by Teletype Corporation All rights reserved. Printed in U.S.A.

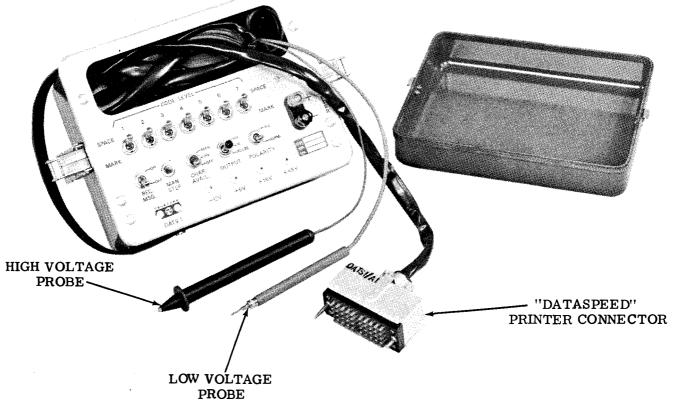

- Figure 1 DATASPEED Printer (Receive-Only) With Blank Front Panel

- Figure 2 DATASPEED Printer (Receive-Only) With Shelf for 202C Data Set or 804A Data Auxiliary Set

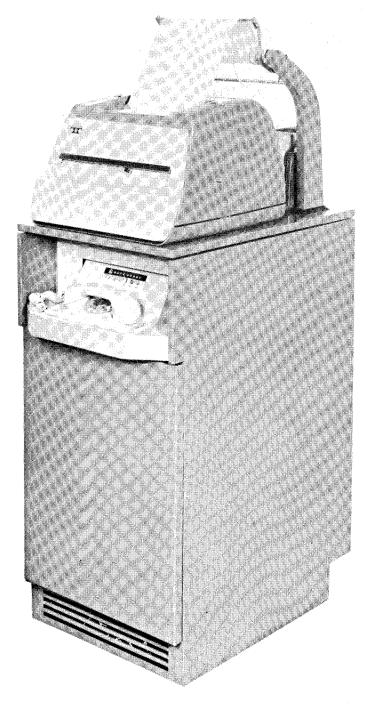

Figure 3 - DATASPEED Printer With Cabinet Panels and Cover Removed and Top Shelf and Modules Extended connected to an external data set in a DATA-SPEED sender or receiver. The data set is not furnished with the printer in either case. Sets used with a serial interface operate at 1050 or 1200 wpm, and those with a parallel interface operate at 750 wpm.

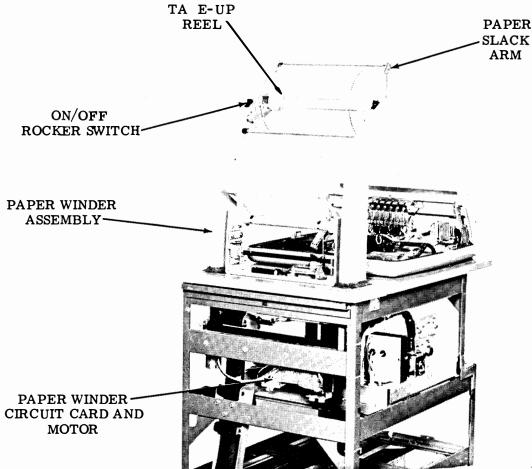

1.03 The set consists of a cabinet containing the power supply and electronic modules plus space for a data set, with the page recorder and paper transport housed in a separate cover on top (Figure 3). A paper winder and unwinder are mounted outside the cabinet at the rear. Operator controls are located on a stripat the front of the cover. There are additional controls on the data set (if present) and inside the cabinet.

1.04 Power is supplied to the set from a 117 v ac line. High voltage is used in the recorder for printing. As a safety feature, two magnetic reed interlock switches are located inside the cover and one is located at the top center of each door opening to shut off the high voltage when any part of the cover is raised or the front or rear door is opened.

### 2. COMPONENTS

2.01 Most of the electronic circuits are contained in the following four modules:

DAIF serial or parallel interface (may also contain discrete calling generator modification kit),

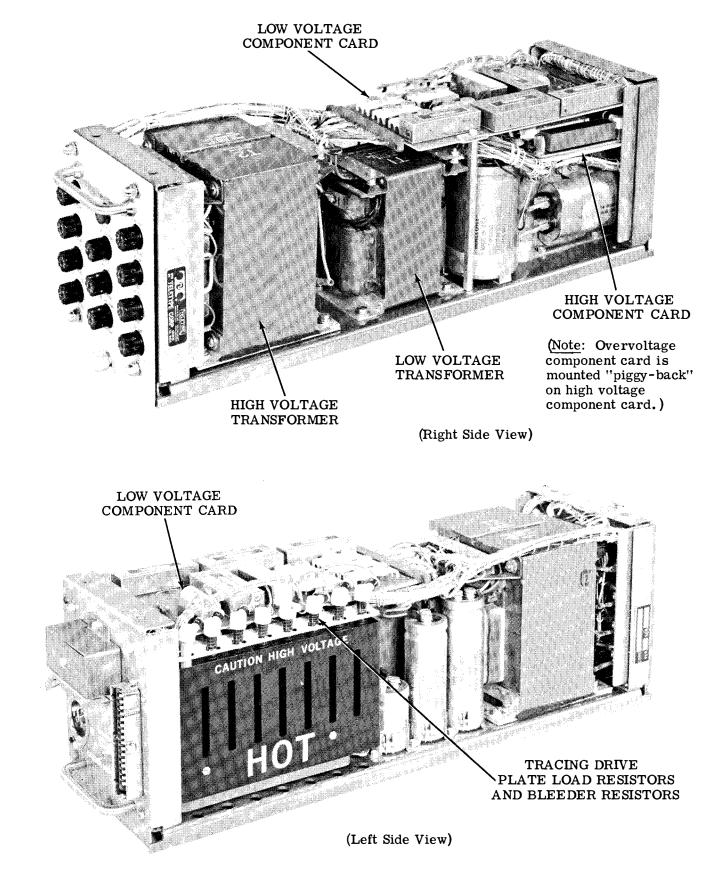

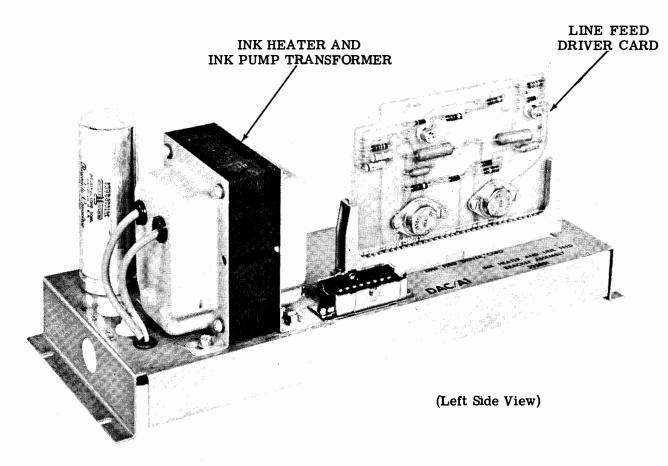

DAG character generator, DAD printer drive, and DAPS power supply. The DAD and DAPS modules and DAG and DAIF modules are attached to each other vertically when installed in the set so they are drawn out together (Figure 3). Other circuits are located in the ink heater and line feed bracket assembly, which is mounted on the data set shelf (not visible in Figure 3).

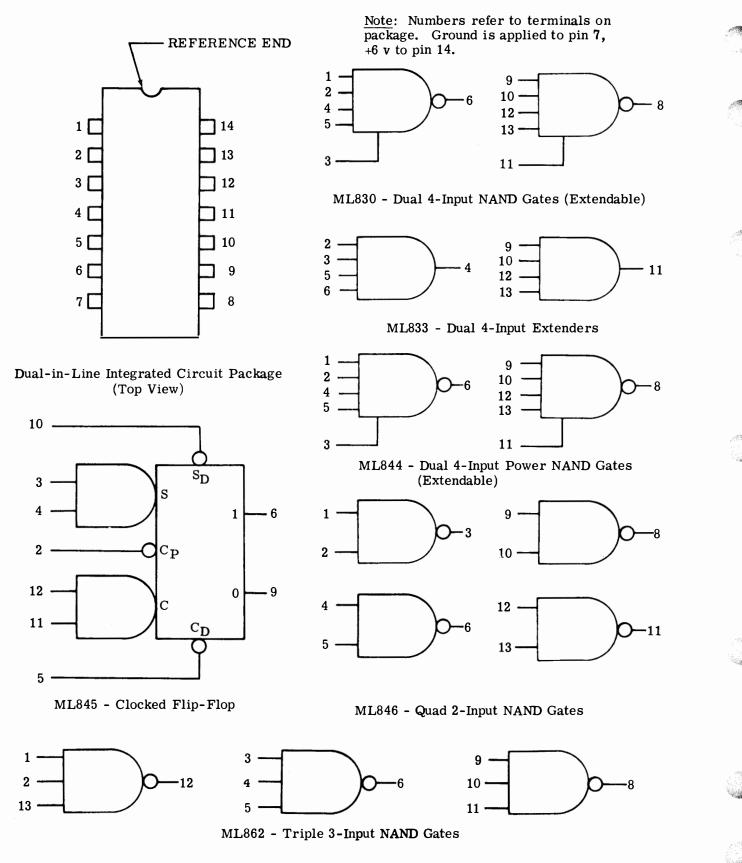

2.02 Components are mounted on etched circuit cards of various sizes (except for the power supply), some extending the entire length of the module. Besides discrete components such as resistors, capacitors, and diodes, many cards contain miniature integrated circuits identified by ML numbers. These cards have MC designations while cards with only discrete components have EC designations.

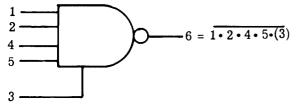

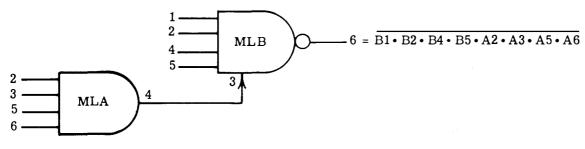

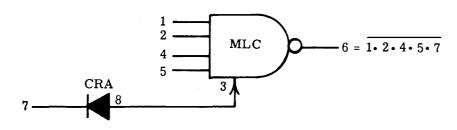

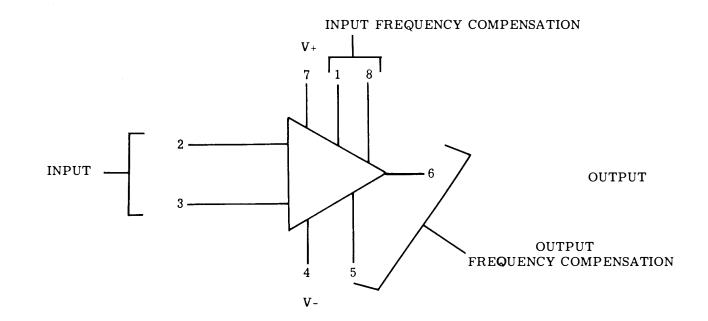

2.03 Integrated circuits used in the modules are of two types: Logic functions (gates and flip-flops) and operational amplifiers (op amps). Logic circuits are digital devices; that is, they respond to and produce as outputs high or low voltage levels, or high-to-low or low-tohigh transitions only. Op amps are linear devices and respond to a continuous range of voltages. All digital circuits used are compatible with the diode-transistor logic (DTL) family and all linear circuits are "709" type op amps. Schematic symbols, truth tables, and configurations of the various components are shown in Part 4.

### 3. OPERATION

3.01 Reference documents useful to understand the operation of the electronic circuits are listed on WDP0194.

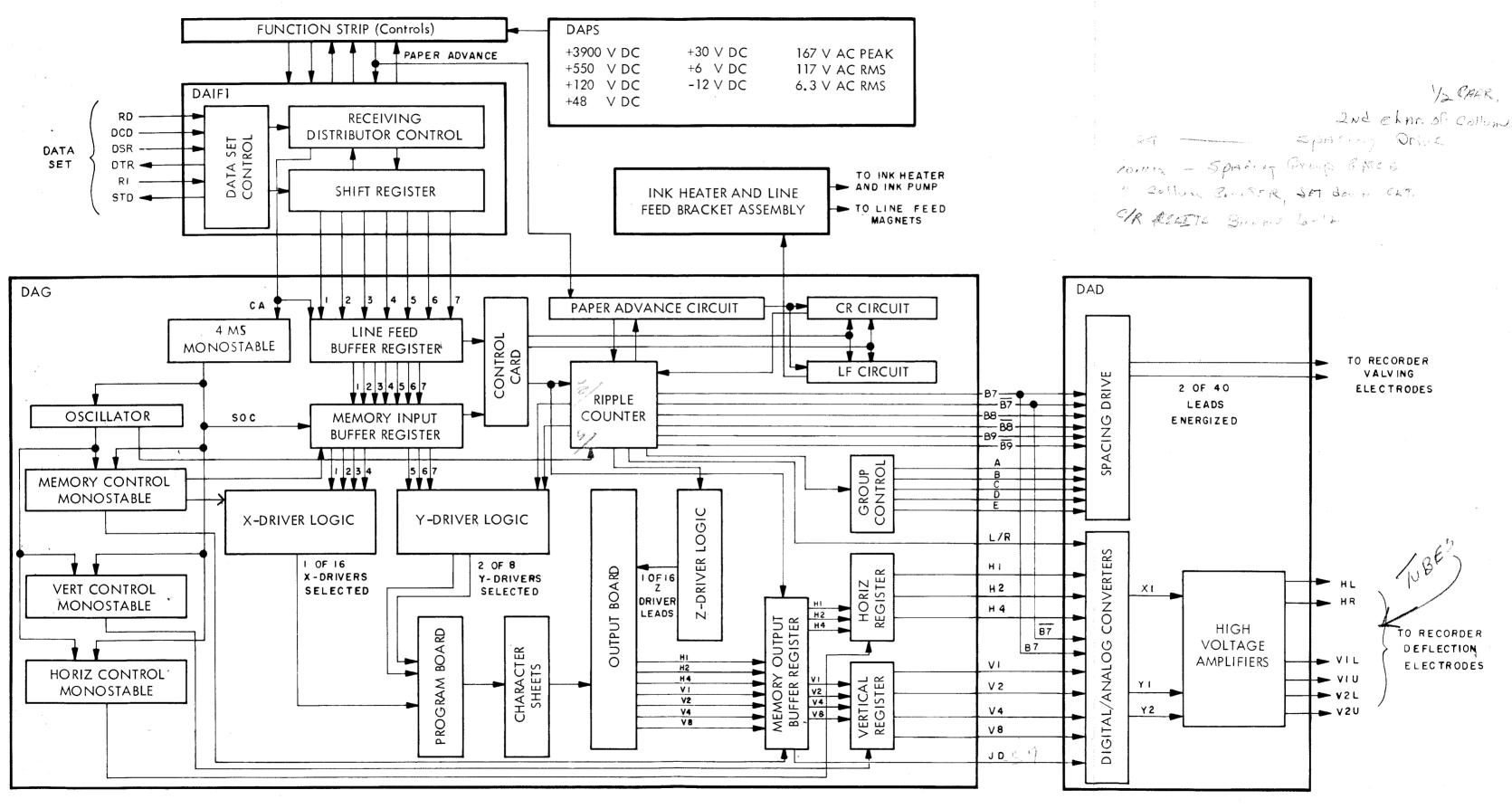

3.02 Operation is described in the order a character follows from the time its signal appears at the interface until it is printed on the page. Refer to Figure 4 for a block diagram of electronic operation.

## CONTROLS AND INDICATORS

3.03 The function strip of the DATASPEED printer is shown in Figure 5. The operator controls and indicators are as follows:

BREAK — A momentary pushbutton switch that turns off reverse channel when depressed to indicate that a break in transmission is desired. The button lights while it is depressed.

TRANS START — A momentary pushbutton switch that starts the discrete calling generator accessory (if present) which sends a discrete code sequence to start an unattended transmitter. The button lights while it is depressed and goes out when the sequence is finished.

PRINTER ON — An indicator and momentary pushbutton switch that lights when not depressed if the printer has all conditions necessary for printing (a supply of paper and all interlocks closed) and has its motors and high voltage on. The indicator lights when depressed if all interlocks are closed, whether the printer is ready to receive or not.

READY — An indicator and momentary pushbutton switch that lights when not depressed if the printer has all conditions necessary for printing and the high voltage is capable of turning on or is on. If an overvoltage condition should occur (excessive plate voltage on one or more high voltage tubes), the high voltage will be shut off and the READY lamp will go out. Operating the pushbutton resets the circuit, so the lamp will go on again if the overvoltage condition was temporary. How-

ISS 4, SECTION 578-500-111

Figure 4 - Block Diagram of DATASPEED Printer (Receive-Only) Electronic Circuits (Serial Interface)

Page 5/6

ISS 4, SECTION 578-500-111

Figure 5 - Operator Controls (At Front of Cover)

ever, the READY lamp always lights while depressed to indicate that it is not burned out.

PAPER ADVANCE — A momentary pushbutton switch that feeds out paper. The button lights while it is depressed.

PAPER ALARM — A red indicator which lights when the paper supply drops below a specified level. The lamp may be tested by depressing the button; on late design units, depressing the button causes W test characters to be generated repeatedly.

The BREAK and TRANS START buttons are not used in private line installations.

**3.04** In addition to the controls and indicators on the function strip, there are five others located as follows:

MAIN POWER — A toggle switch, located on the cabinet frame below the DAPS module. This switch turns on the 117 v ac power to cabinet.

NORM. /TEST — A slide switch, located on the side of the DAIF module frame. This switch allows the printer to operate, when in the TEST position, regardless of the condition of the data set.

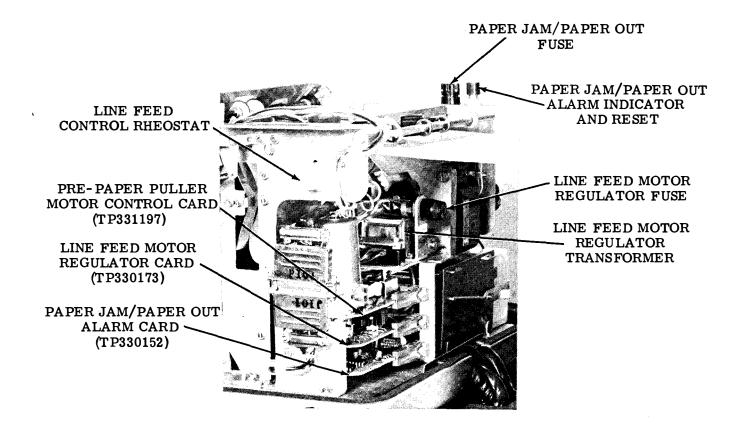

PAPER JAM/PAPER OUT ALARM — A red lighted pushbutton, located on top of the left side frame of the paper transport. The lamp lights to indicate a paper line feed failure, caused by paper being allowed to run out, breaking, or jamming. (On early design units, failure of the pre-paper puller motor will also cause an alarm to be indicated.) This alarm occurs on early design units if the

paper storage loop is not renewed within 28 to 29 line feed steps (normally the pre-paper puller motor renews the paper storage loop after 18 line feed steps, resetting the alarm circuit) or the pre-paper puller motor runs more than 480 milliseconds; on late design units, this alarm occurs if the paper-out switch operates or the pre-paper puller motor runs more than 1.2 seconds. In either case, when an alarm condition occurs the READY light on the control strip will go out, the paper jam/paper-out alarm lamp will light, and the printer will become inoperative. The PAPER ALARM lamp may be lighted also. Depressing the paper jam/paper-out alarm pushbutton after the condition has been corrected resets theprinter and extinguishes the red light.

OVERRIDE — A pull switch located on the lower front of the cabinet frame, by the lower door hinge, in back of the front door. The switch overrides (bypasses) the interlock switches for the front and rear doors when extended forward, permitting the printer to be turned on manually for servicing when the front door is open or removed.

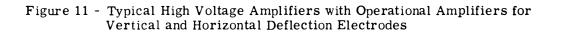

HIGH VOLTAGE POWER ON — A red indicator, located on the faceplate of the DAPS module. It is behind the front door and will be visible only when the door is open and the override switch is operated. This indicator lights when the high voltage is on.

## INTERFACE

3.05 The printer is available with either of two interfaces, serial or parallel, housed in the DAIF module. The serial interface (DAIF1) is used where the transmitted data is in serial

### SECTION 578-500-111

form. It provides operation at 1050 and 1200 wpm when used with a 202C or 202D data set or equivalent. The parallel interface (DAIF2) is used in installations where the incoming data is in parallel form. It provides operation at 750 wpm when used with a 402D data set or equivalent. Modification kits are necessary to interface with type 2 or type 5 DATASPEED sets, and an accessory is available to provide the discrete calling feature. Late design units include a test character generator circuit.

A. DAIF1 Serial Interface

General

3.06 The DAIF1 interface has one mode of operation, serial receive only. It provides the station controls and signal conversion necessary to enable data interchange between a signal source such as a 202C or 202D data set or equivalent and elements of the high speed printer. The interface converts data from polar serial start-stop form to neutral parallel (voltage) form. The baud rate is fixed by the interface crystal oscillator frequency. The data output of the interface, applied to the character generator module (DAG), consists of a sevenbit parallel data signal plus a character available signal.

3.07 Both the printer and the sender are controlled by the interface in either the attended or unattended mode of operation. The interface signals the printer to turn on its motors and enables data to flow only if the printer indicates that it is ready to receive. If the printer cannot receive, the interface signals the sender that no data should be sent.

3.08 The interface is insensitive to character code and can be wired for 5-, 6-, 7-, or

8-level characters enclosed in a 7.00-, 7.42-,

8-, 9-, or 10-unit frame. Its parallel output can be shifted to handle the 5-level code for type-setting by means of a jumper clip arrangement so that levels 2 through 6 are received in level positions 1 through 5.

3.09 Power requirements for the interface are as follows:

$\begin{array}{r} +6.0 + 0.6 \ v \ dc \ at \ 0.500 \ amp \\ -12.0 + 1.2 \ v \ dc \ at \ 0.150 \ amp \\ +18.0 + 1.8 \ v \ dc \ at \ 0.060 \ amp \\ +48.0 + 6.0 \ v \ dc \ at \ 0.200 \ amp \\ 117 + 10 \ v \ ac, \ 60.0 \ +0.5 \ Hz \ at \ 1.0 \ amp \end{array}$

3.10 Input signals from the signal source must conform to EIA Standard RS232-B (+5 to

+25 v for a space or on condition and -5 to -25 v for a mark or off condition). Output signals to the printer are +6.0 +0.6 v for a mark or off condition and  $0.0 \pm 0.5$  v for a space or on condition. These signals will have less than 45 percent distortion per bit and 5 percent distortion per character. Output signals to the signal source are +6.0  $\pm 0.6$  v for a space or on condition and  $-12.0 \pm 1.2$  v for a mark or off condition.

3.11 There are six options for the DAIF1 interface, excluding variations in bit timers for different operating speeds. All are strapping options, as follows:

- DU for operation on a dial-up or switched network

- PL for operation on a private line or dedicated network and direct interface to a DATASPEED Type 2 Sender

- XW for operation with ASCII (United States of America Standard Code for Information Interchange) or with 7.00- or 7.42-unit Baudot code and 10-unit Baudot code not compatible with DATASPEED senders and receivers

- XX for operation with 10-unit Baudot code, DATASPEED compatible

The other two options, AW and BW, are present only on late design units equipped with the test character generator card MC192:

AW — ASCII W

BW — Baudot W, 2

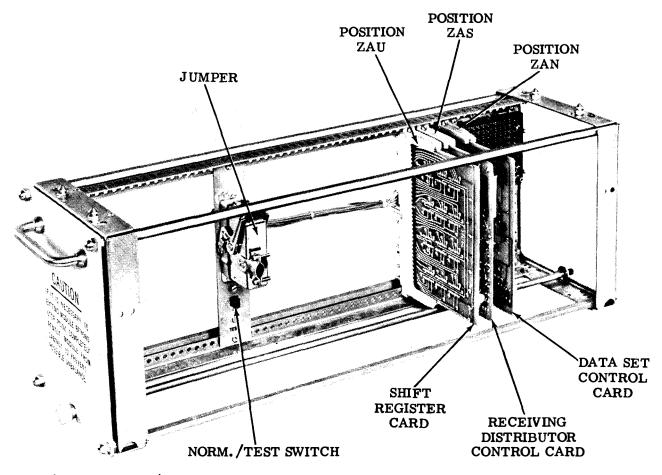

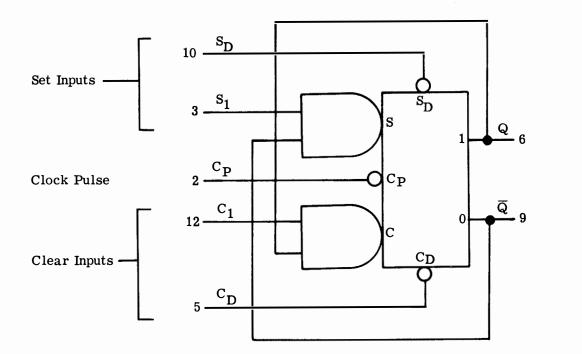

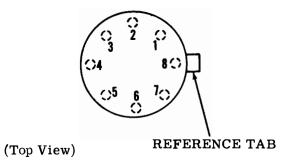

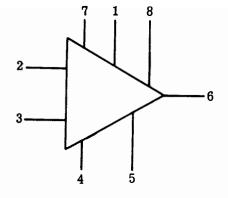

Physically, the interface consists of three etched circuit cards with integrated circuit and discrete components (in positions ZAU, ZAS, and ZAN) and a NORM./TEST switch (Figure 6). On late design units an additional circuit card is present in position ZAW (not shown in figure).

**Dial-Up Operation**

3.12 If the data sets at the printer and remote senderare equipped with handsets, calls may be originated manually at either the printer or remote sender. With both data sets in the talk mode, the calling station dials the other station. When the called station answers, if the operators agree to go into the data mode, the

Page 8

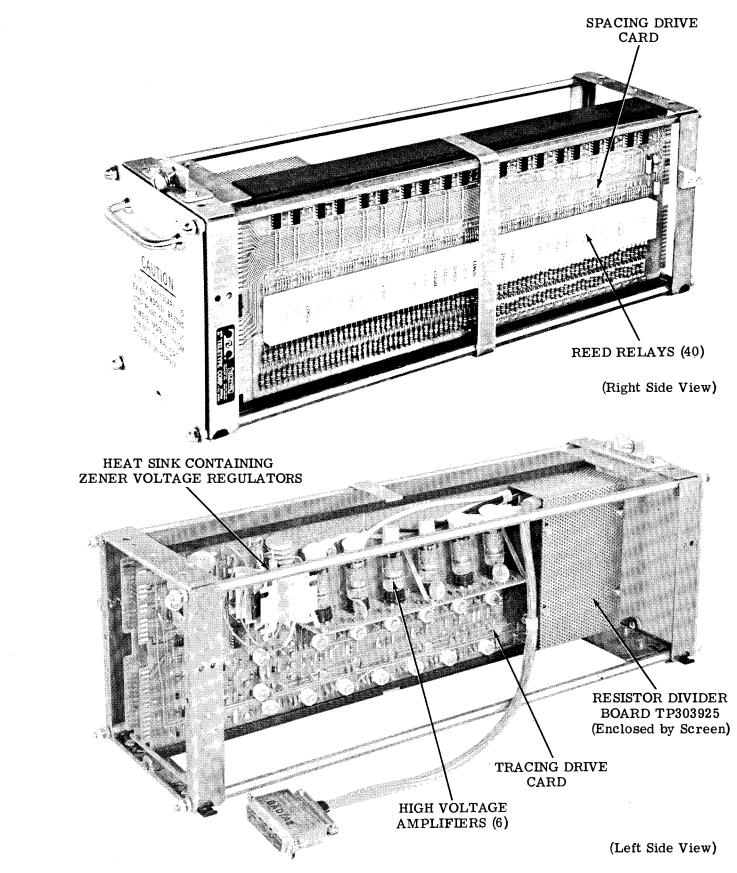

(Right Side View)

Figure 6 - DAIF1 Serial Interface Module

called station must go into the data mode first. When the calling operator hears the 2025 Hz recognition tone, the calling station must be placed into the data mode before the tone ends or the call will be dropped.

3.13 In the data mode, the printer data set turns on the data set ready (DSR) lead to the DAIF1 interface. The interface then turns on the receive message (RM) lead to the printer and starts the 15-second on-hook timer in the interface. When the sender turns on its data carrier, the printer data set turns on the data carrier detector (DCD) lead to the interface, disabling the 15-second timer and enabling the receive data (RD) input to the interface. The DCD lead must turn on before the timer times out or the call will be dropped.

3.14 When the printer turns on, it enables the ready lead to the interface. This turns on the supervisory transmitted data (STD) lead

to the data set, which turns on reverse channel sender (RCS) to the printer if the data set is so equipped. Data transmissions may now take place.

3.15 For unattended operation, the data set must be in the auto mode and the printer must be capable of receiving data (DTR lead on). When the incoming ring signal appears on the line, the data set turns on the ring indicator (RI) lead to the interface and switches to the data mode. The data set turns on the DSR lead to the interface and sends a 2025 Hz recognition tone to the sender. The rest of the turn-on sequence is as described for manual on-line operation.

3.16 Turn-off for either manual or unattended operation occurs when the data carrier is absent for more than about 15 seconds. The data set turns off the DCD lead to the interface about 15 milliseconds after the data carrier ceases. This starts the 15-second timer in the interface, which times out and shuts off the DTR lead to the data set. The data set drops the call, turning off its RCS and DSR leads, so the interface turns off the RM lead to the printer. The printer shuts off its motors, high voltage, and PRINTER ON lamp. This turns off the ready lead to the interface, so the interface turns off the STD lead to the data set. The printer is now ready for another call.

Private Line Operation

3.17 In private line operation, no handset is used with the data set. Consequently, the data set is permanently on line and the data set ready (DSR), data terminal ready (DTR), and ring indicator (RI) signals are not used. Data carrier detector (DCD) is the main controlling signal. The sender activates the printer by placing the carrier on line, causing DCD to come on to the interface. Line feed signals must not be sent for at least 1/3 second in order to give the motors time to reach operating speed.

3.18 When DCD turns on, it causes the interface to enable the receive data (RD) input and turn on the private line-receive message (PL-RM) lead to the printer. The printer responds by turning on its motors, high voltage, and PRINTER ON lamp. This turns on the ready lead to the interface, enabling the supervisory transmitted data (STD) lead and providing reverse channel to the sender, if the data set is so equipped.

3.19 At the end of the message, the sender turns off the carrier. This disables the DCD and PL-RM leads, and the printer shuts off. The printer is now ready for another message.

**Detailed Circuit Description**

3.20 For details of the circuitry, refer to wiring diagrams 8251WD (serial interface schematic), 8263WD (serial interface master reference), 322130 (MC130 shift register card), 322180-87 (MC180-87 receiver distributor control cards), 322132 (202C and 202D data set control RO card), 322192 (MC192 test character generator card — late design units only), and 8260WD (timing diagram). Wiring diagram 8251WD is not a complete schematic, and must be supplemented by the master reference wiring diagram (containing notes) and the three individual circuit card drawings (containing the schematics for the circuitry on the cards).

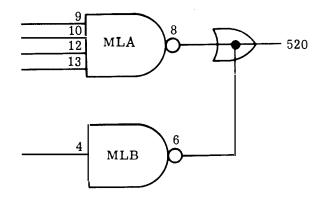

3.21 References to components in this description are abbreviated as follows: XZAN, XZAU, XZAS, and XZAW (late design units only) refer to the terminals on the cards in positions ZAN, ZAU, ZAS, and ZAW, respectively, and ML1, ML2, etc, refer to specific integrated circuit components. The number following an XZ or ML designates an associated terminal or pin. For example, 'XZAN-18, ML2-3, MC132" refers to terminal 18 on card MC132, located in position ZAN, which is connected directly to pin 3 on circuit ML2. The drawing of card MC132 shows that circuit ML2 is three three-input NAND gates. All 'gates' mentioned in the description are NAND gates unless stated otherwise, and all references to MC180 apply to cards MC181 through MC187 as well. Refer to the appendix (Part 4) for schematic symbols and truth tables for the integrated circuits.

3.22 Logic signals, unless otherwise noted, are either +6 v (high) or 0 v (low). The on or off condition of a circuit element varies with its function and is defined separately.

Turn On Sequence

3.23 The NORM./TEST switch must be in the NORM. position. This enables the receive message (RM) lead, XZAN-18, MC132, which connects to the autoon relay driver input.

3.24 The DAIF/AAA interface turns on (+6 v) the data terminal ready (DTR) lead, XZAN-33, if:

Disconnect lead XZAN-32 is high (positive) at ML1-4, MC132. This indicates ageneral ready condition at the printer; cabinet closed, some paper available for printing.

(2) Selectable lead XZAN-12 is low (zero) at ML1-10, MC132. This indicates that there is a predetermined amount of paper on the supply roll. The low at ML1-10 produces a high at ML1-8. This high is applied to ML1-3.

Note: If the paper supply is below the predetermined level the selectable lead goes high (positive) and turns the DTR lead off (-12 v) before the printer answers a new data call. However, the selectable lead cannot turn off the DTR lead once a call has been established.  (3) The on-hook timer (OP1-6, MC132) is high (+6 v) at ML1-5. (OP1-6 is high when the timer is initially set.)

With high signals at all three input leads, ML1-6 is low and Q2 saturates to provide +6 v at the DTR lead.

3.25 The high at ML1-8 also appears at ML2-1. Thus, a data set ready (DSR) signal from the data set, applied to ML2-2, will cause ML2-3 to go low. The RM lead, XZAN-18, goes low, turning on the printer.

3.26 The low at ML2-3 causes ML2-11 to go high, placing a high on ML3-1. With no data carrier detector (DCD) signal from the data set, XZAN-25 is low, forcing ML2-8 high to place a high on ML3-2. With highs on both of its inputs, ML3-3 goes low. This forces ML2-6 high and causes OP1-6 to start timing out.

3.27 The DCD lead, XZAN-25, must be turned on (positive) within 15 seconds after the DSR lead turns on. ML2-8 then goes low, causing ML3-3 to go high and ML2-6 to go low, resetting OP1-6. If the DCD lead does not turn on within the 15-second interval, OP1-6 will time out and produce a low at ML1-5. This forces ML1-6 high, cutting off Q2 and turning off the DTR lead.

3.28 Assuming the DCD lead has turned on within the timing limit, it forces ML3-11 high. The high at ML3-11 is gated with ML3-8, which is high unless the data set is in an answering sequence. These two highs enable ML1-12, so that the output receive data (RD) lead, XZAN-16, is dependent on the incoming data at ML1-13.

3.29 The ring indicator (RI) lead, XZAN-26, is normally off (negative) and goes on (positive) only when the data set is ringing. Gated with the high from ML3-11, the RI signal forces ML3-8 low. This inhibits the RD gate, ML1-12, during the answering sequence of the data set or associated equipment. Once the call is answered the RI lead goes off (negative), forcing ML3-8 high and enabling ML3-6 and ML1-12. Thus, to permit a data transfer from the RD input (XZAN-24) to the RD output (XZAN-16) of the control unit, XZAN-26 (or XZAN-4 in private line installations), must be held low.

3.30 In installations where it is desirable for the data set to inform the sending station that it is ready to receive data, a signal may be obtained for this purpose at the supervisory transmit data (STD) lead, XZAN-29. The autoon relay in the printer grounds the ready lead, XZAN-28, causing Q1 to conduct and thus turning on the STD lead to the data set.

#### Bit Timer

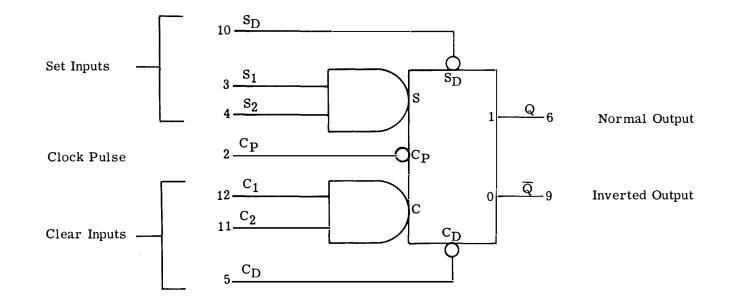

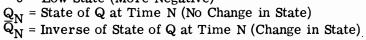

3.31 A bit timer on the MC180-187 control card consists of a free-running crystal oscillator, four control gates, six J-K flip-flops, which provide a divide-by-64 logic function, and a clocked flip-flop for pulse shaping.

3.32 The output of the oscillator, at the collector of Q1, card MC180, is applied to ML8-3, which provides isolation and pulse shaping. ML8-4 is applied to the clock pulse input of ML2, the first stage of the divide-by-64 counter. With no incoming information on the RD line, XZAS-B3, counter stages ML2, ML1, and ML3 are disabled by the low applied to their clear direct (CD) inputs by ML8-6. Thus, the output at ML3-8 is low. Flip-flop ML6 is also disabled by a low applied to its CD input by ML14-3, so the ML6-6 output is low.

3.33 To initiate the bit timer operation, ML8-6 must go high and remain high for the duration of the bit timer cycle. Once this condition is satisfied, the timer begins a counting sequence. Gate ML14-3 goes high and unclamps the clear direct of ML6. Gate ML14-6 now controls the clear direct of ML6. The output at ML6-6 remains low. The first negative transition of the oscillation at ML8-4 will shift the state of ML2-6, and each ensuing negative transition at ML8-4 will advance the counter one count. At a 1050 baud rate the output of the last counter stage, ML3-8, will go low exactly 476 microseconds after the first negative transition appears at ML8-4. The low at ML3-8, applied to the clock pulse input of ML6, causes the flipflop to change states. ML6-6 goes high and remains high. The clear direct on ML6-5 was disabled by the initial action of the counter. At the instant ML3-8 goes low, all binary outputs of the counter are low. The next negative transition at ML8-4 resets ML2-6 high. The following high at ML8-4 is gated with the high at ML2-6 through ML14-6 to produce a low at ML6-5, resetting the flip-flop so that ML6-6 is low.

3.34 To stop the counter and associated circuitry, ML8-6 must go low.

3.35 The oscillator and associated counter is essentially free running and generates pulses approximately 11 microseconds in duration every 476 microseconds for operation at a 1050 baud rate. This rate is established by the frequency of the crystal used in the oscillator circuit. The crystal can be changed to provide the pulse delays and pulse durations required for other baud rates.

## Receive Data

3.36 With no input data the RD lead, XZAN-24, MC132, is low, corresponding to a stop pulse (mark) from the data set. This is gated through ML1-12 to provide a high at XZAN-16. This high is applied to the RD lead of the receiving distributor control card, XZAS-B3, MC180, preventing the distributor from generating any control signals.

3.37 When a start pulse (space) is applied to XZAN-24, MC132, the XZAN-16 lead goes low. This low is applied to XZAS-B3, MC180, and also to XZAU-B29, MC130. The low at XZAS-B3 forces ML14-11 high: This causes ML8-8 to go low, which forces ML8-10 high. The SE lead, XZAS-B2, is strapped to ground, giving a high at ML8-12, so the signal at ML8-10 is in control of the wired OR gate and ML14-10 at all times. XZAS-A34, the receive message (RM) lead is also strapped to ground, giving a high at ML4-6 and at the R+ lead. XZAS-A35, at all times. With both ML14-9 and ML14-10 high, ML14-8 goes low and forces ML8-6 high. This starts the operation of the bit timer as explained in 3.32.

3.38 When ML8-8, MC180 is low, due to a low at XZAS-B3, the CD input to ML5 is enabled (high). ML6-6 goes from low to high, and this high appears at ML4-13. Gated with the high at ML4-12, it forces ML4-11 low. This low causes ML10-6 and ML10-8 to go high. The high at ML10-8 is applied to ML12-10, and is gated with the highs at ML12-12 and ML12-13 to force ML12-8 low. This low, applied to ML7-13, forces ML7-11 high. It is also transferred to XZAU-A30, MC130, the register reset (RR) lead of the shift register, where it resets all of the register flip-flops except ML4. The outputs (pin 6) of all flip-flops except ML4 on the MC130 card are now high.

3.39 The nine highs from the flip-flops of the shift register are gated together on the MC180 card by ML11-2, 3, 5, 6, 9, 10, 12, and 13, and ML12-2. This forces ML12-6 low. The low at ML12-6 appears at ML12-13 and causes ML12-8 to go high, removing the reset. Approximately 300 nanoseconds elapse from the time the reset is initiated to the time the reset is decoded and removed.

3.40 Approximately 10 microseconds after ML6-6 on card MC180 goes high, ML8-4 and ML2-6 are high and ML14-6 goes low. This places a low on the clear direct of ML6, forcing ML6-6 low. ML6-6 going low forces ML4-11 high, and this high causes ML10-6, the clock pulse (CP) lead, to go low. The pulse is applied to XZAU-B30, MC130, transferring the start signal, the low at XZAU-B29, and the high at XZAU-B31 into ML9. When this occurs, ML9-6 goes from high to low. The clock pulse also transfers the high at ML8-6 to ML4-4. ML4-9,  $\overline{ST}$  is now low, and this low is applied with the lowat ML9-6 to terminals 1 and 13 of gate ML13 on card MC180. This forces ML13-12 high.

3.41 When ML6-6 of card MC180 goes low, it also flips ML5-9 from high to low. This low appears at ML4-12 and holds ML4-11 high until ML6-6 goes through another high-to-low transition. The result is a high-to-low transition (a clock pulse) at ML10-6 for every other cycle of ML6-6. Thus, ML6-6 operates at twice the bit rate and ML5-9 effectively divides this rate in half to match the bit rate of the incoming information.

3.42 As long as ML13-12, MC180 is high, ML8-2 will be low, ML14-8 low, and

ML8-6 high, keeping the bit timer on. At the same time, ML13-8 is low, forcing ML7-8 high and holding the character available timer (Q4) off by producing a low at ML9-6. The low at ML13-8 disables the RR lead, ML12-8.

3.43 When a start bit (space) is shifted into ML4, MC130, and a stop bit (mark) is shifted from the RD input (XZAU-B29) into ML9, the SP and  $\overline{ST}$  inputs at pins 1 and 13 of ML13, MC180, are both high. This forces ML13-12 low, so ML13-8 and ML8-2 are forced high. With ML8-2 high, the mark (stop bit) on the RD lead (XZAS-B3) forces ML8-8 and ML8-11 high. This causes a low at ML8-10 and a high at ML14-8. The high at ML14-8 also holds ML14-1 high, and the second crystal output after it appears turns ML14-2 high also. When this occurs it forces ML14-3 low, placing a low signal on the direct clear input (5) of ML6, causing ML6-6 to go low. Before ML6 is cleared, both

inputs (13 and 12) of ML4-11 are high, making its output low, but when ML6-6 becomes low, ML4-11 goes high. This causes ML10-8 to remain low, preventing a reset of the input register. The high at ML13-8 is gated with the high at ML7-6 to produce a low at ML7-8, forcing ML9-8 and ML9-6 both high (through an external strap).

3.44 The high at ML9-6 triggers the 100 microsecond timer, Q4 and associated components, which times out and then produces a brief positive pulse (approximately 5 microseconds). This positive pulse is inverted by Q3, producing a negative pulse at ML9-1 and ML4-2 (early design units only). On early design units, the corresponding high at ML4-3 is gated with the high at ML12-12 to force ML4-8 low. This produces a character available (CA) signal at XZAS-B26. Although the low is present at ML4-8 for only about 5 microseconds, the high at ML4-3 and the resultant low at ML4-8 are held for approximately 20 microseconds because of the charge time of C5 at ML4-1. The low at the Q3 collector also forces ML9-3 high, and ML9-11 then goes low to prevent another pulse from the 100 microsecond timer. On late design units, the high at ML9-8 is gated with the high from ML9-11 to cause a low at ML4-3. This produces a character available (CA) signal at XZAS-B26. When the 100 microsecond timer, Q4 and associated components, completes its timeout period, ML9-1 goes low causing ML9-3 to go high. This sets the flip-flop, making ML9-11, low and ML4-3 high and removing the character available signal. The high output of ML9-3 is inverted by ML4-8 to prevent another pulse from the 100 microsecond timer. (The significance of this change is that on early design units, the CA pulse is delayed by 80 microseconds (typically) and is approximately 20 microseconds long, while on late design units, the CA pulse is not delayed and is approximately 80 microseconds long.) On both early and late design units, the ML9-3, ML9-11 flip-flop is reset when the next start pulse appears at the RD input. ML7-8 goes high when ML12-8 goes low, and the cycle begins again to present a new character in parallel form.

#### Turn Off

3.45 When the DCD lead, XZAN-25, MC132, turns off, it causes ML2-6 to go high.

The on-hook timer, OP1, times out and forces ML1-5 low, turning off (-12 v) the DTR lead, XZAN-33. The low on the DCD lead also disables

the RD gate by placing a low on ML1-1. Thus, the RD output at XZAN-16 goes high and remains high. This high stops MC130 and MC180 from cycling.

3.46 When DTR turns off, it causes the DSR lead, XZAN-27, MC132, to go low (-12 v).

DSR low forces ML2-11 high, turning off the RM lead. The DSR low also resets OP1 by forcing ML2-6 low. With OP1 reset, DTR can once again go high, provided the NORM. /TEST switch is still in NORM. The terminal is now ready for another call.

Test Character Generation

3.47 On late design units a test character generator circuit is located in the DAIF1 interface. Its purpose is to simplify cleaning of the recorder nozzles and electrodes by enabling the results of cleaning to be tested immediately, without waiting for an incoming message or connecting the DATS1 simulator. It does this by generating continuous W (or 2, with Baudot code in figures mode) characters whenever the PAPER ALARM button on the control panel is depressed, whether an incoming message is being received or not.

3.48 Depressing the PAPER ALARM button

supplies ground, through 3NO and 3C, to pin 21 on the control panel connector, CP1. This signal, generate test character, is connected via DAIF/AA1-41 to XZAW-35, where it is connected to ML1-13 on test character generator card MC192 (TP322192). The output of this gate, ML1-11, will go high since gate ML2-8 is held low through strap A. This high causes ML2-2, XZAW-26, to go low, supplying T.R.M. to the receive message input of the printer drive, DAD/C209 (via DAIF/AA1-26), and card MC132, XZAN-18 or XZAN-23 (via a DU or PL strap). This turns on the high voltage and permits printing.

3.49 The high on ML1-11 causes ML2-6 (XZAW-23) and ML2-10 (XZAW-21) to go low. These two leads, reset 2 and reset 1, are connected to B28 and B11, respectively, on card MC180-87. They serve the dual purpose of removing the character that is stored in the serial register and preventing the set from storing any additional characters coming in on line. This accomplished by holding the register in the reset condition. A low on ML12-8 will cause the input register to be held in the reset condition. This can be accomplished by holding all the inputs to ML12-8 high. The low (produced

#### SECTION 578-500-111

by the test character generator card) on B28 (ML10-12) causes ML10-8 to go high and thus ML12-9 and ML12-10 to go high. The low (produced by the test generator card) on B11 (ML13-9) causes ML13-8 to go high and thus ML12-12 to go high. The input, ML12-13, will be high unless the register is already in the reset condition. The register will then be reset by the small pulse produced at ML12-8.

3.50 The high at ML1-11 of card MC192 also appears at ML3-2. This gate allows the test charactergenerator card to generate a substitute character available pulse. The test character available (T.C.A.) pulses are generated with the aid of Q1, Q2, and their associated components. Capacitor C3 and diode D2 are used to increase the test character available (T.C.A.) pulse to a minimum of 30 µ sec. Capacitor C3 will effectively hold ML1-5 low longer by charging to the slicing level of ML1-6 with a low-to-high transition on ML1-4. Diode D2 is used to eliminate resistor R9 from the charging circuit of C1 and thus helps increase the width of the T.C.A. pulse. The unijunction oscillator is constantly generating pulses but they do not appear at ML3-3 (XZAW-20) because there is normally a low on ML3-2 (not generating a test character).

3.51 When the PAPER ALARM button is pushed, ML1-13 will go low, ML1-11 high and ML3-2 high. This high at ML3-2 permits the C.A. to appear at ML3-3 (XZAW-20). The test character is factory-programmed by cutting straps 1 to 7. Strap one is cut if the desired character has a spacing first bit. Strap two is cut if the desired character has a spacing second bit, etc. When ML1-11 goes high, ML1-3 goes low and ML2-12 goes high. This allows the input to gates ML3-6, ML3-8, ML4-3, ML4-6, ML4-8, ML4-11, and ML3-11 to sense the condition of straps 1 to 7. If the strap is closed, a ground will be sensed at the input of the gate thus causing a high (mark) at the output of its associated gate. If the strap is open, two highs will be sensed at the input of the gate and hence producing a low (space) at the output.

3.52 When the PAPER ALARM button is released, ML1-13 will go high thus permitting the next T.C.A., which is seen at ML1-9, to reset the flip-flop (ML1-11, ML1-8). Resistor R10 is a pull-up resistor used to help keep the flip-flop (ML1-11, ML1-8) from being set due to noise on the ML1-13 to switch contact lead. Capacitor C1 is also used to keep noise from setting this flip-flop. When ML1-11 is low, a small negative noise spike appearing on ML1-13 must be wide enough to overcome the R-C rise time of C1 in order to set the flip-flop (ML1-11, ML1-8) erroneously.

B. DAIF2 Parallel Interface

General

3.53 The DAIF2 interface has one mode of operation: parallel receive only. It provides the station controls and signal conversion necessary to enable data interchange between a signal source such as a 402D data set or equivalent and elements of the high speed printer. The interface converts data from parallel contact closures or equivalent to neutral parallel (voltage) form. The baud rate is fixed by the sender, but may not exceed the data set maximum (750 for a 402D). A 402D data set must be mounted external to the printer cabinet.

3.54 Both the printer and the sender are controlled by the interface in either the attended or unattended mode of operation. The interface signals the printer to turn on its motors and enables data to flow only if the printer indicates that it is ready to receive. If the printer cannot receive, the interface will signal the sender that no data should be sent.

3.55 The interface is insensitive to character code and can be wired for 5-, 6-, 7-, or

8-level characters enclosed in a 7.00-, 7.42-, 8-,

9-, or 10-unit frame. Its output can be shifted to handle the 5-level code for typesetting by means of a jumper clip arrangement so that levels 2 through 6 are received in level positions 1 through 5.

**3.56** Power requirements for the interface are as follows:

+6.0 +0.6 v at 0.125 amp -12.0 +1.2 v at 0.050 amp +48.0 +6.0 v at 0.200 amp 117 +10 v ac, 60.0 +0.5 Hz at 1.0 amp

3.57 Input signals for a mark or on condition must be ground (0.0 +0.5 v) capable of sinking 4 madc resistive, and for a space or off condition must be open or very high resistance (100 k ohms or higher) capable of withstanding +6.6 v. The timing lead must be on for a minimum of 5 milliseconds and should occur simultaneously with the beginning of each new character.

3.58 Output signals to the printer are +6.0 $\pm 0.6$  v through a 6 k ohm impedance for a mark or off condition and  $0.0 \pm 0.5$  v for a space or on condition, capable of sinking 10 ma dc resistive. The data signals will have the same duration as the incoming timing signal, and the output timing signal will be present for about 30 microseconds near the midpoint of the data signals.

3.59 There are six strapping options for the DAIF2 interface. Four are strapping options, as follows:

- DU for operation on a dial-up or switched network.

- PL for operation on a private line or dedicated network and direct interface to a DATASPEED Type 5 Sender or Receiver.

- XW for operation with ASCII or with Baudot code not compatible with DATASPEED senders and receivers.

- XX for operation with DATASPEEDcompatible Baudot code (bits 1 through 5 of code presented by sender in bit positions 2 through 6).

The other two options, AW and BW, are present only on late design units equipped with the test character generator card MC192:

AW — ASCII W

BW — Baudot W, 2

Physically, the interface consists of an etched circuit card with integrated circuit and discrete components and a NORM./TEST switch. On late design units an additional circuit card is present in position ZAR.

**Dial-Up** Operation

3.60 If the data sets at the printer and remote sender are equipped with handsets, calls may be originated manually to either the printer or remote sender. With both data sets in the talk mode, the calling station dials the other station. When the called station answers, if the operators agree to go into the data mode, the called station must go into the data mode first. When the calling operator hears the 2025 Hz recognition tone, the calling station must be placed into the data mode before the tone ends or the call will be dropped. 3.61 In the data mode, the printer data set turns on the data setready (DSR) lead to the DAIF2 interface. (This lead is also referred to as receive message (RM) in the DAIF2 interface.) The printer turns on its motors, high voltage, and PRINTER ON lamp, and starts the 15-second on-hook timer in the interface. The ready lead from the printer to the interface is turned on, and the interface turns on the supervisory transmitted data (STD) lead to the data set, if the data set is so equipped.

3.62 The data set must turn on the data carrier detector (DCD) lead within 15 seconds of the DSR (or RM) lead in order to disable the on-hook timer before it times out. If the timer is permitted to time out, it turns off the data terminal ready (DTR) lead to the data set, and the call is dropped. With the DCD lead on, the interface is ready to receive data.

3.63 For unattended operation, the data set must be in the auto mode. When the incoming ring signal appears on the line, it turns on the ring indicator (RI) lead. This places the data set in the data mode, and it is held there by the DTR lead from the interface. The rest of the turn-on sequence is as described for manual online operation.

3.64 Turn-off for either manual or unattended operation occurs when the data carrier is absent for more than about 15 seconds. The interface turns off the DTR lead to the data set, and the data set opens the DSR (or RM) lead to turn off the printer. The 15-second timer is reset, and the printer station is ready to accept another call.

Private Line Operation

**3.65** If the printer has no handset (402D data set without an 804A data auxiliary set), the printer station is unable to place calls but has the ability to answer calls and receive data when called by a sending station. The sender activates the printer by placing the carrier on line, causing the data carrier detector (DCD) lead to come on to the interface. This enables the receive message (RM) lead of the printer. When the printer turns on its motors, a ready signal is sent to the interface and the supervisory transmitted data (STD) lead is enabled. This serves as a reverse channel indication to the sender if the data set is so equipped. If the data set is not equipped for reverse channel, the sender must not transmit a line feed signal for at least 1/3 second after the DCD lead is turned on. At the end of the message the carrier is turned off by the sender, causing the DCD and RM leads to go off and shut off the printer.

### **Detailed Circuit Description**

3.66 For details of the circuitry, refer to wiring diagrams 8267WD (parallel interface master reference), 8268WD (parallel interface schematic), 8274WD (parallel interface actual wiring diagram), 322134 (MC134 control card), and 322192 (MC192 test character generator card — late design units only). Wiring diagram 8268WD is not a complete schematic, and must be supplemented by the master reference wiring diagram (containing notes) and the control card wiring diagram (containing the schematic for the circuitry on the card).

3.67 Reference to components in this description are abbreviated as follows: XZAN and XZAR (late design units only) refer to the terminals on the cards in positions ZAN and ZAR, respectively, and ML1, ML2, etc, refer to specific integrated circuit components. For example, ''XZAN-20, ML1-4'' refers to terminal 20 on card MC134, located in position ZAN, which is connected directly to pin 4 of circuit ML1. The description of card MC134 shows that circuit ML1 is three three-input NAND gates. All gates mentioned in the description are NAND gates unless otherwise stated. Refer to the appendix (Part 4) for schematic symbols and truth tables for the integrated circuits.

3.68 Logic signals, unless otherwise noted, are either +6 v (high) or 0 v (low). The on or off condition of a circuit element varies with its function and is defined separately.

Turn On Sequence

3.69 The NORM./TEST switch must be in the NORM. position. This enables the receive message (RM) lead, XZAN-21, which connects to the auto on relay driver input.

3.70 The DAIF2/AAB interface turns on (0 v) the data terminal ready (DTR) lead, XZAN-35, if:

(1) Disconnect lead XZAN-24 is high (+6 to +54 v). This indicates a general ready condition at the printer; cabinet closed, some paper available for printing.

(2) Selectable lead XZAN-22 is low (0 v). This indicates that there is a predetermined amount of paper on the supply roll.

Note: If the paper supply is below the predetermined level, the selectable lead goes high (positive) and turns the DTR lead off (negative) before the printer answers a new data call. However, the selectable lead cannot turn off the DTR lead once a call has been established.

(3) The on-hook timer (OP1-6) is high. (OP1-6 is high when the timer is initially set.)

These three conditions result in highs at ML1-9, 10, and 11, causing a low at ML1-8. This reduces the conduction of Q3, causing its collector voltage to rise, and Q5 therefore saturates to produce the low at the DTR lead.

3.71 DTR on allows the data set to answer an incoming call. When the telephone circuit is complete, the data set grounds the RM lead, XZAN-21, turning on the printer. The low at XZAN-21 is applied to ML4-2, causing ML4-3 and ML4-4 to go high. This results in a low at ML4-6 and ML4-9, causing ML4-8 to go high. The high at ML4-8 releases timer OP1. When the printer turns on it grounds the ready lead, XZAN-30, which reduces the conduction of Q4 and therefore saturates Q6. This results in a low at the collector of Q6, which also appears at XZAN-31, the supervisory transmitted data (STD) lead. This lead may be used for reverse channel indication if the data set is so equipped.

3.72 The data carrier detector (DCD) lead,

XZAN-20, must be turned on (0 v) within 15 seconds after the RM signal has initiated the timing cycle of OP1. This low DCD signal forces ML4-6 high, causing ML4-8 to go low and thus discharging C3 to clamp the timer. DCD on also forces ML2-11 high to enable ML2-10 and ML3-10.

Note: If the timer is permitted to time out, the resultant low at OP1-6 will force ML1-9 high, causing Q3 to conduct heavily and Q5 to cut off, thus producing a high (off) on the DTR lead which causes the data set to drop the call.

### Receive Data

3.73 The timing lead, XZAN-18, turns on (0 v) and starts the character available timer.

Since the DCD signal removed the clamp on ML2-3 during turn-on, ML2-3 goes high. This

high is gated with the high at ML3-8 to produce a low at ML2-8, forcing ML2-6 high, and C2 begins to charge to this positive voltage. The unijunction transistor, Q1, fires from 1.8 to 4.0 milliseconds after the timing signal appears at XZAN-18. The positive pulse across R1 is applied to Q2, and the Q2 collector goes low. This low forces ML3-3 high, which forces ML3-11 and the character available (CA) lead, XZAN-19, (early design units only), low. This also forces ML3-6 high, and this high is gated with the high from ML2-3 to force ML3-8 low, ML2-8 high, and thus ML2-5 high. In early design units, this forces ML2-6 low, preventing another cycle of the character available timer. The CA pulse is approximately 20 microseconds long. In late design units, the low pulse from the collector of Q2 is gated into ML2-4 to keep the unijunction timer from turning off until one full character available pulse has been generated. After this occurs, ML2-4 will go high, forcing ML2-6 low and thus preventing another cycle of the character available timer. The CA pulse width is increased to a minimum of 30 microseconds with the aid of CR10 and C7. When the low-to-high transition occurs at ML3-2, ML3-1 is held low until C7 charges to the slicing level of ML3. This effectively increases the pulse width to about 80 microseconds. As in early design units, CA appears at XZAN19.

3.74 When the timing lead, XZAN-18, returns to high, ML2-3 goes low and forces ML3-8 high. This enables the ML2-9 input, and the generation of the CA pulse is complete. The timing lead must be low for at least 5 milliseconds and high for at least 20 microseconds for each character.

3.75 The eight input data leads, XZAN-3, 5, 6, 8, 10, 12, 14, and 16, must be low (zero) to produce marks (+6 v) at output leads XZAN-2, 4, 7, 9, 11, 13, 15, and 17. The input data leads must be open or above +3 v to produce spaces (0 v) at the outputs.

### Turn Off

3.76 When data transmission is completed, the DCD lead is opened, and the resultant high at ML4-5 causes ML4-6 to go low. This forces ML4-8 high, and the on-hook timer, OP1, is enabled. When the timer times out, OP1-6 goes low (zero), forcing ML1-8 high and turning off Q5. This opens the DTR lead (XZAN-35) to the data set, so the data set drops the call and opens the data set ready (DSR) lead, XZAN-21. ML4-3 goes low, forcing ML4-6 and ML4-8 low, resetting timer OP1. The interface is now ready to accept another call.

**Test Character Generation**

3.77 On late design units a test character generator circuit is located in the DAIF2 interface. Its purpose is to simplify cleaning of the recorder nozzles and electrodes by enabling the results of cleaning to be tested immediately, without waiting for an incoming message or connecting the DATS1 simulator. It does this by generating continuous W (or 2, with Baudot code in the figures mode) characters whenever the PAPER ALARM button on the control panel is depressed, whether an incoming message is being received or not.

3.78 Depressing the PAPER ALARM button supplies ground, through 3NO and 3C to pin 21 on the control panel connector, CP1. This signal, generate test character, is connected via DAIF/AA1-41 to XZAR-35, where it is connected to ML1-13 on test character generator card MC192 (TP322192). The output of this gate, ML1-11, will go high since gate ML2-8 is held low through strap A. This high causes ML2-2, XZAR-26, to go low, supplying T.R.M. to the receive message input of the printer drive, DAD/C209 (via DAIF/AA1-26), and card MC134, XZAN-21. This turns on the high voltage and permits printing.

3.79 The high on ML1-11 causes ML2-6 (XZAR-23) and ML2-10 (XZAR-21) to go low. These two leads, C.A. stop and blind, are connected to B23 and B27, respectively, on card MC134. The low on B23 (ML3-8) of card MC134 keeps any character available pulses from being generated. The low on B27 (ML5-10, ML5-13, ML6-10, ML6-13, ML6-5, ML6-2, ML5-2, and ML5-5) of card MC134 blinds the set from receiving any incoming data.

3.80 The high at ML1-11 of card MC192 also appears at ML302. This gate allows the test character generator card to generate a substitute character available pulse. The test character available (T.C.A.) pulses are generated with the aid of Q1, Q2, and their associated components. Capacitor C3 and diode D2 are used to increase the test character available (T.C.A.) pulse to a minimum of  $30 \mu$  sec. Capacitor C3 will effectively hold ML1-5 low longer by charging to the slicing level of ML1-6 with a low-to-high transition on ML1-4. Diode D2 is used to eliminate resistor R9 from the charging circuit of C1 and thus helps increase

the width of the T.C.A. pulse. The unijunction oscillator is constantly generating pulses but they do not appear at ML3-3 (XZAR-20) because there is normally a low on ML3-2 (not generating a test character).

When the PAPER ALARM button is 3.81 pushed, ML1-13 will go low, ML1-11 high and ML3-2 high. This high at ML3-2 permits the C.A. to appear at ML3-3 (XZAR-20). The test character is factory-programmed by cutting straps 1 to 7. Strap 1 is cut if the desired character has a spacing first bit. Strap 2 is cut if the desired character has a spacing second bit, etc. When ML1-11 goes high, ML1-3 goes low and ML2-12 goes high. This allows the input to gates ML3-6, ML3-8, ML4-3, ML4-6, ML4-8, ML4-11, and ML3-11 to sense the condition of straps 1 to 7. If the strap is closed, a ground will be sensed at the input of the gate thus causing a high (mark) at the output of its associated gate. If the strap is open, two highs will be sensed at the input of the gate and hence producing a low (space) at the output.

3.82 When the PAPER ALARM button is released, ML1-13 will go high thus permitting the next T.C.A., which is seen at ML1-9, to reset the flip-flop (ML1-11, ML1-8). Resistor R10 is a pull-up resistor used to help keep the flip-flop (ML1-11, ML1-8) from being set due to noise on the ML1-13 to switch contact lead. Capacitor C1 is also used to keep noise from setting this flip-flop. When ML1-11 is low, a small negative noise spike appearing on ML1-13 must be wide enough to overcome the R-C rise time of C1 in order to set the flip-flop (ML1-11, ML1-8) erroneously.

C. Discrete Calling Generator

3.83 The TP325200 discrete calling generator consists of a TP199570 signal generator assembly and a relay bracketassembly, mounted within the DAIF1 or DAIF2 module frame. The signal generator assembly has a 20 rpm, 117 v ac motor and clutch, a TP199580 programmable code disc, and a set of stationary sensing brushes. A dual wire spring relay and terminal strip are mounted on the relay bracket. When programmed, the discrete calling generator permits the printer to enable an unattended type 2 or type 5 DATASPEED sender equipped with an identically programmed recognizer.

3.84 Depressing the TRANS START pushbutton on the printer function strip (after the PRINTER ON light has come on) operates the discrete calling generator relay, placing the associated data set in the send or answer-back mode and engaging the clutch. This starts the code disc turning and generates the discrete 14bit code. When the code disc completes one revolution it stops and restores the data set to its original mode.

3.85 The TP325200 discrete calling generator

is almost identical to the TP199550 protected unattended transmitter modification kit for Type 2 DATASPEED Receivers. It differs from the TP199550 kit in that it mounts in the interface module instead of having its own frame and cabling and uses a positive instead of a negative voltage supply. There is no difference as far as operation with type 2 equipment. Refer to Section 592-806-101 for additional information. The discrete calling generator is also similar to the TP199784 station identifier for Type 5 DATASPEED Receivers. There are packaging and electrical differences, but operation with type 5 equipment is identical. Refer 592-808-101 for additional inforto Section mation.

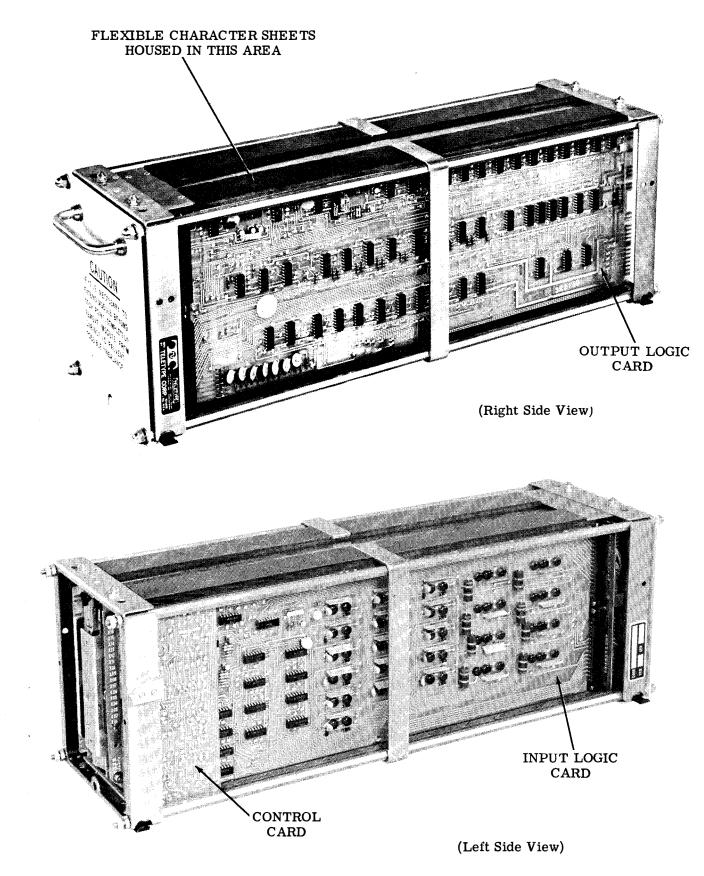

## CHARACTER GENERATOR

3.86 The character generator is a memory and logic system which translates incoming codes from the interface into the signals necessary for the printer drive to direct the generation of characters by the recorder. It controls both the tracing of each individual character and the spacing of characters on a line, plus additional functions such as line feed. The character generator is housed in the DAG module (Figure 7).

## A. General

3.87 The character generator receives digital

information input signals (seven bits for ASCII; five for Baudot) and a start signal from the interface, in parallel form. Together, these signals define a character. Each character is stored for 8 milliseconds while the logic selects and processes the appropriate memory subroutine. This consists of sequentially interrogating the memory while storing the character until the tracing drive processes it. When the character is printed the generator locates to the next printing position.

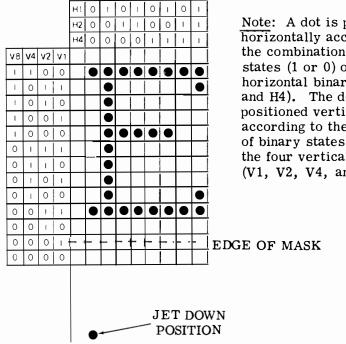

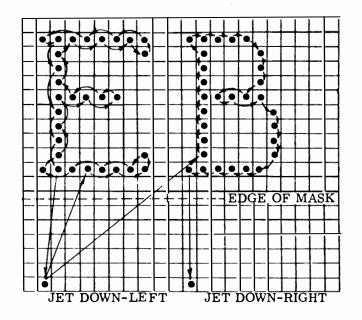

3.88 The character generator has provisions

for generating 64 different characters, with each character being composed of a maximum of 32 dot positions (Figure 8). Dot positions

(

(

(

(

(

(

Figure 7 - Character Generator (DAG) Module

are defined by up to 32 seven-bit words which control the actual tracing of the character, and the outputs of seven binaries, used to position characters on a line.

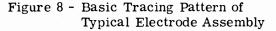

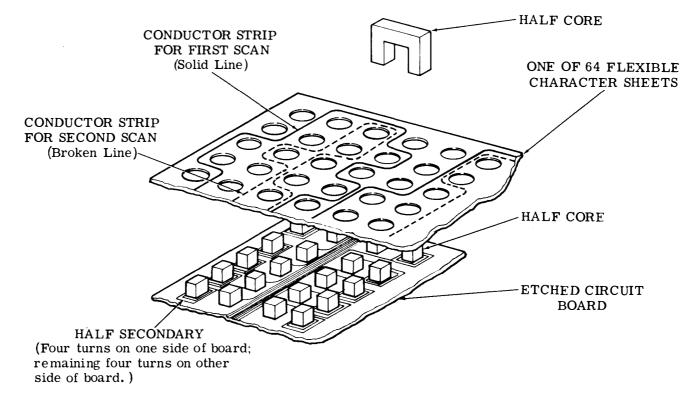

3.89 The memory consists of a matrix of 112 transformer cores together with input and output windings. Two U-sections make up a core and establish a closed magnetic circuit. The memory works on transformer action, with a primary of one turn and a secondary of eight turns. The primaries are on 64 flexible plastic etched circuit sheets 0.003 inch thick, one for each character. Each sheet has a unique conductor path which distinguishes it from the sheets for all other characters. A character sheet contains two separate conductors, as shown in Figure 9. Each conductor acts as a primary for half of a character, and the memory is scanned twice per character. As a result, the number of cores needed to store a character is reduced from 32 times 7, or 224, to 16 times 7, or 112. The secondaries are on an etched circuit card arranged in 16 groups of 7, one secondary for each core. Each group of seven secondaries produces the information for two dots of the character; one dot on the first scan and the other dot on the second scan.

**3.90** Depending on the memory program board and the character sheets it contains, the

memory can store up to 64 characters of ASCII, all of communications Baudot, or all of weather Baudot. The character generator code and individual character sheet part numbers are the same for all codes; variations are accommodated in the memory program board codes, DAG2/AAB, DAG2/AAC, and DAG2/AAE.

- 3.91 Power requirements for the character generator are as follows:

- 5.3 v to 7.3 v dc

- 41.5 v to 53.0 v dc

- 13 watts maximum power

3.92 There are two independent optional features in the character generator. The time required to feed out one line of paper when the PAPER ADVANCE button is depressed may be reduced from the standard 64 milliseconds to 32 or 16 milliseconds so that paper will be fed out two or four times as fast. Normally, CR initiates carriage return only and LF initiates line feed only, but the character generator may be programmed for simultaneous carriage return and line feed on receipt of CR (for ASCII only) or simultaneous carriage return and line feed on receipt of LF.

Figure 9 - Core Arrangement and Conductor Routing on Character Sheets

## B. Detailed Circuit Description

3.93 The detailed description of this unit is divided into seven parts: the line feed buffer and controls; the memory input buffer and controls; the timing signals; the character positioning binaries and associated gates; the memory drivers and controls; circuits peculiar to control functions; and programming for ASCII and Baudot codes.

3.94 For details of the circuitry, refer to wiring diagrams 8252/AAA/WD (character generator schematic), 8252/AAB/WD (ASCII program board), 8252/AAC/WD (communications Baudot program board), 8252/AAE/WD (weather Baudot program board), 322151 (MC151 input logic card), 322150 (MC150 output logic card), 322152 (MC152 ASCII control logic card), 322153 (MC153 Baudot control logic card), 303927 (EC927 ASCII program board), 303928 (EC928 Baudot program board), 303929 (EC929 output board assembly), and 8260WD (timing diagram).

3.95 The following discussion is directed toward ASCII operation. Therefore, a start signal and a seven-bit signal defining a character must be supplied to the generator from the interface. The start signal is referred to as the character available signal. It is nominally a low pulse of approximately 20 or 80 microseconds duration, as explained in 3.44 for serial interface and 3.73 for parallel interface.

Line Feed Buffer and Controls

3.96 The character available signal (a low at 201 of card MC151) controls the line feed buffer, shown on Sheet 2 of TP322151. It clears register ML2-5 through ML8-5 and simultaneously enables transfer gates ML2-2 through ML8-2 via a high signal generated by inverting gate ML1-13. Because the propagation time of this gate is about 10 nanoseconds, the transfer signal is high longer than the clear to the register is low. Utilizing this fact, one signal and one inverting gate are used to both clear and transfer information into the register. The purpose of this register is to supply the line feed mechanism with 12 milliseconds of operating time on receipt of a line feed signal. This exceeds the normal character time for printing functions (8 milliseconds) because of the cycling time required by the line feed mechanism. A line feed signal can be generated by any of three control characters as decoded by gate ML1-8, ML2-6, or ML1-6 on card MC152. These

control characters are line feed, vertical tab, and form feed, respectively. The line feed signal (which is the result of a wired OR connection of the above gates) drives a line feed network on card MC150 as described in 3.102 (c).

## Memory Input Buffer and Controls

3.97 This same character available signal

triggers a 4-millisecond monostable network, established by diodes CR1 and CR2 and transistor Q1, by setting a dc flip-flop (ML17-11, 6) on MC151 that reverse-biases diode CR3, permitting capacitor C1 to charge to the threshold of the network. When this point is reached, transistor Q1 saturates and flip-flop ML17-11, 6 is reset. The positive-going edge of this 4-millisecond signal is sensed by a differentiating network consisting of R7, C3, R8, R9, and Q3 and amplified by an emitter follower consisting of R43 and Q60. This signal, designated start of cycle (SOC) is nominally low for 4 microseconds and is used to clear the memory input buffer register, which consists of ML10-12 through ML16-12 on card MC151. Its transfer gates, ML2-8 through ML8-8, are simultaneously enabled by the inverted SOC signal (high) from gate ML1-8. The propagation time of this gate permits the transfer signal (high) to exist longer than the register clear signal (low), so that the signal first clears and then transfers information into the register. The purpose of the 4-millisecond delay is to allow for the 12-millisecond line feed time mentioned in 3.96. Thus, printing signals are delayed 4 milliseconds before they are processed by the character generator, whereas line feed signals are fed directly to the line feed circuitry and are allowed a duration of 12 milliseconds.

## Timing Signals

3.98 The SOC signal initiates the internal timing of the character generator. The timing elements include three monostable networks and a unijunction oscillator. There are 32 timing frames (250 microseconds each) within a character interval (8 milliseconds), and each timing frame defines the operations needed to print one dot. The first frame is initiated by the SOC signal, which also starts the unijunction oscillator. The oscillator initiates the remaining 31 frames. The three monostable networks will be referred to in the following discussion as the memory control monostable, the vertical control monostable, and the horizontal control monostable.

(a) The memory control monostable consists of ML22-12, ML17-8, CR4, CR5, CR6, C2, R4, R5, R6, and Q2 on card MC151. On receipt of the SOC signal (low on ML22-2) or the oscillator signal (low on ML22-1), dc flipflop ML22-12 and ML17-8 is set and diode CR6 is reverse-biased. This permits capacitor C2 to charge through resistor R6 to the threshold of this monostable network, which is established by CR4, CR5, and Q2. When this point is reached, transistor Q2 turns on and flip-flop ML22-12 and ML17-8 is reset. The output signal from this network is a high 10microsecond pulse. This signal is gated with the normal and inverted level 1 signals from the memory input buffer register (ML10-6 and ML10-8) via NAND gates ML1-3, 6 and inverters ML9-8, 6. Output signals MRL #1 (memory register level 1) and MRL #1 (memory register level 1 inverted) are thus always opposite in sign (high, low or low, high). They are supplied to the X-drivers as a sequence of 32 ten-microsecond pulses. The output of the X-drivers is used to read the memory (via program board EC927) as described in 3.99. The memory output buffer register on MC150 is also cleared as soon as the reading of the memory begins. This clear signal (MC) is propagated through three gates: ML1-3 or ML1-6, and ML17-3 on MC151 and ML29-8 on MC150. This propagation delay is necessary to insure that signals in the vertical and horizontal registers (3.98(b) and (c))are not disturbed by new information being processed by the memory output buffer register.

(b) The vertical control monostable consists of CP7 through CP0 P11 through P12

of CR7 through CR9, R11 through R13, C2, and Q4, all on MC150. The SOC signal produces a low at ML3-1, forcing the vertical register control lead (ML3-12) high. This high is applied to ML29-1, and the resulting low at ML29-3 inhibits the vertical transfer gates (ML41-3, ML42-11, ML44-3, and ML45-11). With ML3-12 high, the vertical control monostable begins to time out. After approximately 20 microseconds, Q4 conducts and its collector voltage goes low, forcing ML4-11 high. This high forces ML3-12 low, enabling the vertical transfer gates. Information stored in the vertical portion of the memory output register (ML4-11, ML42-3, ML44-11, and ML45-3) is now transferred to the vertical register, and appears at ML40-8, ML43-6, ML43-8, and ML46-6. This information remains on the output leads of the vertical register (V1, V2, V4, and V8) for the

remainder of the 250-microsecond timing interval.

(c) The horizontal control monostable consists of CR4 through CR6, R8 through R10, C3, and Q5, all on MC150. This circuit operates in essentially the same manner as the vertical control monostable, but produces a 200 microsecond delay, compared to the 20-microsecond delay of the vertical monostable. (The additional 180 microseconds compensates for the time it takes the ink droplets to move from the vertical deflection electrode to the horizontal deflection electrode on their way to the platen.) The SOC signal produces a low at ML3-4, forcing the horizontal register control lead (ML3-6) high. This high is applied to ML29-5, and the resulting low at ML29-6 inhibits the horizontal transfer gates (ML36-11, ML38-3, and ML39-11). With ML3-6 high, the horizontal monostable begins to time out. After approximately 200 microseconds, Q5 conducts and its collector voltage goes low, forcing ML4-3 high and ML3-6 low. The low at ML3-6 enables the horizontal transfer gates. Information stored in the horizontal portion of the memory output register (ML36-3, ML38-11, and ML39-3) is now transferred to the horizontal register, and appears at ML37-6, ML37-8, and ML40-6. As explained for the vertical register, this information remains on the output leads (H1, H2, and H4) for the remainder of the 250-microsecond timing interval.

(d) As mentioned, the SOC signal starts the 250-microsecond oscillator, which consists of CR1, R2 through R7, C1, Q1, and Q2. The SOC signal produces a low at ML3-11, forcing ML3-8 high and latching ML4-6 low. This low, applied to the base of Q3, cuts off Q3 and produces a high at its collector. C1 begins to charge through R2 and R7, until its voltage reaches the firing point of Q2. When the UJT fires, C1 discharges rapidly through R6, producing a positive pulse across R6. This pulse is applied through R3 to the base of Q1, which conducts heavily to produce a negative-going pulse at its collector. C1 quickly discharges to a point where it can no longer maintain conduction of Q2, which then cuts off. C1 begins to charge again, and the cycle is repeated. As long as ML4-6 remains latched, the oscillator continues to generate pulses at a 250-microsecond rate. The pulses (lows) are applied to ML3-2 and ML3-3, producing inverted pulses (highs) at ML3-12 and

ML3-6 to control the vertical and horizontal registers. They are also applied to ML22-1 on MC151 to trigger the memory control monostable. The pulses at ML3-6 also serve as a clock for ML5-2, the clock pulse input of the first Z-driver binary. On the 31st pulse after the SOC pulse, ML9-9 delivers a high to ML10-5, causing ML10-6 to go low and ML4-8 to go high. This high is applied to ML2-11, forcing ML2-8 low. The low at ML4-4 resets the latch, forcing ML4-6 high and turning on Q3 so that its collector voltage goes low and prevents further oscillations.

Character Positioning Binaries

3.99 A ripple counter of seven binaries on card MC150 controls the positioning of characters on a line. These binaries are designated ML11 through ML17. Their ultimate outputs to the printer drive are five group signals (A, B, C, D, and E) and seven binary signals (L/R, B7, B7, B8, B8, B9, and B9), which together determine all 80 character positions on a line.

(a) The last three binaries, ML15 through ML17, drive five decoding gates: ML33-8, ML34-6, ML34-8, ML35-6, and ML35-8. The outputs of these gates are inverted by gates ML47-6, ML47-8, ML48-6, ML48-8, and ML49-8 and presented to the spacing drive portion of the printer drive as groups E, D, C, B, and A, respectively. They control five intervals on a line which are in turn divided into sixteen character positions, determined by the last six binary signals. The five decoding gates are also controlled by a network consisting of gates ML22-6 and ML22-8 on card MC151. These two gates monitor the 4-millisecond interval as established by the 4-millisecond monostable, the printing interval as established by the oscillator reset gate, and a nonprint or horizontal tab mode as established by decoders on MC152. Consequently, the five MC150 decoding gates will be inhibited during nonprint characters or intervals.

(b) The inverted output of the first binary, ML11, is coupled to the tracing drive portion of the printer drive via line driver ML30-6 as L/R, and the inverted and normal outputs of the next three binaries, ML12 through ML14, are coupled to the spacing drive portion via line drivers ML31-6, ML30-8, ML32-6, ML31-8, ML33-6, and ML32-8 as B7, B7, B8, B8, B9, and B9, respectively. These last 6 binary signals determine 16 character positions which, together with the 5 group signals, define the 80-characterline. L/R is used by the tracing drive to control the character position — left or right — in which one of the 40 ink jets will print. (B7 and  $\overline{B7}$  are also connected to vertical switches in the tracing drive.)

(c) A nonprint condition inhibits the stepping

of the binaries. This print inhibit condition can be generated either by an incoming code that defines a nonprint character (and is decoded on MC152) or the operation of the paper advance network. Should either of these conditions exist, gate ML10-3 is inhibited, and binary ML9 is inhibited from stepping binaries ML11 through ML17. The source of the print inhibit signal, located on MC152, is described in 3.103 (a). The paper advance network works in conjunction with these seven binaries and must have control of the binaries at all times. Therefore, should a print inhibit exist the binaries can still operate via an alternate gate ML10-11 that will be enabled when the paper advance network is triggered. This circuit is described in 3.102 (a).

## Memory Drivers and Controls

3.100 A matrix of 16 X-drivers and 4 pairs of Y-drivers on MC151 allows the selection of any one of the 64 character sheets in the memory. The 16 X-drivers decode bit levels 1 through 4 of the memory input buffer register. The 4 Y-driver pairs decode the last three levels of this register. Therefore, any character information in this register will select only one X-driver and one pair of Y-drivers, which in turn will select only one character sheet in the memory. Each Y-driver in conjunction with an X-driver produces the information for 16 dots. Therefore, the Y-driver pair and this X-driver will produce a maximum of 32 dots necessary to print a character. When a Y-driver is enabled, its output rises to +48 volts for half the print cycle (4 milliseconds). A binary, ML9 on MC150, produces the controlling signals (B5 and  $B\overline{5}M$ ) that determine which Y-driver of any Ydriver pair is to be on and for how long. The X-driver is enabled by the input signals and by a sequence of 32 ten-microsecond clock pulses from gate ML9-8 or ML9-6 on MC151, as described in 3.98 (a). When an X-driver is enabled, its output is grounded and permits current to flow through one sheet.

**3.101** By pulsing the memory and then stepping the 16 Z-drivers, ML21-6 through ML28-8 on MC150, the information for 16 dots is sequentially read out. The control of these Z-drivers is a function of four binaries, ML5 through ML8 on MC150. As information for the positioning of each dot is read from the memory (in parallel), it is stored in the memory output buffer register ML45-3, ML44-11, ML42-3, ML41-11, ML39-3, ML38-11, and ML36-3. This information will remain in the register until the memory is pulsed again. It is then selectively applied to another set of registers. The first register stores vertical information. It consists of ML46-6, ML43-8, ML43-6, and ML40-8 and behaves as a register for 20 microseconds from the time the memory is pulsed. After this interval, this register behaves as a set of inverting gates monitoring the information in the memory output buffer register. Horizontal information is handled identically to vertical information, with one exception. The horizontal register, ML40-6, ML37-8, and ML37-6, behaves as a register for 200 microseconds after the memory is pulsed and as a set of inverters for the remaining 50 microseconds of each character. A jet down signal (JD) is also supplied via NAND gate ML46-8 and diode CR14, which monitors the outputs of the vertical register and the inverted vertical control monostable output from ML29-3, and NAND gates ML1-8 and ML1-11. On late design units, the print interval signal from ML2-8 is connected (via diode CR26) to the JD signal output to hold jet down on at all times when the set is not printing, even if noise spikes should set any one of the vertical register latches. These eight signals -V1, V2, V4, and V8 from the vertical register; H1, H2, and H4 from the horizontal register; and JD from ML1-8 and ML1-11 — are supplied to the tracing drive portion of the printer drive, along with L/R, B7, and  $\overline{B7}$ , to control the racing of each character.

## **Control Function Circuits**

3.102 Three circuits on MC150 control modes other than those associated with the racing and spacing of characters: The paper dvance circuit, the carriage return circuit, and he line feed circuit.

(a) The paper advance circuit consists of a dc flip-flop, ML1-6 and ML1-3, which is controlled by the PAPER ADVANCE button on the function strip. When this button is operated, a low signal changes the state of the flip-flop, enabling gate ML1-11 and al-

lowing the character positioning binaries, ML11 through ML17, to step at the character rate as determined by the oscillator and binaries ML5 through ML9. By programming the input (422) of gate ML19-12 to the output of either binary ML12 (416), ML13 (412), or ML14 (408), the paper advance will operate at a 16-, 32-, or 64-millisecond rate. Since gate ML19-3 is enabled and the oscillator that controls character time enabled by a signal via ML17-3 and ML3-8, binaries ML11 through ML17 will step at the character rate (8 milliseconds) until the programmed position is located. At this instant, the line feed and carriage return networks are operated via gate ML19-11, and binaries ML11 through ML17 are reset, repeating this operation. Flip-flop ML1-1 is reset by the low signal from line feed driver ML20-6.

(b) A carriage return signal resets the character-positioning binaries to a quiescent state defined as the first character position on a line. The carriage return circuit consists of ML18-8, ML19-6, and ML20-8. Four inputs are capable of triggering this circuit: The carriage return or line feed signal (119), brought in if the charactergenerator is programmed for line feed on receipt of carriage return or carriage return on receipt of line feed; the output of the carriage return decoder, ML2-8 on MC152 (123); the output of the paper advance circuit, via gate ML19-11; and the output of the automatic carriage return and line feed circuit from gate ML2-6, which senses the binary condition (normal output of ML11, ML15, and ML17 high) indicating that 81 characters have been received without a carriage return or line feed (two characters are lost when this condition occurs). Any of these signals will set flip-flop ML18-8 and ML19-6 and cause a carriage return by placing a low on the set direct leads, SD (pins 5), of binaries ML11 through ML17. This flip-flop and the line feed flip-flop described in the following paragraph are reset by the low signal from oscillator Q1 on MC150.

(c) The line feed circuit consists of a dc flip-flop, ML18-6 and ML19-8, and gate ML20-6. This circuit can be triggered by a signal from the line feed decoder, ML1-8, on MC152 (125); the CR or LF signal (119), brought in if the character generator is programmed for line feed on receipt of CR or carriage return on receipt of LF; the output of the automatic CR/LF gate, ML2-6; and the

#### SECTION 578-500-111

output of the paper advance network via gate ML19-11. The output of this circuit, LF (low), is connected to the ink heater and line feed bracket assembly.

Programming for ASCII and Baudot Code

3.103 ASCII code was assumed throughout the preceding description of the character generator. This required that it contain control card MC152 and program board EC927. In a character generator for Baudot code, these components are replaced by control card MC153 and program board EC928. Operation of these codesensitive components is as follows: