# 0969-090-6010 (a/so)

A-5336

ſ

AUS 8 1980

SPCC LIBR.....

Statistics of the second

INSTRUCTION MANUAL FOR TELEGRAPH SIGNAL ANALYZER DIGITECH MODEL DT-603-3

\* -

0969-200-1010

### APPROVAL AND PROCUREMENT RECORD PAGE

APPROVAL DATA FOR: NAVSHIPS \_\_\_\_\_0969-200-1010\_\_\_\_

TITLE OF MANUAL: TELEGRAPH SIGNAL ANALYZER MODEL DT-603-3

APPROVAL AUTHORITY: SupShip Thirteen 165'PGM/5600 Ser. 625-536/1742 Dtd. 15 Mar. 1967

| CONTRACT OR<br>PURCHASE ORDER | SHIPS<br>APPICABLE | QUANTITY OF<br>MANUALS | QUANTITY OF<br>EQUIPMENT | BUILDING<br>YARD                      |

|-------------------------------|--------------------|------------------------|--------------------------|---------------------------------------|

| 3PGM 4058<br>NObs 4853        | PGM88, 89,90       | 5                      | 3                        | Tacoma Boat-<br>building Co.,<br>Inc. |

|                               |                    |                        | •                        | 1                                     |

**REMARKS:**

DATE 4/6/67

CERTIFICATION: It is hereby certified that NavShips 0969-200-1010 to be provided under purchase order 3PGM 4058 has been approved by the approval data shown above.

Ernest E. Courchene, Jr., President DIGITECH, INC. 66 Grove St. RIDGEFIELD, CONN. 06877 MFR. CODE: 14031

CHANGE NO.

#### ERRATA FOR INSTRUCTION MANUAL FOR TELEGRAPH SIGNAL ANALYZER DIGITECH MODEL DT-603-3

#### DRAWINGS

Figure 8A - Change 5R6, 680 ohms to 700 ohms

Figure 10 - Fg1-2, Correct Resistor Value R1 & R28 from 3900 ohms to 1800 ohms.

Fgl-2, Correct Transistor Value Q1 & Q2 from 2N404 to 2N1300

Fal-2, Correct Capacitor Value C21 from 83 mmf to 150 mmf

Figure 16 - Ge4-2, Correct Transistor Value Q2 from 2N404 to 2N1300

Figure 17 - Add C26, 150 mmf across R24

LIST OF REVISED PAGES:

| 1-3 | 7_2 | 7-5 |

|-----|-----|-----|

| 4-1 | 7-3 | 7-6 |

| 5-7 | 7-4 | 8-3 |

DIGITECH, INC. 8/3/66 Revision #1

#### PAGE 1 of 1

### TABLE OF CONTENTS

(

(

| CHAPTER 1 | INTRODUCTION                                                                                                                                          | <u>PARAGRAPH</u>                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|           | Scope                                                                                                                                                 | 1-1<br>1-2<br>1-3<br>1-4<br>1-5  |

| CHAPTER 2 | UNPACKING AND INSTALLATION                                                                                                                            | PARAGRAPH                        |

|           | Unpacking and checking                                                                                                                                | 2-1<br>2-2                       |

| CHAPTER 3 | OPERATION                                                                                                                                             | PARAGRAPH                        |

|           | Chart of Operating Controls, Indicators                                                                                                               | 3-1                              |

|           | and Connectors                                                                                                                                        | 3-2                              |

| CHAPTER 4 | OPERATOR MAINTENANCE AND ALIGNMENT                                                                                                                    | PARAGRAPH                        |

|           | Fuse Sizes and Locations.Crystal FrequenciesAdjusting the MeterAdjusting the INPUT Circuit                                                            | 4-1<br>4-2<br>4-3<br>4-4         |

| CHAPTER 5 | THEORY OF OPERATION                                                                                                                                   | <b>PARAG</b> RAPH                |

|           | General                                                                                                                                               | 5-1<br>5-2<br>5-3<br>5-4         |

|           | Circuits-Selected Transition<br>Assembly 8 - Transfer Pulses - Character Timing<br>Assembly 6 and 4 - Power Supply<br>Assembly 9 - Crystal Oscillator | 5-5<br>5-6<br>5-7<br><b>5-</b> 8 |

| CHAPTER 6 | CORRECTIVE MAINTENANCE                                                                                                                                | PARAGRAPH                        |

|           | General                                                                                                                                               | 6-1<br>6-2<br>6-3<br>6-4<br>6-5  |

|           | f. Transfer Circuit<br>g. Register Circuits<br>h. Peak Logic Circuits                                                                                 |                                  |

### CHAPTER 7

CHAPTER 8

# PARTS LIST

| PARTS LIST             |   | PARAGRAPH         |

|------------------------|---|-------------------|

| General                | • | 7-1<br>7-2<br>7-3 |

| SYNCHRONIZING ADAPTER, |   | PARAGRAPH         |

# MODEL SA-3 (OPTION) 8\_1

| Purpose and Use     | 8-1 |

|---------------------|-----|

| Theory Of Operation | 8-2 |

| Installation        | 8-3 |

| Maintenance         | 8-4 |

| Parts List          | 8-5 |

|                     |     |

2 11--

### LIST OF ILLUSTRATIONS, DT-603-3

. ÷,•

FIGURE

(

(

### TITLE

| 1 200100    |                                             |

|-------------|---------------------------------------------|

| 1           | Front Panel View                            |

| 2           | Inside View - Assembly Location             |

| 2<br>3<br>4 | Typical Logic Circuits                      |

| 4           | Types Of Distortion                         |

| 5           | Block Diagram, DT-603-3                     |

| 6A          | Assembly No. 1 Diagram, DT-603-3            |

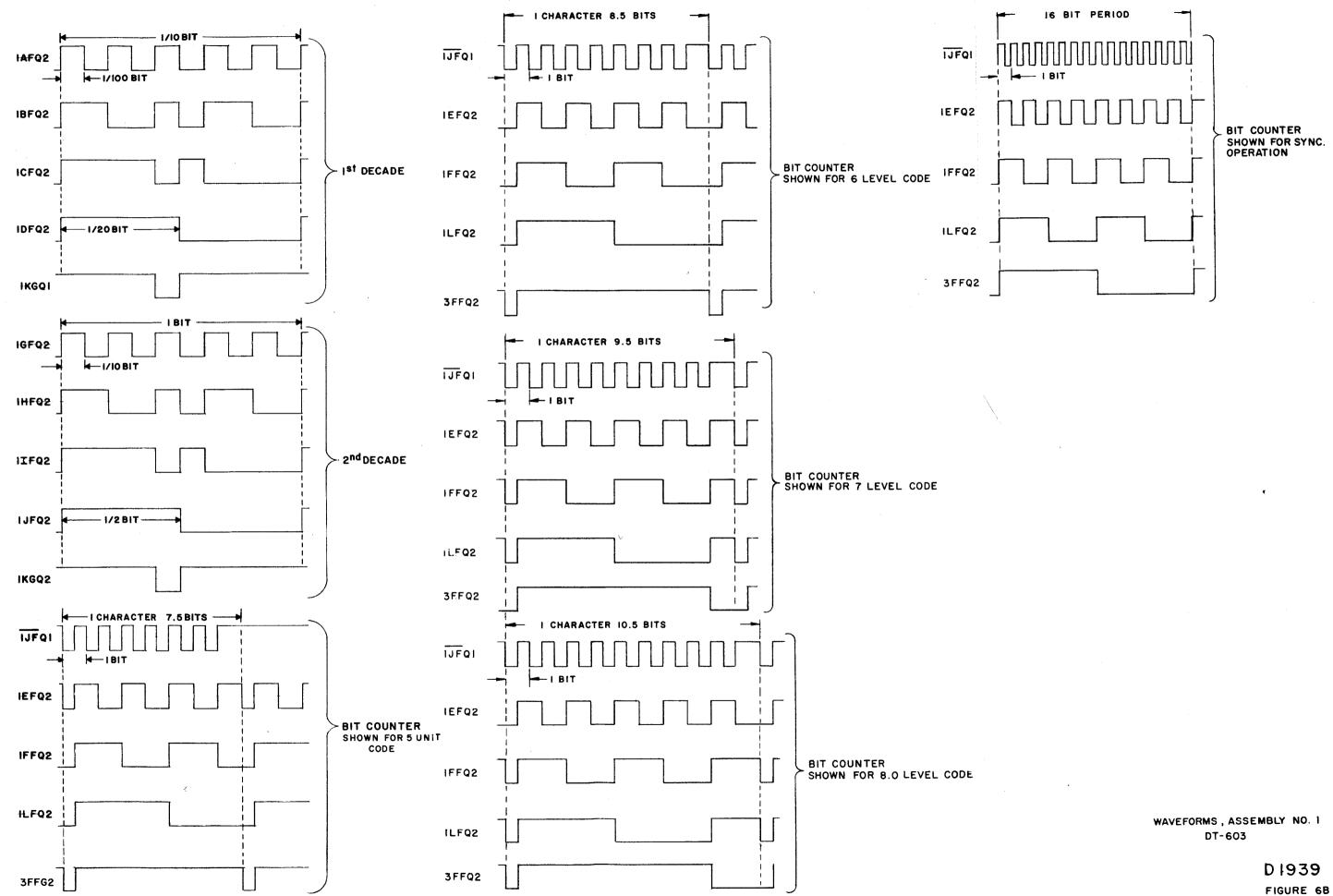

| 6 <b>B</b>  | Waveforms, Assembly No. 1                   |

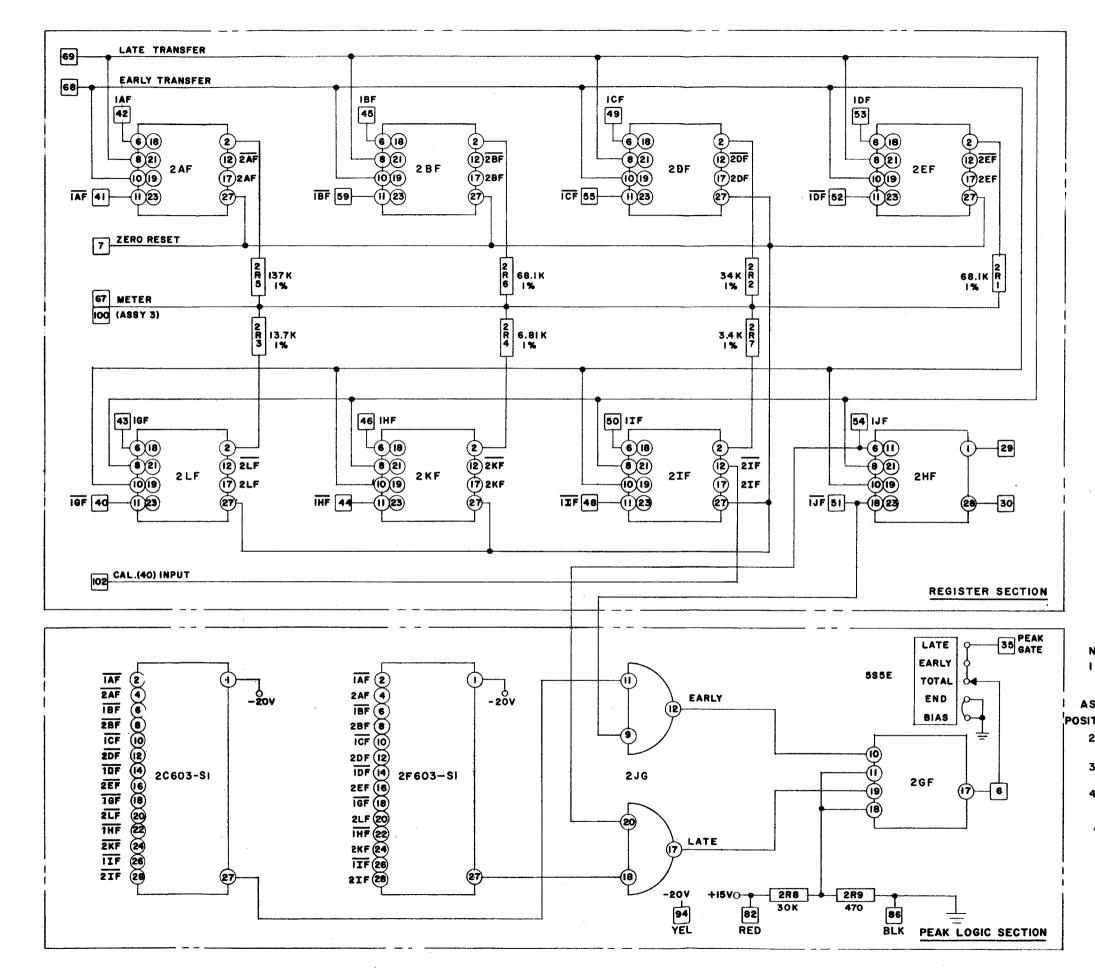

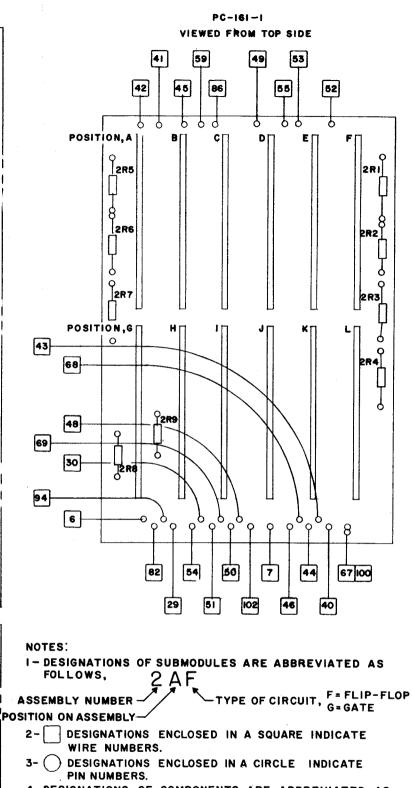

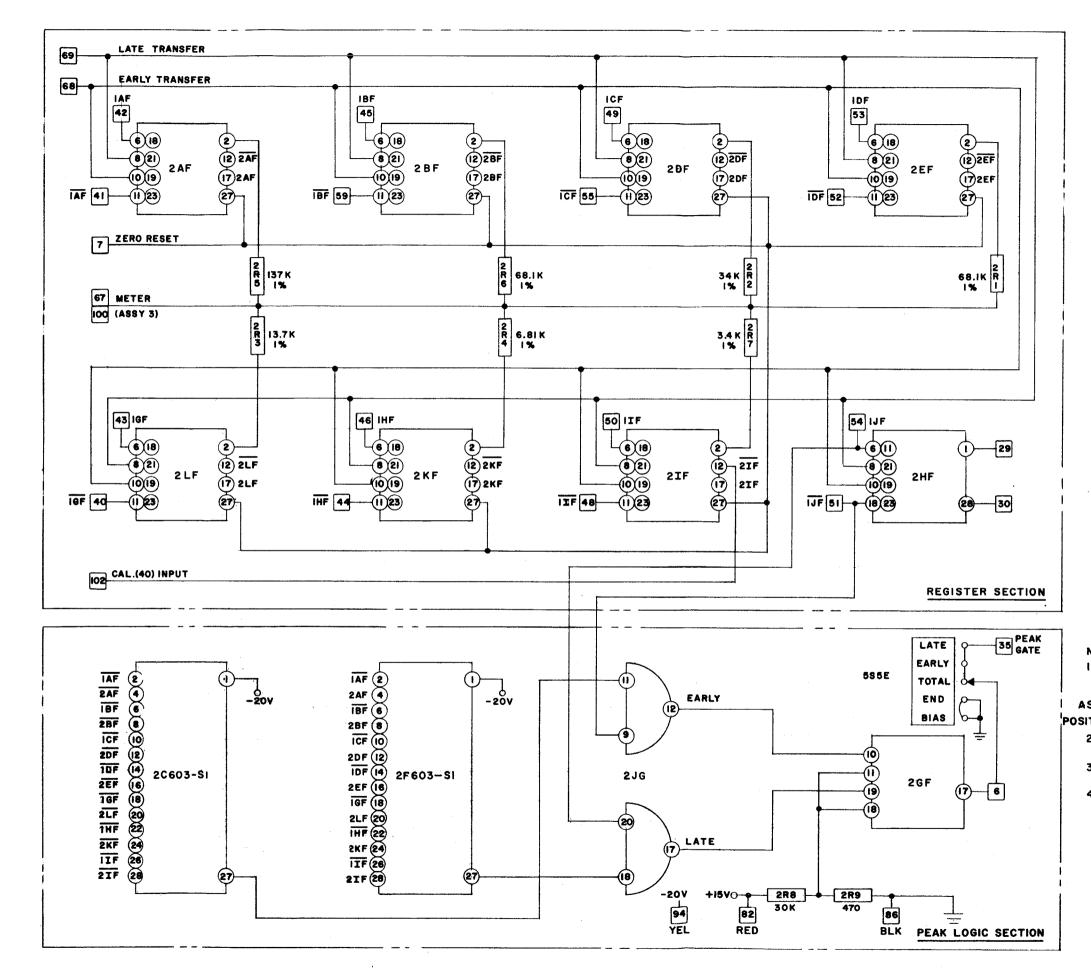

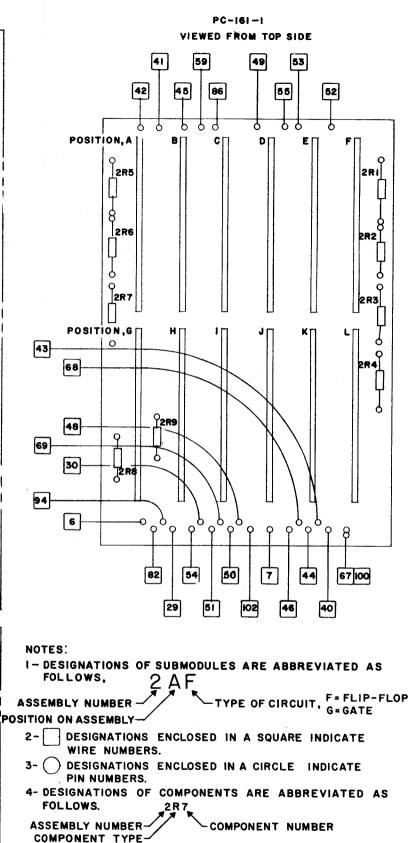

| 7A          | Assembly No.2 Diagram, DT-603-3             |

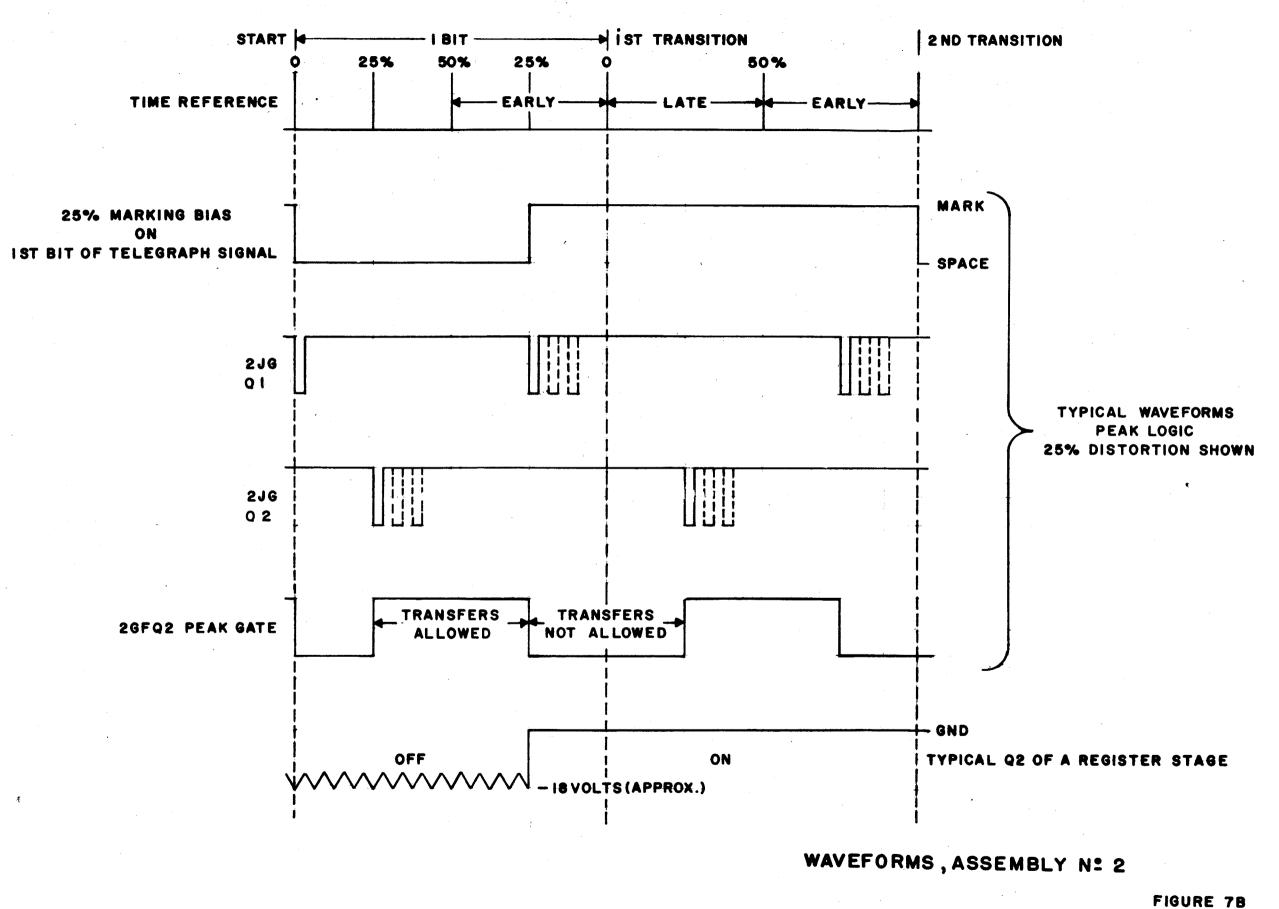

| 7B          | Waveforms, Assembly No. 2                   |

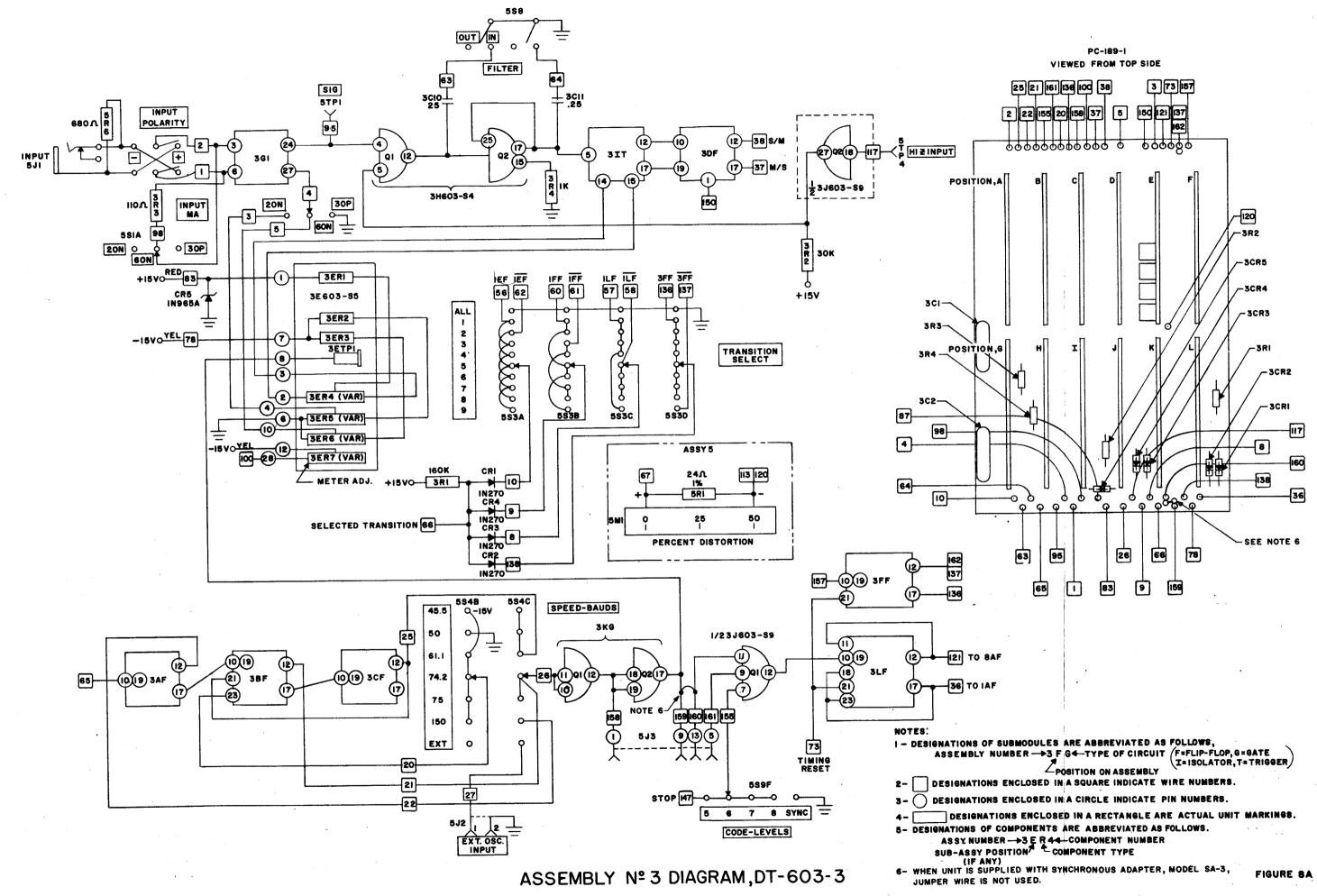

| 8A          | Assembly No. 3 Diagram, DT-603-3            |

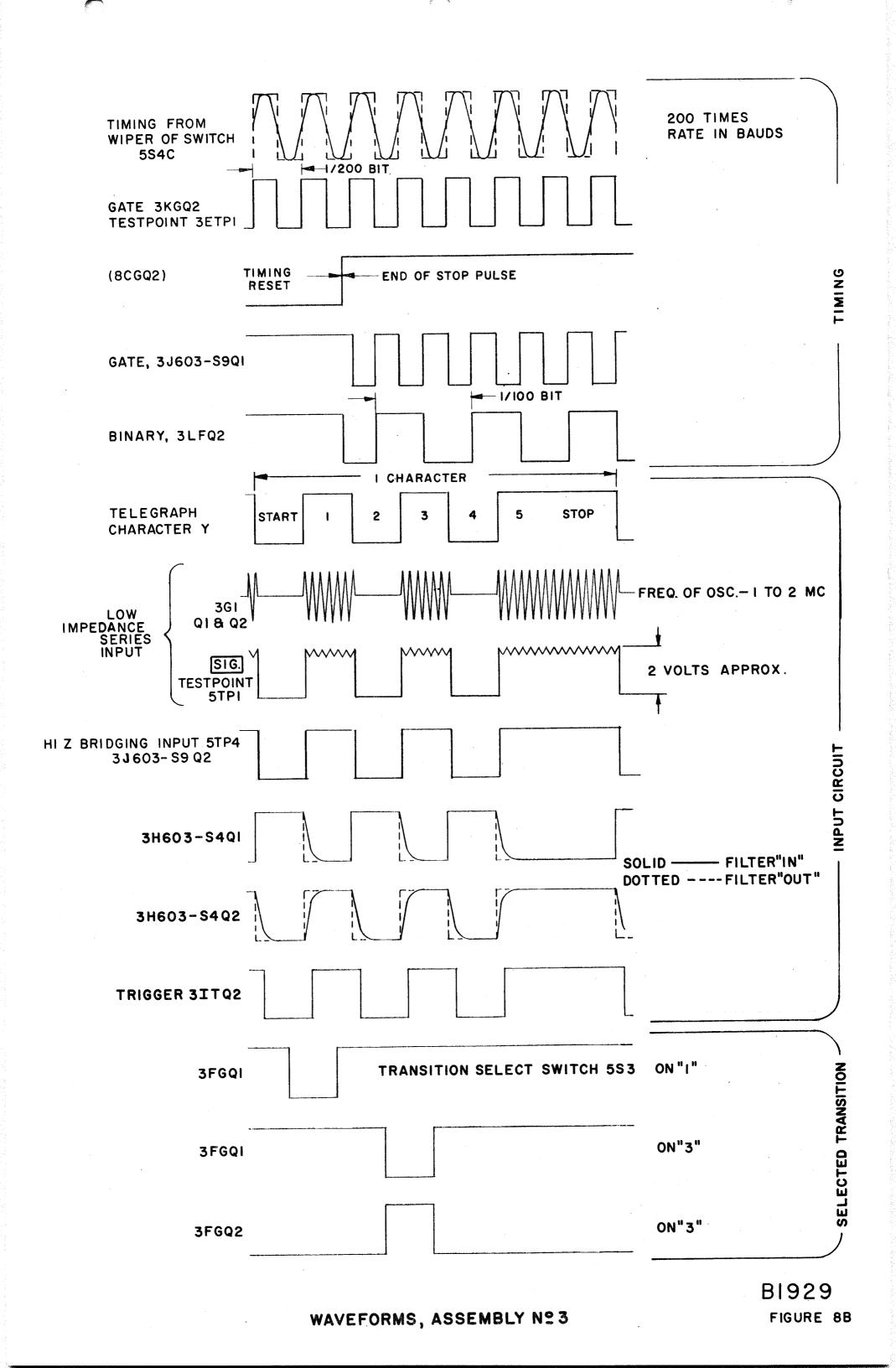

| 8B          | Waveforms, Assembly No. 3                   |

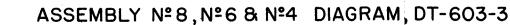

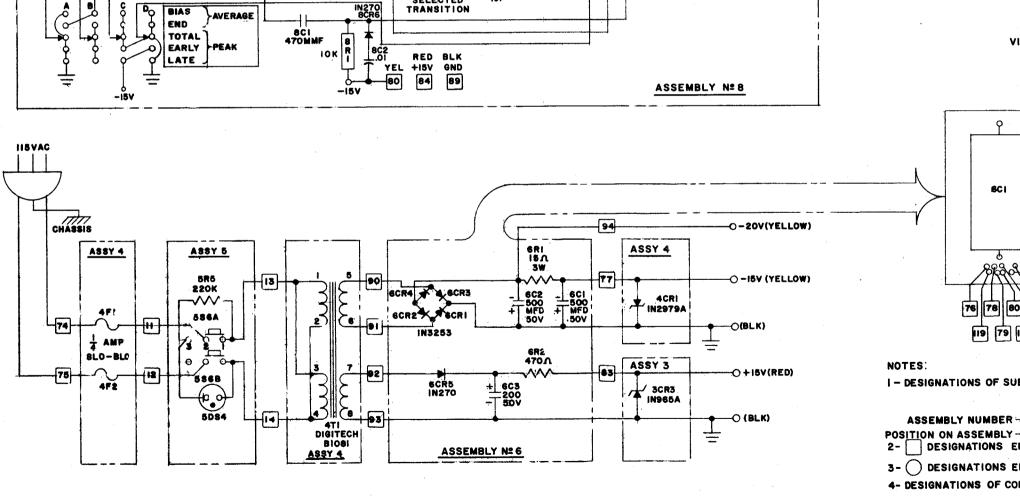

| <b>9A</b> · | Assembly No. 8 No.6 & No.4 Diagram DT-603-3 |

| 9B          | Waveforms, Assembly No.8                    |

| 9C          | Crystal Oscillator, Assembly No. 9          |

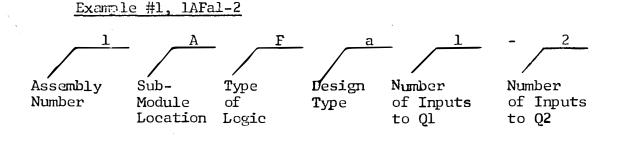

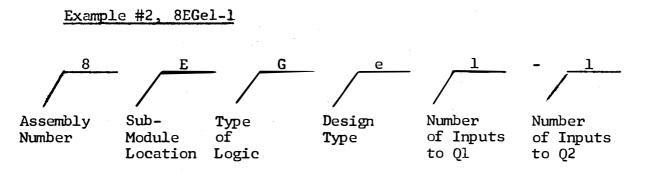

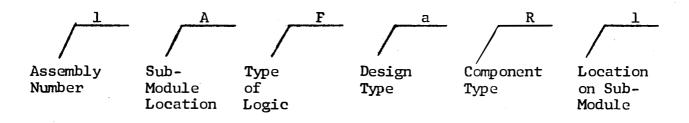

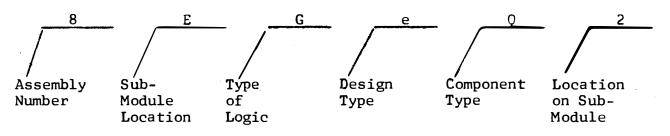

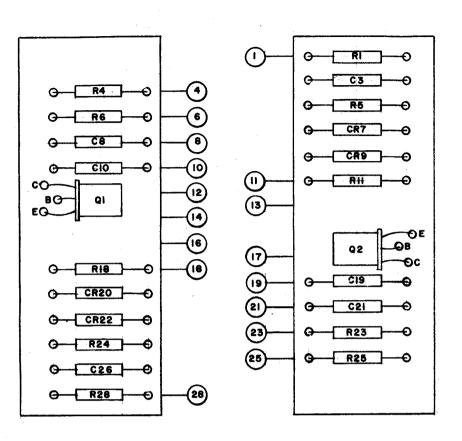

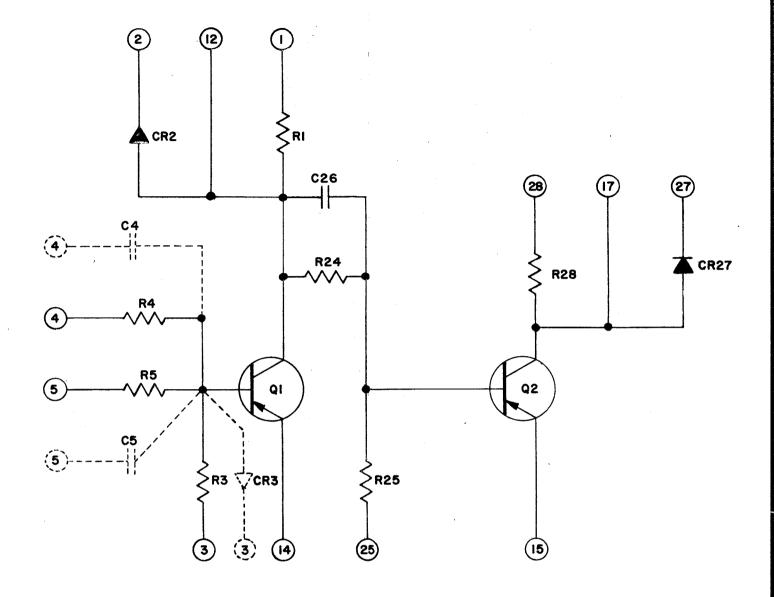

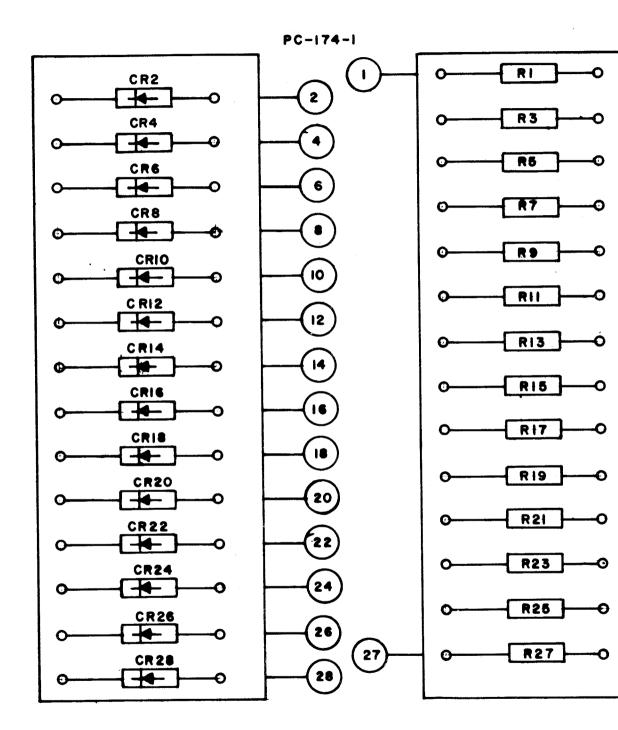

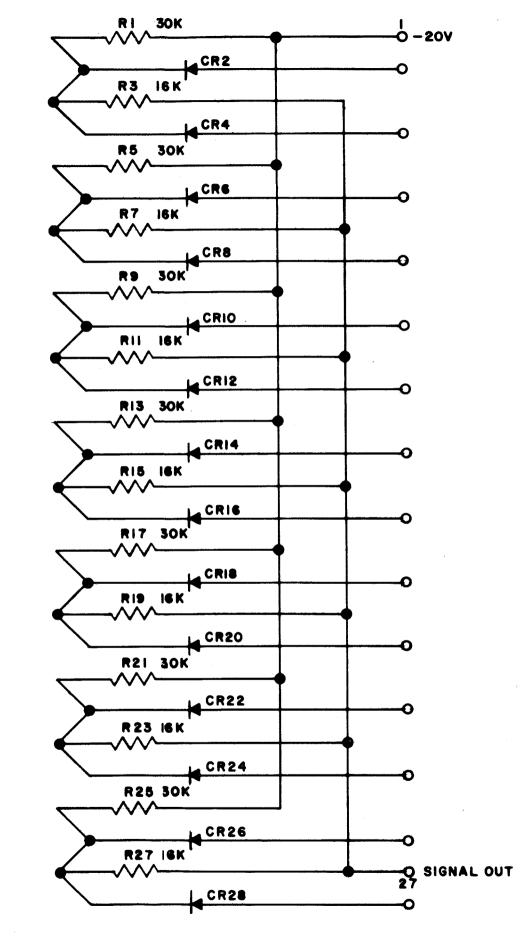

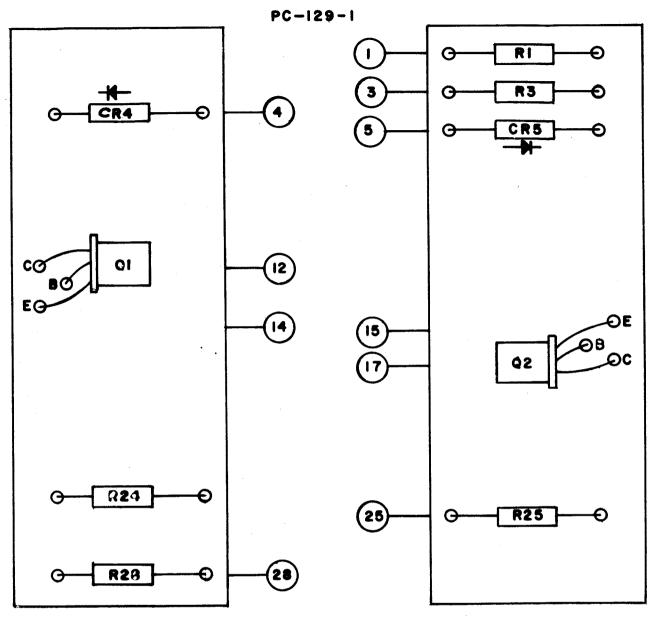

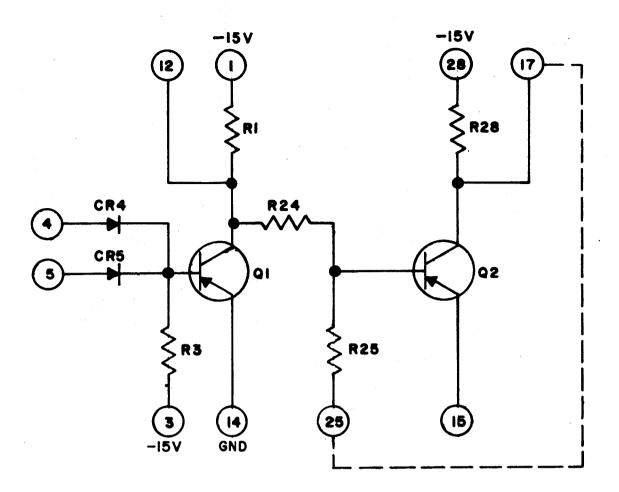

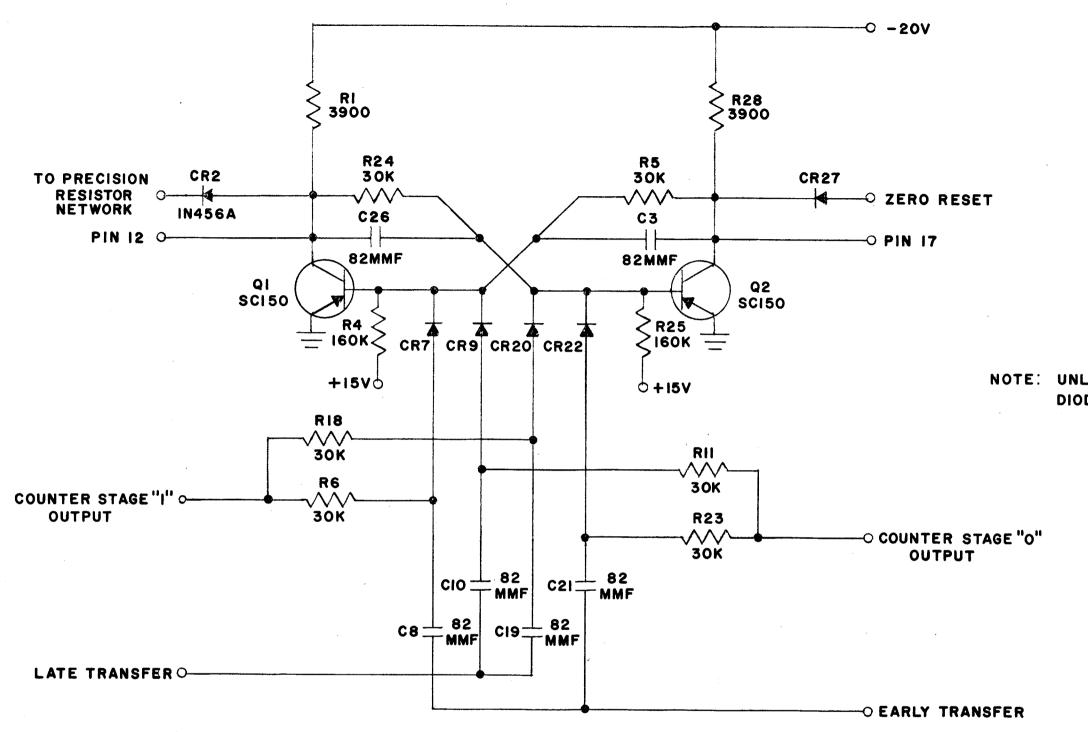

| 10          | Submodule Type F, Binary (Flip-Flop)        |

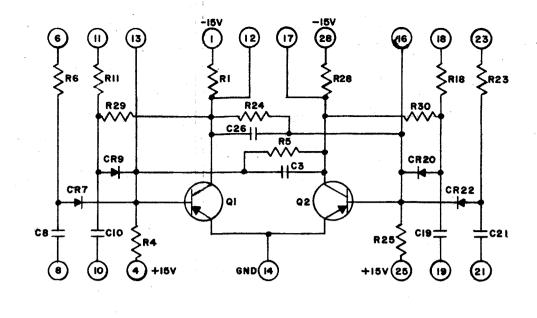

| 11          | Submodule Type G, Gate                      |

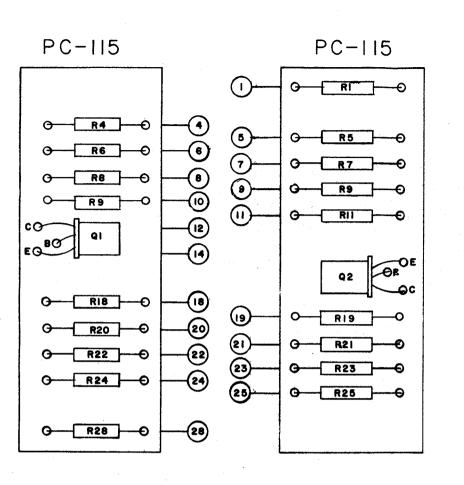

| 12          | Submodule Type Tb & Tc, Trigger             |

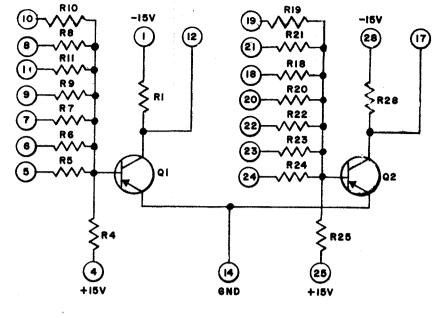

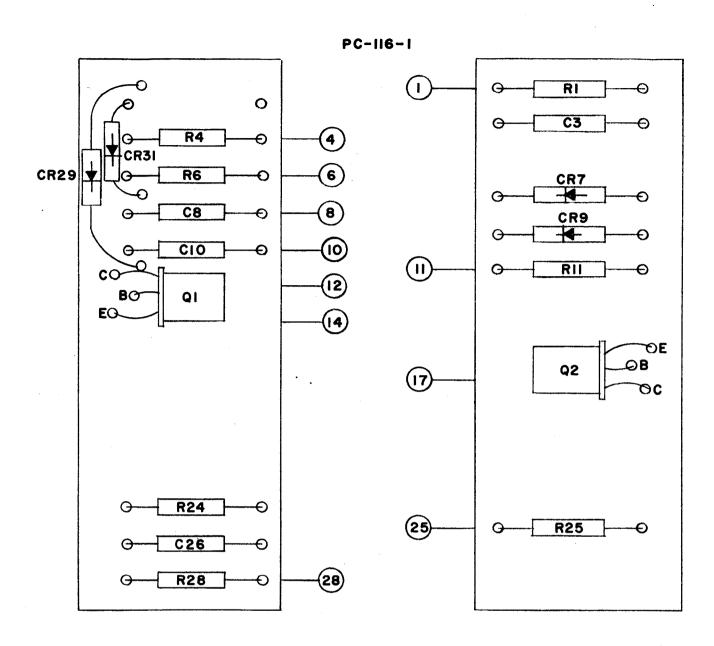

| 13          | Submodule Type Ib, Isolator                 |

| 14          | Submodule Type 603-S1, Special              |

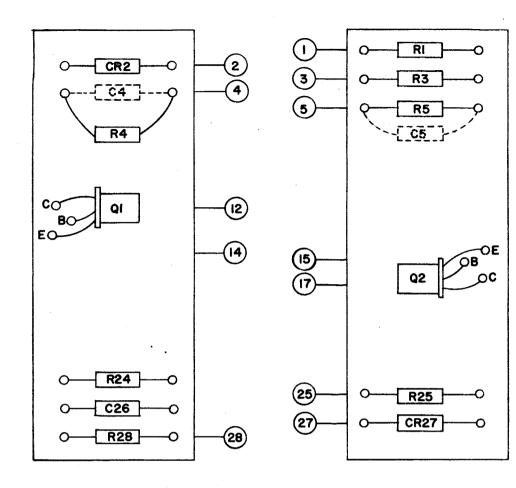

| 16          | Submodule Type 603#S9, Special              |

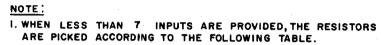

| 17          | Submodule Type 603-S4, Special              |

| 18          | Register Stage, Schematic Diagram           |

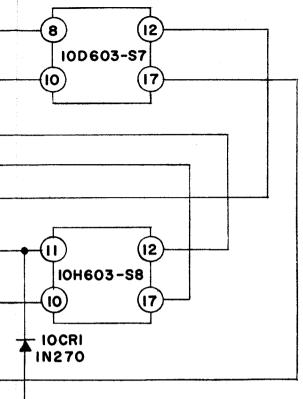

| 19          | Submodule Types 603-S7 and 603-SS           |

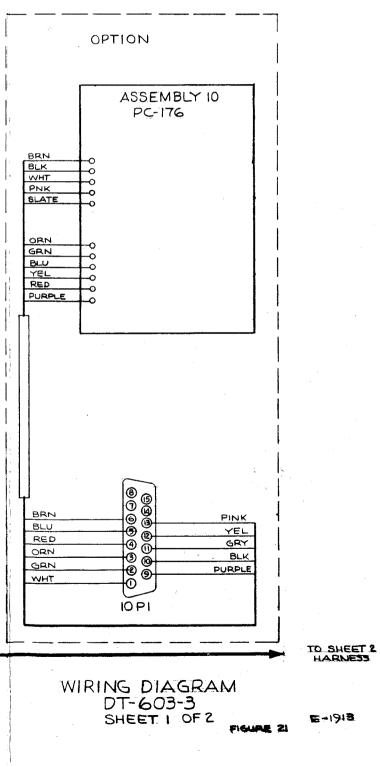

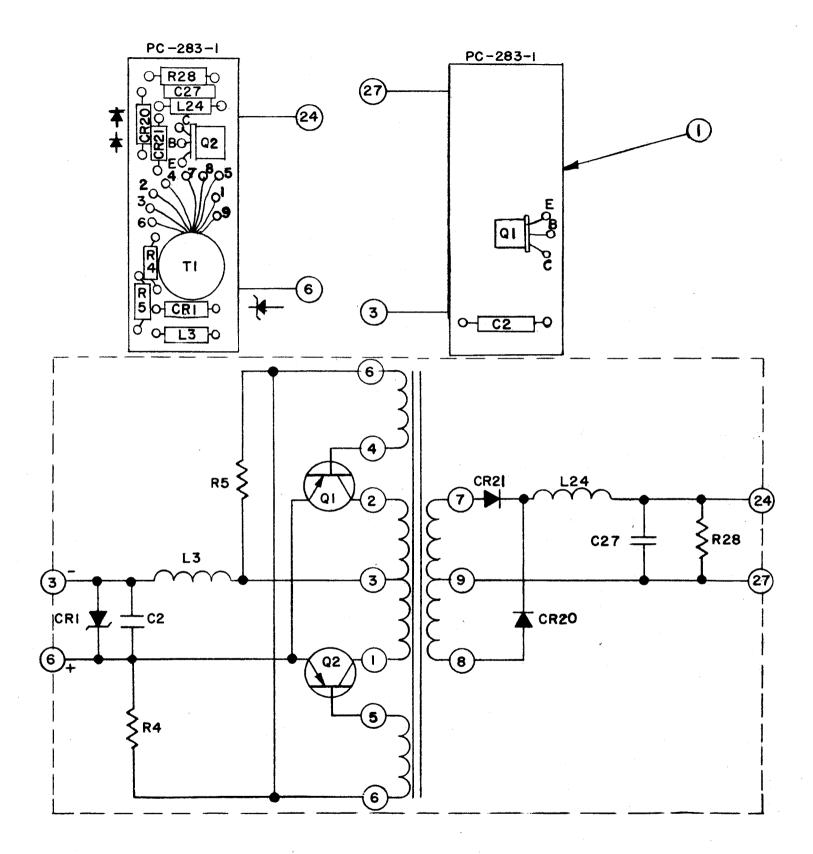

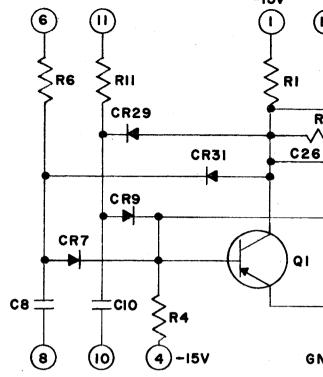

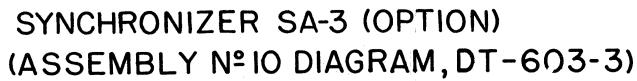

| 20          | Synchronizer SA-3 (OPTION) Assy, No.10      |

|             | Diagram DT-603-3                            |

| 20B         | Assembly No. 10, Waveform Diagram           |

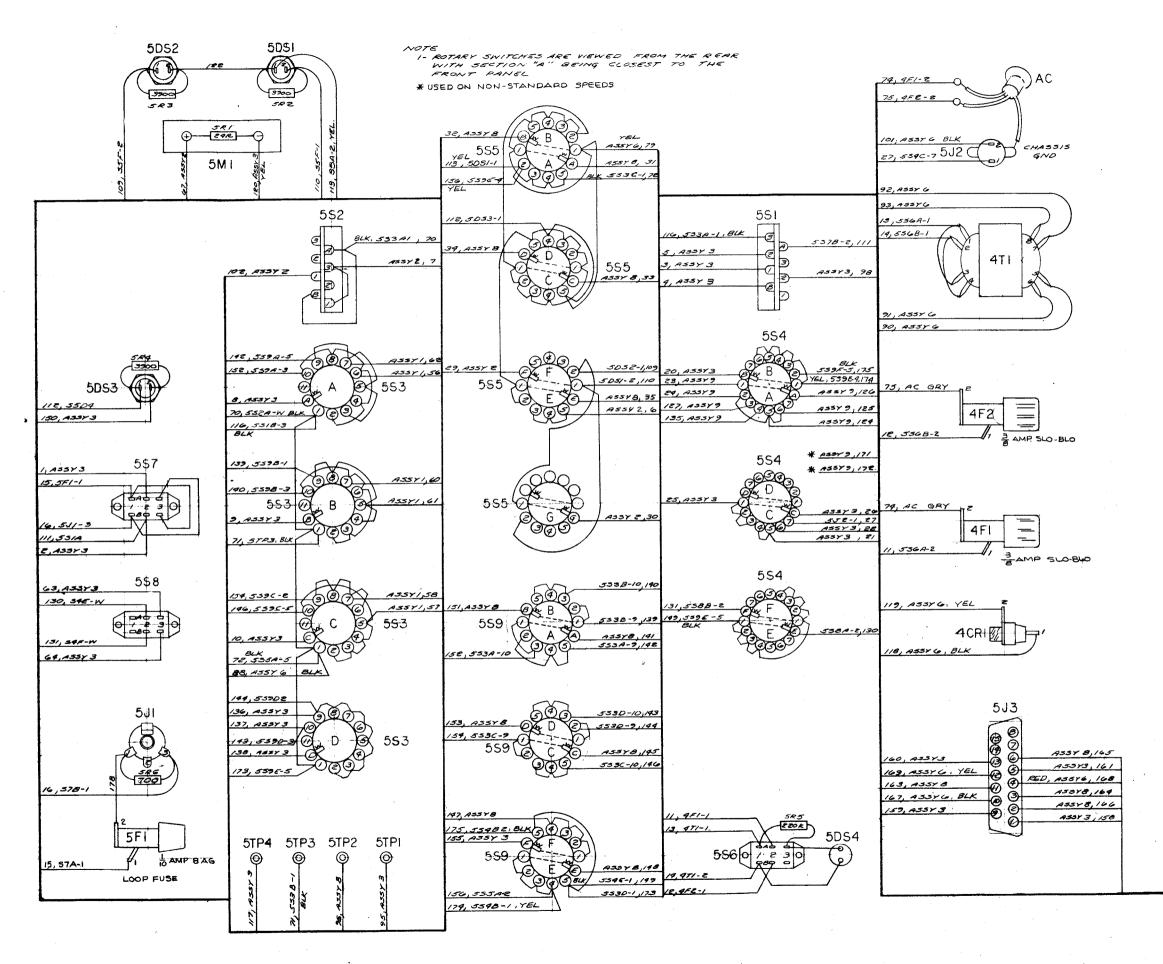

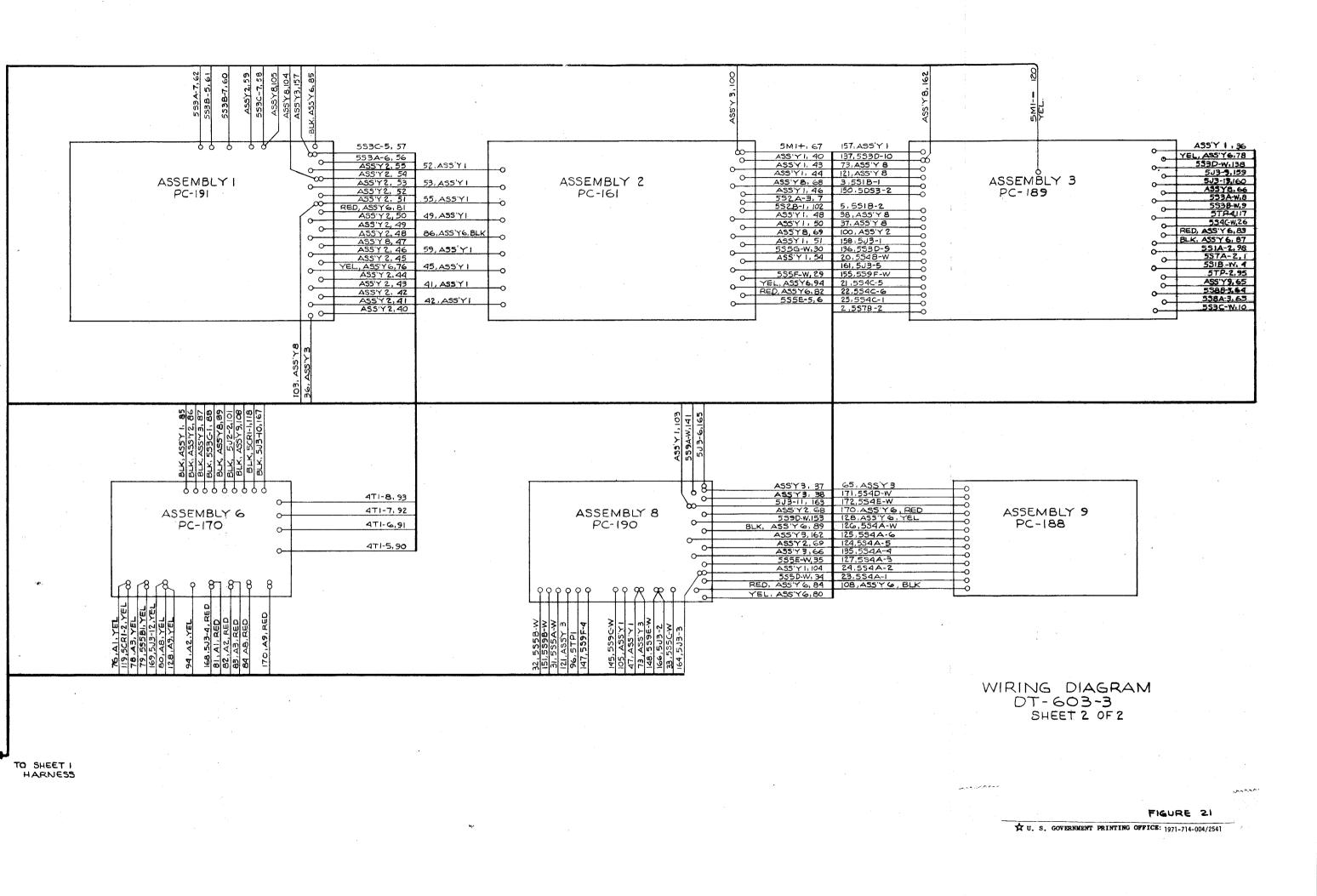

| 21          | Wiring Diagram                              |

|             |                                             |

#### Chapter 1

#### INTRODUCTION

#### 1-1. Scope:

This instruction manual describes the Telegraph Signal Analyzer, Model DT-603-3 and covers its installation, operation, and alignment.

For variations of the DT-603-3 operating on other or additional speeds and inputs, an attachment sheet is provided, noting these changes.

#### 1-2. Purpose and Use:

The DT-603-3 is a high quality, portable, transistorized telegraph signal analyzer operating on the digital principle.

It uses digital techniques to measure all types of telegraph distortion on all or individually selected transitions within a character, and displays the result on an easy to read linear scale meter.

#### 1-3. Description:

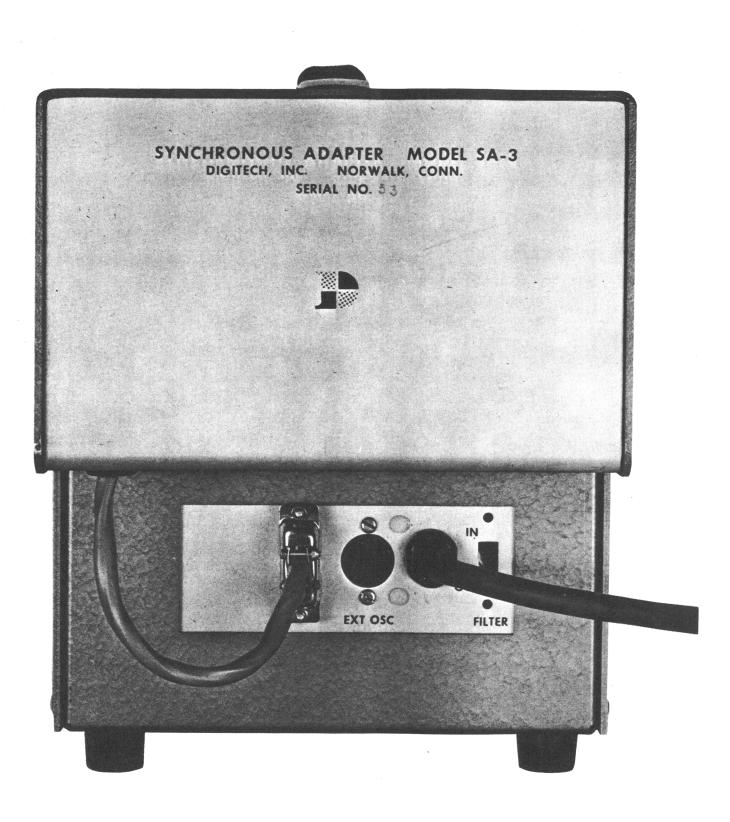

Refer to Figure 1. The DT-603-3 is housed in a portable case measuring approximately 9" high by  $7\frac{1}{4}$ " wide by  $9\frac{1}{4}$ " deep. A carrying handle is pro-vided at the top of the case.

A door is provided on the right side of the unit for access to all non-operating adjustments.

A 3-wire line cord extends from the rear of the unit. The signal input jack is located on the front panel.

#### 1-4. Technical Description:

The DT-603-3 is completely semi-conductor in design, making full use of digital circuitry to create a test instrument for the analysis of telegraph signals.

The DT-603-3 measures all types of distortion on <u>all</u> or <u>individually</u> selected transitions within a character. Bias and End distortion as well as Total Peak, Early Peak, and Late Peak are displayed on an easy to read meter, permitting even an untrained operator to make accurate, unambiguous measurements. Peak readings are displayed with full instrument accuracy and remain displayed until reset manually.

The use of the digital principle makes possible distortion measurements to an accuracy of 2% without any warm-up period or operator adjustments. Long term accuracy is essentially independent of component aging and drift.

A most important feature of the digital principle is that it makes the instrument operation and accuracy independent of speed to an upper limit. Standard operating speeds of 45.5, 50, 61.1, 74.2, 75 and 150 Bauds are supplied internally with provision on the rear panel for using an external oscillator for operating speeds up to 1200 bauds.

The DT-603-3 will measure distortion on start/stop telegraph and data signals of 5,6,7, or 8 level codes, without regard to the length of the stop interval. (With Synchronizer Adapter SA-3 Option it will also phase lock its timing to that of the incoming signal to measure distortion on synchronous signals.)

Measurements may be made on a current basis without interrupting traffic for neutral telegraph signals of 20 or 60 ma and polar signals of 20 or 30 mas. In addition, measurements may be made on a voltage basis using the Hi Z input.

The capabilities of the DT-503-3 described above enable its use in the complete analysis of a telegraph signal to determine the amount and type of bias or end distortion it may contain. The use of EARLY and LATE PEAK distortion measurements enable an operator to determine the amount of fortuitous or cyclic distortion in the signal, while TOTAL PEAK indicates the largest amount of distortion in the signal under test. The instruments ability to measure all transitions or to select each bit individually is an aid in isolating the cause of distortion and can be used to measure speed errors.

1-5. Technical Characteristics:

Types of Distortion Measured:

Display:

Speeds:

Codes:

Marking and Spacing Bias Marking and Spacing End Total Peak Early Peak Late Peak

Meter readout with indicating lights for Marking and Spacing.

Speeds are 45.5, 50, 56.8, 74.2, 75, 150 and EXTERNAL.

An external oscillator may be used to operate the instrument at speeds up to 1200 bauds.

Operates on standard 5, 6, 7, and 8 level start/stop codes with any length stop interval. Operates on Synchronous signals when Synchronizing Adapter SA-3 option is provided. Inputs:

Peak Reset:

Distortion Accuracy:

Bit Transition Selection:

Signal Indicator:

Character Sync:

**Operating Temperature:**

Power:

(

Physical:

- Isolated 20 ma. (200 ohms) and 60 ma. (67 ohms) neutral, and 30 ma.(200 ohms) polar loops.

- 2. Hi Z INPUT (High impedance input) operating on a voltage basis with a signal of -5 volts or more for Mark and Gn. or a positive voltage for Space. This input will operate the DT-603-3 on either a neutral or polar basis, presenting an impedance of approximately 50K ohms for negative signals and a higher impedance when the signal goes positive.

Peal readings are maintained at full level until manually reset.

2%

All or individual selected transitions may be measured.

A light indicates the condition of the loop. (lights on Mark)

A sync pulse occurring once per character is supplied.

$0^{\circ}C$  to  $50^{\circ}C$

The self contained power supply operates from 115 volts a-c 50 to 400 cps, using approximately 15 watts of power.

The unit is portable, fitting in a case 9" high by  $7\frac{1}{4}$ " wide and  $9\frac{1}{4}$ " deep, weighing approximately 8 pounds.

REV 1

#### Chapter 2

#### UNPACKING AND INSTALLATION

#### 2-1. Unpacking and Checking

Remove the DT-603-3 from its shipping container. While doing so check the outside of the case for possible damage incurred during shipment.

#### 2.2. Installation

The DT-603-3 is a self contained portable instrument so no special installation procedures are required.

The line cord should be plugged into a 3 wire receptical of 115v A.C. 60 cycles.

A standard telephone jack is required to patch into the input loop.

When in use, the DT-603-3 should be placed on its rubber feet on a horizontal surface. Operation of the unit on its side or back will result in loss of meter accuracy.

#### EXTERNAL OSCILLATOR

(

If an external oscillator is to be used a Cinch Jones plug CJP302CCT must be obtained and wired to the external timing source. Pin 1 (wide) should contain the 10 volt RMS. signal while Pin 2 (narrow), the groud. )

.

.

## SECTION 3 OPERATION

# 3-1. Chart of Operating Controls, Indicators and Connectors

(

(

(

| Control, Indicator or<br>Connector | Position    | Function                                                                                                       |

|------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------|

| Power (DPDT Slide Sw)              | ON          | Connects both side of line<br>cord to equipment and turns<br>on power.                                         |

| Power (Neon Lamp)                  |             | Lights when ac power is applied.                                                                               |

| Signal Indicator (lamp)            | Flash       | Lights when the input signal is a MARK.                                                                        |

| INPUT (phone jack)                 |             | Provides connection to INPUT circuits.                                                                         |

| Input Polarity<br>(DPDT Slide Sw)  | +<br>-      | Connects tip of jack to<br>positive side of input.<br>Connects tip of jack to<br>negative side of input.       |

| Speed-Bauds                        | Selected    | Sets analyzer operating<br>speed to the indicated rate<br>in bauds or for use with an<br>external oscillator.  |

| Transition Select<br>(Rotary Sw)   | ALL         | For the analysis of all<br>transition positions in a<br>character as determined by<br>the AVERAGE-PEAK switch. |

|                                    | 1 through 9 | For the selection of indivi-<br>dual transition positions<br>in a character.                                   |

| Average-Peak<br>(Rotary Sw)        | Bias        | For the measurement of aver-<br>age distortion on the space<br>to mark (S/M) transitions.                      |

|                                    | End         | For the measurement of aver-<br>age distortion on the mark<br>to space (M/S) transitions.                      |

| CODE-Levels<br>(Rotary Sw)         | 5,6,7,8     | For the selection and measure-<br>ment of 5,6,7, or 8 level<br>Start/Stop signals.                             |

|                                    | Sync.       | For use when the Synchronizing<br>Adapter (option) SA-3 is sup-<br>plied.                                      |

|                                    | 3-1         | p.r.                                                                                                           |

ĺ

| Control, Indicator or<br>Connector | Position     | Function                                                                                                               |

|------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------|

|                                    | Total (Peak) | For the measurement of Dos.<br>distortion on both S/M and<br>M/S transitions occurring<br>both earlier and later than. |

|                                    | Early (Peak) | For the measurement of peak<br>distortion on both S/M and<br>M/S transitions occurring<br>earlier than normal.         |

|                                    | Late (Peak)  | For the measurement of peak<br>distortion on both S/M and<br>M/S transitions occurring<br>later than normal.           |

| INPUT MA<br>(Lever Sw)             | <b>2</b> 0N  | For use with 20 milliamp neutral loops.                                                                                |

|                                    | 60N          | For use with 60 milliamp neutral loops.                                                                                |

|                                    | 30P          | For use with polar loop<br>having from 5 ma. to 30 ma.<br>of current.                                                  |

| Meter Reset<br>(Lever Sw)          | OFF          | No reset is generated in this position.                                                                                |

|                                    | ON           | Resets meter to zero-(must<br>be used when making peak<br>readings.)                                                   |

|                                    | Cal (40)     | Causes meter to read 40<br>percent for meter calibra-<br>tion purposes.                                                |

| Meter                              |              | Indicates the magnitude of<br>distortion on the input sig-<br>nal from 0 to 50 percent.                                |

| Marking (lamp)                     |              | Lights when average distor-<br>tion is of the marking type.                                                            |

| Spacing (lamp)                     |              | Lights when average distor-<br>tion is of the spacing type.                                                            |

|                                    |              | NOTE: Both lights are not<br>when measuring peak distor-<br>tion.                                                      |

| Loop Fuse                          | 1/10 Amp 8AG | Lo impedance input protection.                                                                                         |

| 1                                  | 3-2          |                                                                                                                        |

| Control, Indicator or<br>Connector | Position | Function                                                                                                |

|------------------------------------|----------|---------------------------------------------------------------------------------------------------------|

| Test Points                        | Gnd.     | Connects to circuit ground.                                                                             |

|                                    | SIG.     | Connects to internal circuit<br>side of the input isolator<br>(Positive on mark)                        |

|                                    | SYNC.    | Provides a once per charac-<br>ter synchronizing pulse.                                                 |

| Filter (Side Sw)                   | IN       | Causes removal of small<br>holes in input signal be-<br>fore analysis on Speeds<br>up to 75 Bauds only. |

|                                    | OUT      | Removes filter from the cir-<br>cuit.                                                                   |

Ext. Osc. (2 Pin Socket)

Hi Z INPUT

(

source. Provides connection to high

impedance input circuit.

Provides means for connect-

ing an external Timing

#### 3-2. Operation:

The DT-603-3 may be used by unskilled operators for measuring average and peak distortion on telegraph lines. With a more skilled operator it may be used as a laboratory instrument for the complete analysis of such signals.

a. <u>Initial Steps</u>: Plug the a-c line cord into a source of 115v, 60 cps power and turn the power switch to ON. The power indicator should light.

Set the Speed-Baud switch to the rate of the signal to be measured.

Set the Input MA switch to the current condition of the signal to be measured.

Plug the analyzer in series with the loop. If the SIG IND light does not flash, reverse the INPUT Polarity Switch.

Make sure the TRANSITION SELECT switch is on the ALL position.

NOTE: A check of the meter accuracy can be made by using the METER RESET switch in the CAL (40) position to produce a reading of 40 on the meter. If an adjustment is necessary see Chapter 4. (Such adjustment should not be necessary under normal operating conditions.)

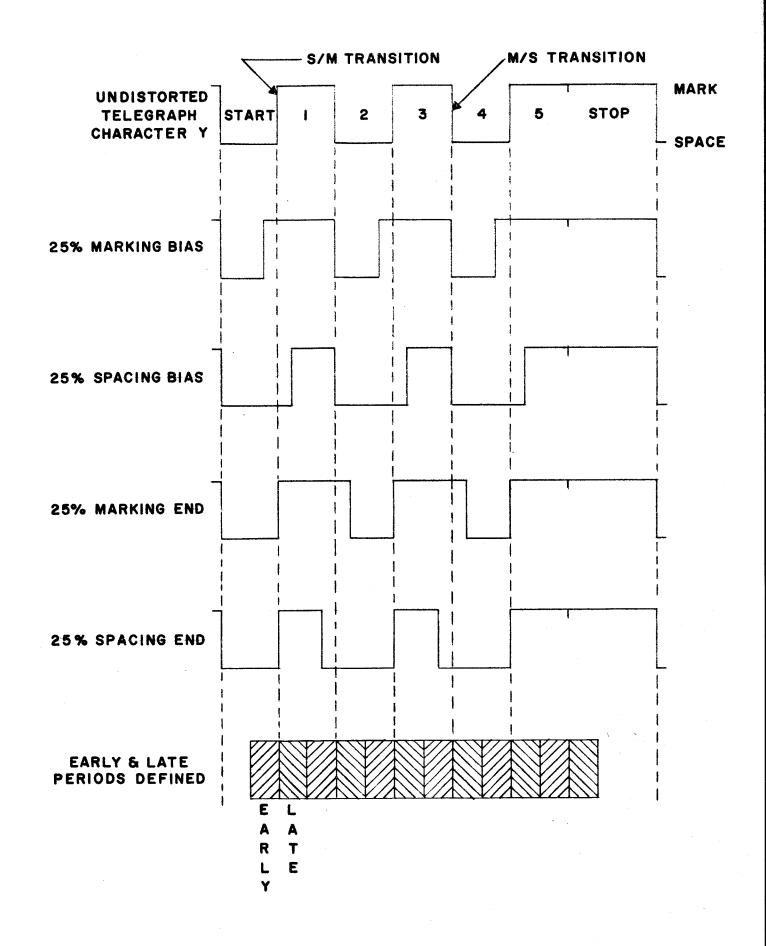

#### b. Bias Distortion (See Figure 4)

Distortion in telegraph is defined as the time displacement of a signal transition from its correct position. On shaped signals, the time of a transition is taken as the half current point for neutral signals and as the zero cross-over point for polar signals.

Bias distortion is defined as an average displacement of the space to mark (S/M) transitions from the correct position. It is marking bias if the resulting mark interval is lengthened (transition occurs early), and it is spacing bias if the preceding space interval is lengthened (transition occurs late).

To measure bias distortion on the DT-603-3 set the center switch to the BIAS position. The amount of bias will register on the meter, with the lights indicating whether it is marking or spacing.

A signal containing zero distortion and operating at the same speed as the analyzer will cause the meter to read zero and the marking and spacing lights to blink alternatively.

#### c. End Distortion (See Figure 4)

End distortion is defined as an average displacement of the mark to space (M/S) transitions relative to the first M/S transition (start pulse). It is called marking end if the preceding mark interval is lengthened (transition occurs late), and it is called spacing end if the resulting space interval is lengthened (transition occurs early).

To measure end distortion on the DT-603-3 set the center switch to the END position. The amount of end distortion will register on the meter, with the lights indicating whether it is marking or spacing.

#### d. Total Peak Distortion

Total Peak distortion on the DT-603-3 is defined as the highest amount of distortion occurring on a signal. It may occur on M/S or S/M transitions, either early or late. A single transition is sufficient to give the peak distortion with full accuracy. The reading will be maintained indefinitely until it is changed by a higher one or reset to zero. In short, a Total Peak measurement, provides a reading of the highest amount of distortion in a signal from any cause.

To make a Total Peak measurement on the DT-603-3 set the center switch to the TOTAL position and reset the meter. The meter reset switch should then be used to destroy the old peak reading before taking new ones. For all PEAK settings of the center switch the Marking and Spacing lights are made inoperative. This is due to the fact that both type of transitions are measured simultaneously and the definition of Marking and Spacing changes with the type of transition.

#### e. Early and Late Peak Distortion

When the center switch is set to Early Peak the DT-603-3 measures the maximum distortion of both M/S and S/M transitions occurring earlier than the correct time.

When the center switch is set to Late Peak the DT-603-3 measures the Maximum distortion of both M/S and S/M transitions occurring later than the correct time.

This ability to display separately peak distortions which occur early and those which occur late, enables the operator to measure the maximum amount of random fortuitous distortion prevalent when transmitting teletype over radio circuits.

#### f. Transition Selection

The DT-603-3 will measure distortion for all transition times in a character restricted only by the center switch (for example on Bias only S/M transitions are measured). In addition, the TRANSITION SELECT switch may be used to restrict the measurement to any one of the intervals one half baud either side of a correct transition location.

This feature is useful in locating defective segments on commutators and locating distortion sources which are evident only in certain bits of a character. It is further useful in detecting distortions due to small speed errors in the signal. <u>NOTE:</u> <u>DO NOT USE FOR SYNCHRONOUS</u> <u>OPERATION</u>.

#### g. Measuring Speed Error

Small differences in speed between the DT-603-3 and the incoming signal can be determined through use of the TRANSITION SELECT. On a random signal pattern the distortion measurement on each successive transition will increase. A faster incoming signal will introduce Marking Bias, shile a slower input signal will introduce Spacing Bias. The amount of speed error in percent is one-fifth (1/5) of the increase in distortion reading from transition 1 to transition 6. For example a 5% increase of Marking Bias from position 1 to position 6 would indicate that the incoming signal speed is 1% fast.

#### h. Front Panel Test Points

There are three test points located to the right of the front panel for use in observing the incoming signal on an oscilloscope.

The GND point provides access to the internal circuit ground.

The Sync point provides a once per character synchronizing signal. It is negative going one-half bit into the STOP interval and positive going at the beginning of a character. It is approximately 13 volts in amplitude. The SIG point provides a reproduction of the input signal at the output of the input loop isolation circuits. This reproduction is a true one with no changes in the shaping on the original signal. The resulting signal measures about 2 volts and is referenced to the internal signal ground. Marks are shown positive and Spaces are negative. No signal is seen at this point when the Hi Z input is used.

#### i. FILTER Switch

On the front panel of the unit is a two position slide switch for the insertion of a filter in the input circuit chain. It will remove from the signal noise due to contact bounce and atmospheric conditions as wide as  $\frac{1}{2}$  milisecond in time duration. For normal use, this filter should be left out of the circuit. It must be left out at operating speeds above 75 Bauds.

#### j. EXTERNAL Oscillator

On the rear panel of the unit is a two pronged jack provided for inserting an external oscillator at 200 times the desired operating speed in bauds, up to a maximum of 1200 bauds. See <u>Chapter 2</u>, Installation for details in connecting this signal.

The signal may be sine or square wave at an amplitude equivalent to 10 volts RMS. The signal may remain connected to the unit while the DT-603-3 is used on its internal speeds and will operate at the external speed only when the SPEED-BAUDS switch is set to the EXT position.

#### k. Input Polarity

The input polarity switch is used to connect the incoming loop signal to the polarity sensitive isolator circuit. When in the + position it connects the Tip of the INPUT jack to the + side of the isolator, when in the - position it connects the tip of the INPUT jack to the - side of the isolator. If the DT-603-3 is plugged into a loop and the SIG IND light does not flash, reverse the POLARITY switch. The polarity switch does not affect the HI Z input.

#### 1. Signal Indicator

The SIG IND light is a long life incandescent lamp introduced into the circuit in such a way as to light when the loop is on Mark.

#### m. Code Levels

The Code Level switch is used to select the proper timing interval within the Analyzer for 5,6,7, or 8 level code signals. A level is defined here as an intelligence bit. For example: Baudot code is 5 level while IBM 10.42 Code is 8 level.

The Sync. position of this switch is used only when the Synchronizing Adapter (option) SA-3 is provided. It then causes the DT-603-3 timing to lock onto that of the incoming sy chronous signal, providing the speeds of the incoming signal and the internal timing are within 0.1% of each other.

#### n. HiZ Input

(

Access to the HI Z (high impedance voltage bridging) input is made by using the orange HI Z pin jack and the black GND pin jack. The incoming signal must be a minimum of 5 volts in amplitude and connected so that the signal to the HI Z pin jack is negative for the Mark condition and ground (or positive) for the Space condition.

#### o. Input (Low Impedance)

The low impedance series input is available through the phone type jack. This input is designed to operate in conjunction with the current levels selected on the INPUT MA switch by inserting the DT-603-3 in series with the incoming loop. Resistance is provided across the jack to prevent an opening of the operating loop while inserting the plug.

#### CHAPTER 4

#### OPERATOR MAINTENANCE AND ALIGNMENT

H-1. Fuse Sizes and Locations:

(

(

For access to the two line fuses, which are 3/8 Amp Slo-Blo the case cover must be removed. This is done by removing the three #6 x 3/8" screws on each side of the cover and lifting it off the base. The fuses are visible on the top of the frame.

A 100 ma. 8AG fuse is provided on the front panel to protect the input isolator from current overloads.

#### 4-2. Crystal Frequencies:

No adjustments are required in the Crystal oscillator of the DT-603-3.

The crystal frequencies and baud speeds relationships are as follows:

| SPEED-BAUD     | FREQUENCY AT<br>3ETP1 (CPS) | CRYSTAL<br>FRECUENCY (Kc) |

|----------------|-----------------------------|---------------------------|

| * 37.5<br>45.5 | 7500 ± 2<br>9100 ± 2        | 120.000<br>145.622        |

| 50.0           | 10000 ± 3                   | 120.000                   |

| * 56.8         | 11378 🛨 3                   | 182.045                   |

| 61.1           | 12224 ± 3                   | 195.652                   |

| 74.2           | 14840 ± 4                   | 118.720                   |

| 75             | 15000 ± 4                   | 120.000                   |

| 150            | 30000 ± 8                   | 120.000                   |

| *1200          | 240,000 ± 30                | 240.000                   |

\*These speeds are not supplied in the standard unit 4-3. Adjusting the Meter:

The meter adjustment for the DT-603-3 is made by setting the METER RESET switch to the CAL position and adjusting the miniature rheostat labeled M until the meter reads 40 as seen from the normal viewing position. This rheostat is the one closest to the front of the unit as viewed through the access door.

This adjustment is made at the factory and should only be made as it becomes necessary.

To mechanically adjust the pointer to zero, remove Assembly 1 at the top of the unit to provide access to the adjustment screw on the meter. Adjust the meter to zero with the power ON and the Meter Reset in the ON position. 4-4. Adjusting the Input Circuits:

The remaining three rheostats are used in adjusting the input circuits. They are adjusted at the factory and need only to be checked on an annual basis.

#### a. 60 MA Threshold Adjust (3ER6)

The rheostat designated 60B is used to adjust the threshold point of the input circuits to operate when the input current of a 60 ma loop exceeds 30 ma.

Set the Input MA switch to 60 MA and adjust the steady mark current in the loop for 30 MA. Key the loop and adjust the 60B rheostat until the SIG IND light on the front panel passes from an off condition to the point where it begins to flash. This sets the input circuits to threshold at 30 MA.

#### b. 20 MA Threshold Adjust (3ER5)

The rheostat designated 20B is used to adjust the threshold point of the input circuits to operate when the input current on a 20ma. loop exceeds 10ma.

Set the INPUT MA switch to 20 MA and adjust the steady mark current in the loop to 10 ma. Key the loop and adjust the 20B theostat until the SIG IND light on the front panel passes from an off condition to the point where it begins to flash.

#### c. Filter Adjust (3ER4)

The rheostat designated FIL is used to adjust the input circuits so that no distortion is introduced by the addition of the internal filter.

A steady source of signal having no variation in distortion (though it may have a fixed amount) must be available for this adjustment.

The technique used for adjusting the Filter circuit is to adjust the FIL rheostat so that the DT-603-3 gives the same readings whether the filter is IN or OUT of the circuit.

This represents all of the adjustments in the DT-603-3.

#### CHAPTER 5

#### THEORY OF OPERATION

#### 5-1. General:

ſ

#### a. Introduction

The DT-603 uses computer logic curcuit techniques to measure time displacements of signal transitions from a reference and to display the result as a percent distortion on a meter.

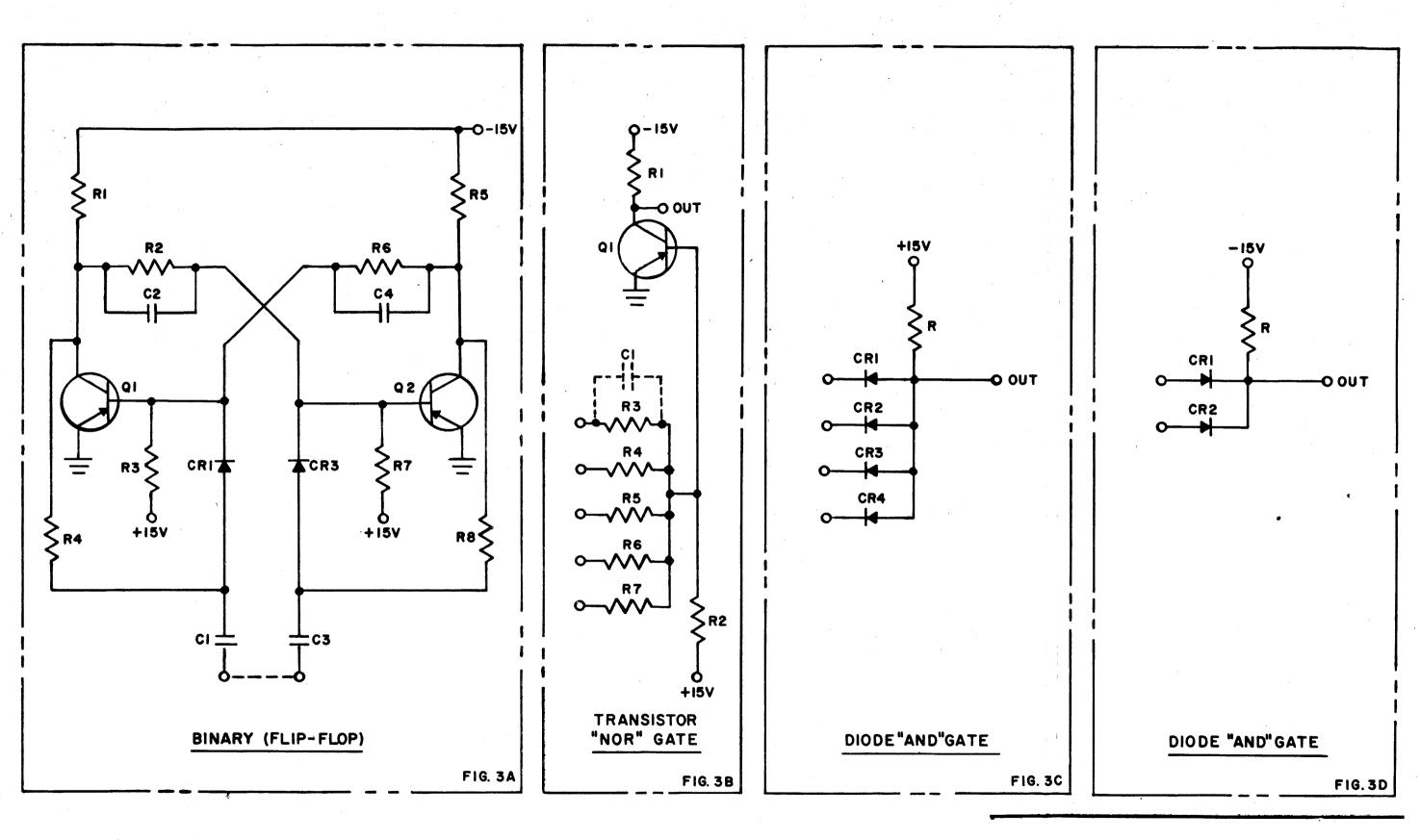

The majority of circuits are repetitive and fall into two main classes, bistables (flip-flops) and gates. A detailed analysis of these circuits is provided here and should be used for reference when consulting the remainder of the theory.

#### b. Bistables (flip-flops)

A typical flip-flop is shown in figure 3. The circuit is called bistable because it has two stable states. The circuit is in a stable state with Ql conducting (on) and Q2 non-conducting (off) or vice-versa. Assume Q1 on and Q2 off. The collector of Q2 will be at a negative potential close to the supply voltage. This negative voltage causes current to flow , through R6 to the base of Q1 to saturate it. Some of the current flows through base resistor R3 to the +15 volts supply, to maintain a negative base to emitter voltage capable of saturating Q1. The saturation current of Q1 causes a voltage drop across R1 which places the collector of Q1 near ground (approx. -.2v). The voltage divider formed by R2 and R7 from ground to positive 15 volts places the base of Q2 positive thereby insuring turnoff. Resistors R3 and R7 absorb collector leakage current Icbo during the off condition to insure that either transistor can be reverse biased up to temperatures of 50° Centigrade. The resulting condition is stable since Q1 - is forced by Q2 - off to remain that way and Q2 - off is forced by Q1 on and the positive bias from R7 to remain that way. The circuit operation is identical with Ql turned off and Q2 turned on.

A change in condition is usually accomplished by triggering the "ON" transistor off. The regenerative action of the circuit then turns the "OFF" transistor on. For example to turn Ql off a positive pulse is applied to Cl where it is differentiated by ClR4. The resulting positive spike passes through CR1 to the base of Ql to turn it off. Capacitors C2 and C4 help to speed up the regenerative action which then tales place while Ql is turning off and Q2 is turning on. When the flip-flop is used in a counting function, input capacitors Cl and C3 are tied together. The input pulse is steered to the off transistor by the differentiating resistors R4 or R8. The collector of the Ql, the "ON" transistor, is at ground thereby allowing the trigger to go positive at the junction of ClR4 while the collector of Q2 is at -9 volts keeping the trigger at C3R8 at a net negative potential. This system is called collector steering. When a flip-flop is not used for counting, but rather as a storage element resistors R4 and R8 may be returned either to the collectors or to external steering signals. Several trigger circuits consisting of a capacitor, resistor, and diode combination may be used for each transistor of the flip-flop.

#### c. Gates

Two types of logical gates are used in this unit, the transistor NOR gate and the diode AND gate. The most frequently used gate is the transistor "NOR" gate shown in figure 3b. It consists of a transistor Ql, its collector resistor Rl, a base biasing resistor R2 (mainly for operating at elevated temperatures) and a number of input resistors which may range from one to six. The gate operates so that a single negative input will cause Ql to saturate and bring its collector to ground. On the other hand all inputs must be positive (ground potential) to cause Ql to turn off and provide a negative output. Thus the gate will go negative when there is positive coincidence on <u>all</u> inputs, a characteristic which makes it an AND gate, or the gate will go positive when any of the inputs goes negative, a characteristic which makes it an OR gate. The circuit then is used to perform both the AND and the OR logical functions by proper choice of input signals.

Capacitor Cl, a small capacitor, is sometimes used to speed up the operation of a gate during the turn-off time.

The diode AND gate shown in figure 3c. is another form of the logical AND gate. Unlike the transistor gate described above it does not invert the signal. Any negative signal on one of the inputs will cause a negative output through a forward biased diode regardless of the signals on the other three. If <u>all</u> the inputs are positive (ground) then the output will go positive.

The diode gate in figure 3d. is also an AND gate but operates in such a way that any positive (gnd) signal on one of the inputs will cause a positive output through a forward biased diode regardless of the signal on the other input. If <u>all</u> inputs are negative, then the output will go negative.

The choice of which type of diode AND gate type is used depends on the polarity of the desired output.

#### 5-2. Block Diagram Theory of Operation:

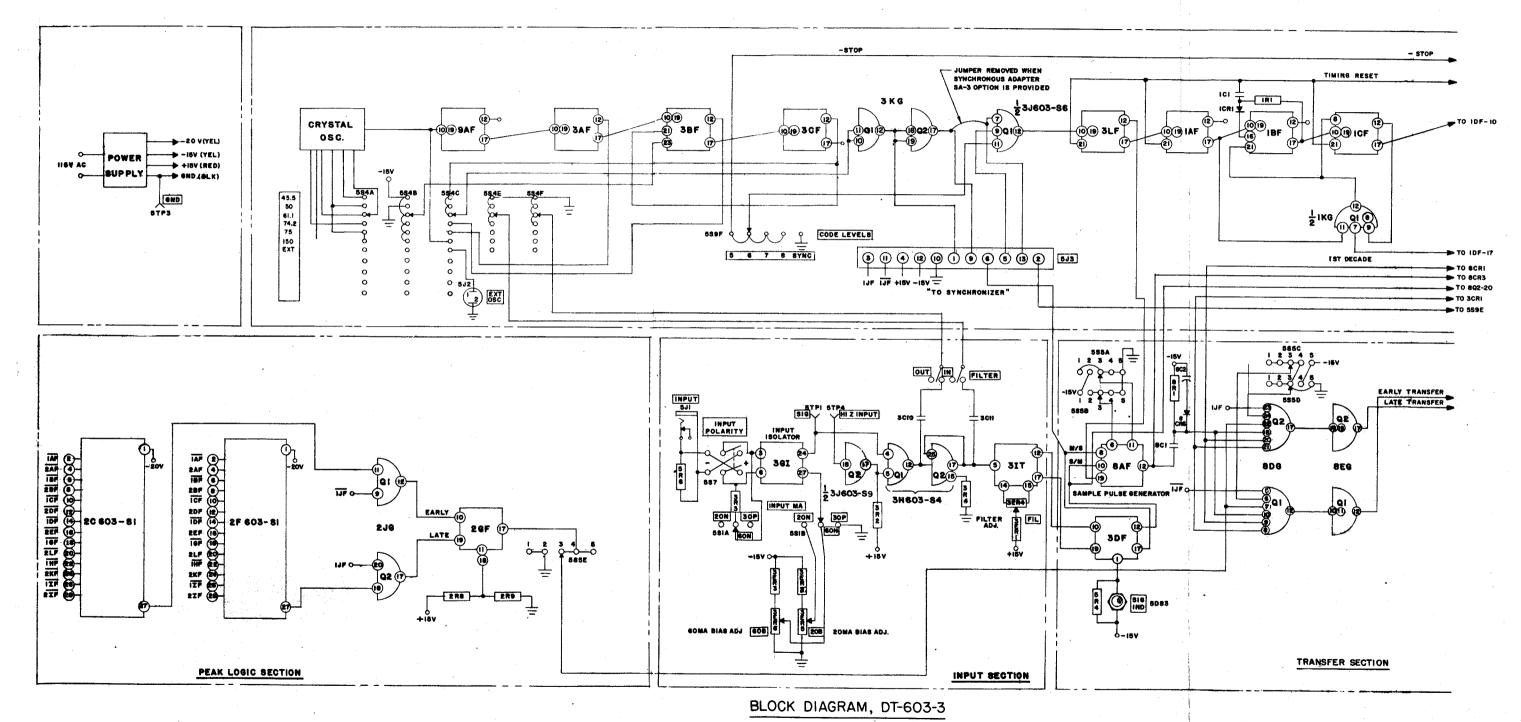

Refer to figure 5, a Block Diagram of the DT-603-3

NOTE: See Chapter 7 PARTS LIST for an explanation of submodule and component reference designations and locations.

The heart of the unit is a crystal controlled Pierce Oscillator operating at several hundred times the desired rate in bauds, operating into a four stage binary divider (9AF, 3AF, 3BF, and 3CF). Switch 5S4 selects the proper crystal for the oscillator and selects an output from the binary divider at 200 times the operating rate in bauds. The selected divider output passes through gates 3KGQl and 3KGQ2.

The squared up timing signal is then applied to 3J603-82 Ql where

its passage through this gate is controlled by a stop pulse generated by the combination of the timing chain and the input signal being measured.

When the timing signal is allowed to pass through 3J603-S9 it is divided in half by 3LF and further divided into one hundred parts by two decades in cascade to produce a timing signal at 1JF which completes one full cycle per bit. The position of the timing chain starting with binary 1AF and ending with binary 1JF has therefore, one hundred states or counts per bit of input signal. It is this count which determines distortion in the input signal. The input signal transition creates a transfer pulse to transfer the count from this timing chain into a Register where it is stored, decoded, and appears as a reading on the meter.

The counter formed by binaries lEF, 1FF, 1LF, and 3FF and gates 3BG 8CG Ql and 8CG Q2 determine character timing. Assume that gate 3J603-S9 Ql is closed and the timing chain is not operating. The next M/S (mark to space) transition of the input signal will cause 8CG Q2 to go positive, thereby resetting binaries 1AF, 1BF, 1CF, 1DF, 1IF 1EF, 1FF, 1LF, and 3FF to a "one" state. The change in 1EF causes 8BG Ql to saturate (gnd.) and thereby open 3J603-S9 Al allowing timing signals to pass through. When six and one-half bits have been counted gate 8BG Ql turns off (negative) stopping the timing cycle. Measurements are possible then during the first  $6\frac{1}{2}$  bits of a telegraph signal on 5 level operation. For 6 level operation the circuit times out  $7\frac{1}{2}$  bits; for 7 level,  $8\frac{1}{2}$  bits; and for 8 level,  $9\frac{1}{2}$  bits.

The outputs of the character timer (lEF, lFF, lLF, and 3FF) are selected through the TRANSITION SELECT switch 5S3 as inputs to a diode AND gate on Assembly 3. Its output is always positive on the ALL position and is positive for one bit only, starting ½ bit before and ending ½ bit after a properly timed selected transition. Its output is used to limit the generation of a transfer pulse to the selected time interval.

(

The input telegraph signal is connected through a polarity reversing switch 5S7 to an Isolator 3GI allowing the DT-603-3 to be inserted anywhere in series with the telegraph loop without concern for grounds. The output of the Isolator is biased for the selected loop current and is connected to a threshold circuit consisting of the amplifiers of 3H603-S4 before being squared up in Schmitt Trigger 3IT. A noise filter may be introduced into the threshold circuit by switch 5S8. Since the threshold circuit is adjusted to provide snap action at the mid-current points of the incoming signal, the output of 3IT provides a squared replica of the incoming signal with the transitions occurring at the mid-current points of the incoming signal. The output from 3IT is further reproduced in binary 3DF, one side of which operates the SIGNAL INDICATOR Lamp 5DS3 when the incoming signal is a Mark.

When the Hi Z voltage input is used the isolator 3GI is completely bypassed and the signal is amplified by gate 3J603-S9 Q2 before entrance to going to the threshold circuit of 3H603-S4.

The transitions from 3DF are used to generate transfer pulses at 8AF as selected by the AVERAGE-PEAK switch, 5S5. When measuring Bias distortion, only the S/M (space to mark) transitions are allowed to generate transfer pulses. When measuring END distortion, only the M/S transitions are allowed to generate transfer pulses. When measuring PEAK distortion both the S/M and M/S transitrons provide outputs at 8AF, where potential transfer pulses begin. The selected input signal transitions are used to set binary 8AF. The binary is then reset within 1/100th of a bit by an output timing signal from binary 3LF so as to insure that a transfer will not occur during the short time interval that the timing chain is in the process of changing.

The transfer pulses generated in binary 8AF are a-c coupled into gates 8DG Ol and 8DG O2 where a number of restrictions are placed on their passing through. The first restriction allows transfers which occur later than the correct time to pass only through 8DG Q2, while those occurring earlier than the correct time are allowed to pass only through 8DG Ql. A second restriction allows no transfer to pass for the Start pulse, since this is the reference for all timing in a Start-Stop telegraph signal and has, by definition, no distortion. A third restriction is from the TRANSITION SELECT which may limit the passage of transfers to a selected time interval during a character. The fourth restriction comes from the EARLY and LATE PEAK positions of 5S5 which allow only the selected type of transition to pass by saturating 8DG Q2 for EARLY PEAK and 8DG Q1 for LATE PEAK. The fifth and final restriction is active when peak measurements are being made. The output of the Peak Logic circuits prevents a transfer from passing unless it represents a higher distortion than that already stored in the Register.

Thus the surviving transfer pulses, representing incoming signal transitions to be measured are generated and passed through inverting driver gates 8EG Ql and 8EG Q2 where they are used to transfer the count in the timing chain for storage in the Register.

The Register is made up of binaries 2AF, 2BF, 2DF, 2EF, 2LF, 2KF, 2IF, and 2HF. The outputs of each binary of the two decades of the timing chain is connected to a corresponding stage in the Register in such a way that either the number in the timing chain or its one's complement can be transfered. The Late transfer signal transfers the number directly while the Early transfer signal transfers the one's complement of the number in the timing chain. This reversal of numbers provides for counts of 0 to 49 during the position of a bit when transitions are Late and from 49 to 0 during the position of a bit when transitions may be Early. The number transfered into the register at the time of a signal transition becomes numerically the percent distortion. The decision as to type is made by the selector switch 5S5 and the MARKING and SPACING lights. These lights operate from the eighth stage of the Register indicating whether the transition occurred earlier or later than normal.

The number stored in the first seven stages of the Register are decoded by a precision resistor network into a heavily damped meter to display the magnitude of distortion in percent.

The peak Logic circuitry made up of sub-modules 2C603-S1, 2F603-S1, 2JG and 2GF compare continuously the number in the Register with that of the timing chain decades. A gating signal is formed in 2GF which is positive only for those numbers where the timing chain count is equal or greater

than the number in the Register. This peak gating signal when selected by 555 becomes one of the restriction of the passing of transfer signals through 8DG Q1 and 8DG Q2.

Meter Reset switch 5S2 is used to manually reset the Register to zero or in the Cal. (40) position to set it to 40. The meter is provided with a variable shunt resistor 3ER7 for adjusting it to read 40 in the CAL position of 5S2.

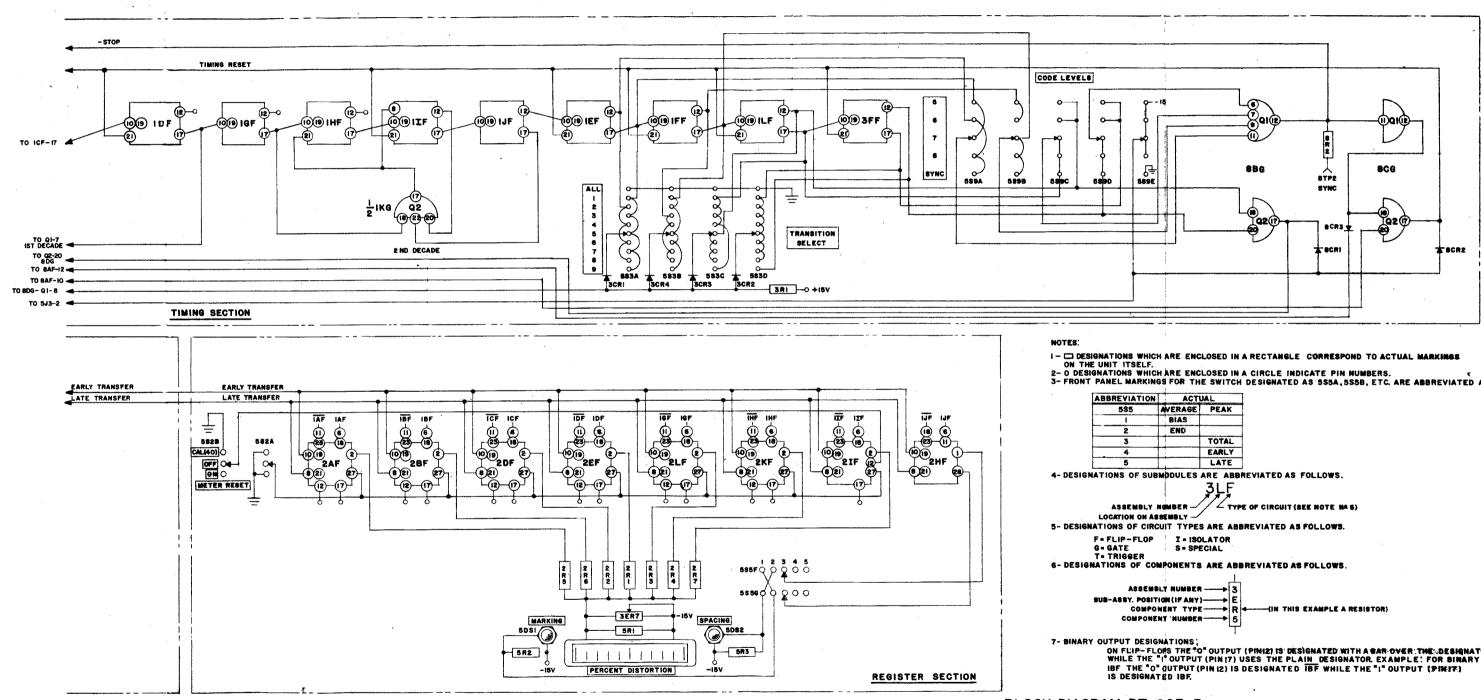

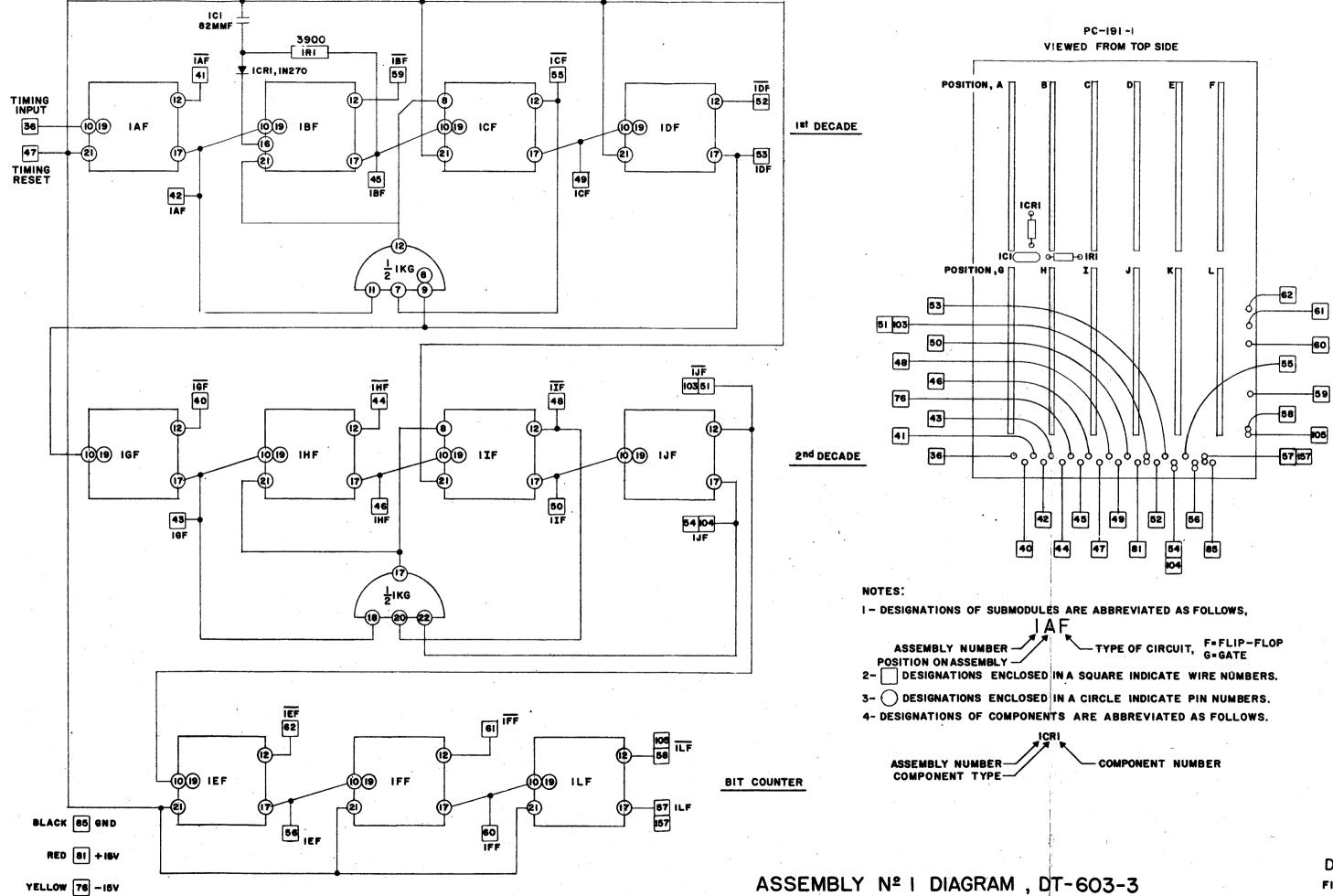

#### 5-3. Assembly 1 - Timing Counters:

Refer to figures 6A, 6B, and 9A

Assembly 1 contains the two Decade Counters of the Timing Countdown and three of the four stages of the Bit Counter.

A timing signal at a frequency of 100 times the rate in bauds coming from Q2 of 3LF (3LF output) is used to trigger the first stage of the first decade counter made up of binaries 1AF, 1BF, 1CF, 1DF and gate 1KG Q1. The decades used in the DT-603-3 use a 1-2-4-2 weighting on the binary stages as shown in the wave forms of figure 6a. When a count of 0010 (4) is reached 1KG Q1 turns off (negative). At the next count its output goes positive changing the count to 1101 (5). Stage 2 (1BF) is reset to a 1 while the last two stages are reversed by triggering 1CF to a zero which in turn triggers 1DF to a 1 state. The output of 1DF has a frequency of 10 times the rate in bauds.

The second decade, made up of binaries 1GF, 1HF, 1JF, 1JF and gate 1KG Q2. Its operation is identical to that of the first decase described above.

The remainder of the assembly is taken up by binaries lEF, lFF, and lLF which together with binary 3FF make up the Bit Counter (Character timer). The "0" output of lJF is used instead of the "1" output to trigger the first stage of the counter, providing a one-half bit offset at the beginning of a character. The outputs of these four binaries are decoded by switch 5S3 TRANSITION SELECT to provie on Assembly 3 a gating output one bit wide beginning one-half bit before and ending one-half bit after a correct input signal transition.

The output of these binaries is also connected to Assembly 8 where a count of  $6\frac{1}{2}$ ,  $7\frac{1}{2}$ ,  $8\frac{1}{2}$ , or  $9\frac{1}{2}$  is detected before a STOP pulse is generated in 8BG Ql to prevent further oscillator signals from entering the counting chain.

The TIMING RESET signal is caused by the telegraph signal Start transition and resets the decades and the Bit Counter stages to all "1" 's. This destroys the coincidence of the stop gate 8BG Ql Assembly 8 allowing the oscillator signals to enter the timing chain for another character interval up to  $\frac{1}{2}$  bit into the stop pulse.

5-4. Assembly 2 - Register and Peak Logic:

Refer to figures 7A and 7B.

Assembly 2 contains two major sections, the Register and the Peak Logic Circuits.

#### a. The Register

The Register is made up of eight binaries corresponding on a stage for stage basis with the eight binaries of the two timing decades of Assembly 1. The trigger .networks of these stages are connected to the decades in the manner shown in Figure 7A so that when a Late transfer command pulse occurs, the binary state of each stage of the decade counter is transferred into the corresponding Register stage. When a Earky Transfer command pulse triggers the Register the inverse of the binary state of each stage in the decade counter (except the Last-lJF) is transferred into it.

The "0" (pin 12) output of each of the first seven Register stages are connected through a silicon diode for isolation between stages to pin 2 then to a precision resistance decoding network. The output of the resistance network provides a current signal proportional to the digits in the Register. The meter is heavily shunted to provide a damping action and is calibrated directly in percent distortion.

The first seven stages provide current in the ratio of 1.2.4.2.10.20.40 to the meter. When the transistor Ql is saturated the precision resistor associated with that stage conducts current through the now forward biased silicon diode into the meter. When the Ql transistor is "OFF", the silicon diode is reverse biased and less than one microampere of current flows through the resistor.

The reverse biasing of the silicon diode is made possible by using the unregulated side of the -15 volt power supply (at a level of about -20 volts) to power all stages on Assembly 2.

The register is reset to zero distortion by clamping each Q2 stage of the Register to ground through a diode (CR27) by means of switch section 5S2A. A calibration signal for the meter at 40% is accomplished by grounding Q1 of the 40% Register stage 2IF in conjunction with the zero reset by means of switch section 5S2B.

The eight the Register stage is used to operate the MARKING and SPACING indicator lights on the front panel for BIAS and END distortion measurements. The state of counter stage lJF in Assembly 1 changes each half bit (Early and Late). It is this information which is transferred to 2HF. When measuring BIAS, transitions occurring EARLY have MARKING bias while those occurring LATE have SPACING bias. The reverse is true for END ditortion. Switch sections 5S5F and 5S5G provide for the reversing of these lights when switching from BIAS to END.

#### b. Peak Logic Circuits

The peak logic circuitry is made up of the diode AND gates on submodules 2C and 2F ( both are special sub-modules type 603-Sl figure 15 gates 2JG Ql and 2JG Q2 and binary 2GF). Sub-module type 603-Sl contains seven dual input diode AND gates, the outputs of which are tied together through seven 16K ohm resistors to provide a single current output. The current output from 2C provides signal to the base of 2JG Ql while that of 2F provides it to the base of 2JG Q2. Gate 2JG Ql is allowed to pass signals only during the period of Early transitions while 2JG Q2 is allowed to pass signals only during the period of Late transitions.

Consider the operation of the seven diode AND gate group. The "O" output of the first seven counter stages are connected to one of the two inputs of the seven AND gates. The second input of these gates is connected to the Register outputs. On sub-module 2C the "O" outputs of the Register stages control the passage of counter stage outputs so that when the number in the counter equals the 1's complement of the number in the Register the collector of 2JG QI goes negative. When it is "less than" 2JG QI stays positive, and when it is "greater than" 2JG QI follows the counter output. For this reason the first negative output of 2JG QI is used to trigger binary 2GF.

On sub-module 2F the "1" outputs of the Register stages control the passage of the counter stage outputs so that when the number in the counter equals the number in the Register the collector of 2JG Q2 goes negative, resetting binary 2GF.

The output of 2GF connects to switch section S5E and provides a gating signal for the transfer pulses on Assembly 8 which on PEAK measurements only allows transfer of a number in the counter to the Register when the telegraph signal transition has a distortion greater than that already stored in the Register.

Note the binary 2GF uses negative triggering and requires a positive voltage for the steering diodes. This voltage is provided by resistors 2R8 and 2R9.

5-5. Assembly 3 - Timing Divider - Input Circuits - Selected Transition:

Refer to figure 8A and 8B.

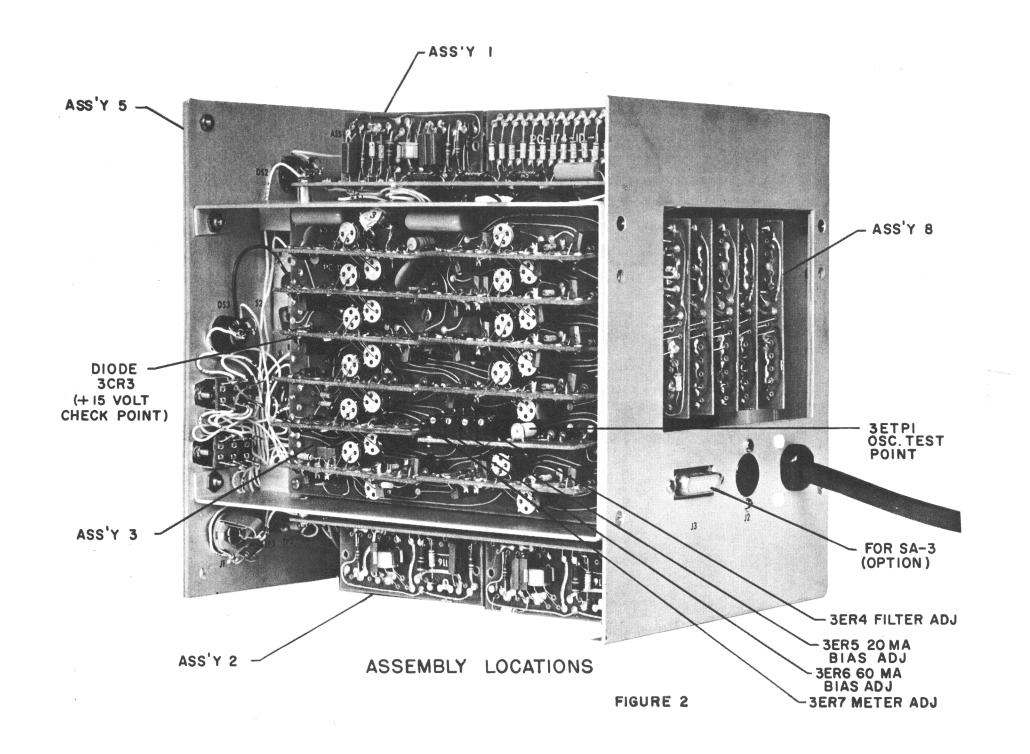

Assembly 3 contains, the Timing Divider, the Input circuitry, the SELECTED TRANSITION gate, and all adjustments for the DT-603-3.

a. Timing Divider

(

The timing divider is made up of binaries 3AF, 3BF, 3CF and 9AF on Assembly 9. The function of the timing divider is to divide down the relatively high frequency signal from the crystal oscillator to a frequency 200 times the desired operating rate in bauds. The four stages operate as a straight binary divider on all speeds except 50 baud. The Ql output

of each binary is selected by switch 5S4C to provide the proper input to timing countdown circuits of the analyzer.

When 50 baud operation is selected switch section 5S4B provides a ground to the reset trigger resistor of binary 3BF to shorten the count from a normal 16 to a count of 12. This allows for the use of a single crystal for operating speeds of 50, 75, 150 etc.

The square wave signal from the squaring gates 3KG is connected to a timing control gate 3J603-S9 Ql where it is allowed to pass through and trigger 3LF, the first stage of the timing countdown. The flow of signal through 3J603-S9 Ql is prevented during the "stop" interval which begins  $6\frac{1}{2}$  bits (5 level) after the Start of a character and lasts until the Start of the next character.

The output (pin 17) of 3LF is used to trigger the decade counters on Assembly 1. The "O" output (3LF) is used to reset binary 8AF on Assembly 8 after it has been set by an incoming telegraph transition.

b. Input Circuits

The input circuitry is made up of an Isolator, Threshold Detector, Filter, and a Schmitt Trigger.

The input telegraph signal is electrically isolated from the DT-603-3 circuitry through the use of a standard Royer type DC to DC converter. The isolator presents a low impedance (67 ohms on 60 ma and 200 ohms on 20 ma, and 30 ma input positions of 5S1) current input which may be inserted anywhere in series with the telegraph loop.

Refer to figure 14, The input isolator 3GI is made up of a push-pull type oscillator operating between one and two megacycles in frequency. On a MARK condition loop current flows between pins 3 and 6 of sub-module 3GI and the resulting voltage causes the oscillator formed by Ql, Q2, R4 R5, and transformer T1 to oscillate. The filter formed by L3 and C2 prevent the oscillations from appearing on the loop. The oscillator output is coupled through a secondary of T1 to a full wave rectifier made up of CR20 and CR22, and a filter made up of L24, C27, and R28. The result is a positive DC voltage across R28 for mark inputs and, since the oscillator does not operate on space inputs, zero voltage across R28 on space. Thus the telegraph signal is reproduced across R28 isolated electrically from the input loop. It is this signal (pin 24) which is brought to the front panel test point 5TPl (SIG) for viewing the input.

The other end of R28 (pin 27) is connected through the INPUT MA switch to appropriate adjustable bias voltages for 60 and 20 ma. neutral operation and ground for 30 ma. polar operation.

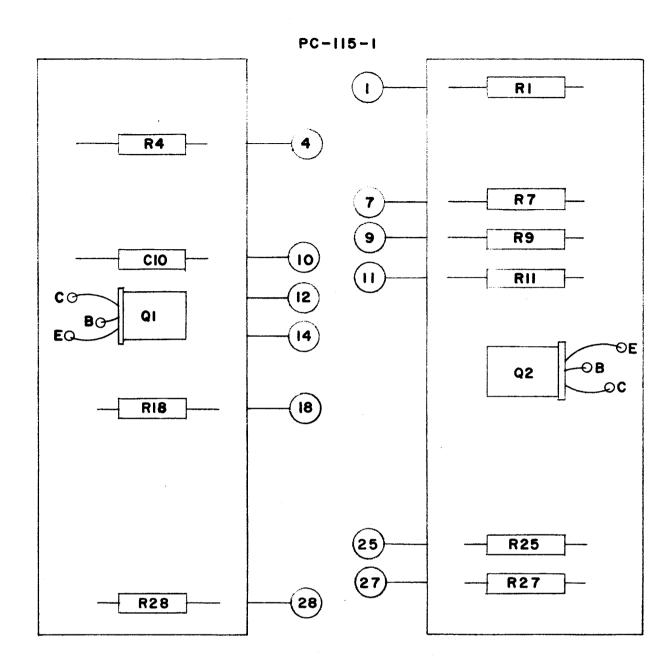

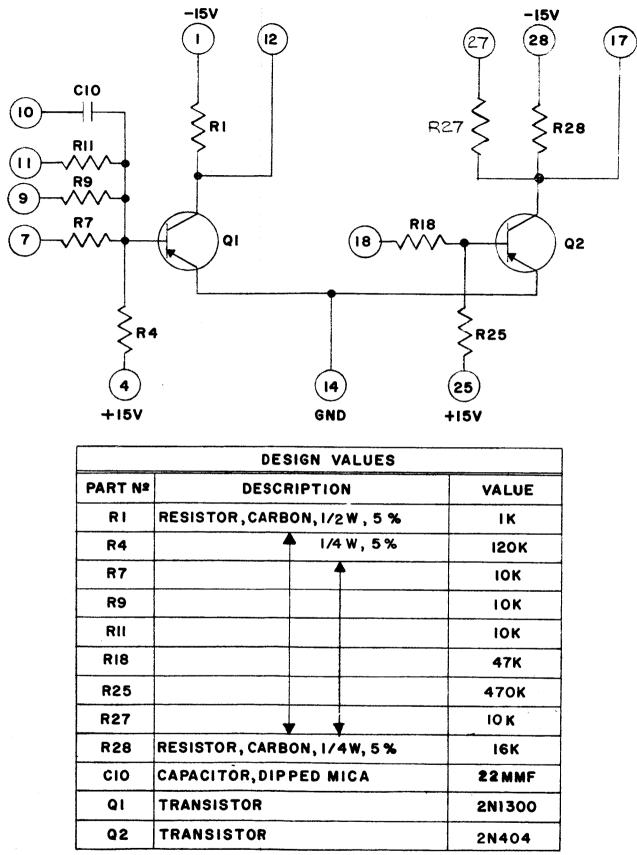

The output of the isolator, properly biased is connected to the threshold detector 3H603-S4 (see figure 17). Ql is biased on through resistor R3 and is turned off when the positive signal of the isolator causes the input diode CR5 to conduct, thereby making the base of Ql positive and turning the transistor off. The bias voltages are adjusted so that this action takes place at the mid-current level of the telegraph signal.

The output of Ql drives the Filter circuit made up of capacitors 3C10, 3C11 and the amplifier made up of R24, R25, Q2, and R28 on 3H603-S4 and 3R5. Two filter capacitors are used because the low output impedance of switching transistors allows shaping only on turn off. Thus capacitor 3C10 shapes the S/M transitions only. In order to retain this shaping it is necessary that Q2 operate as a linear amplifier. Two types of negative feedback are provided to insure this condition: current feedback through emitter resistor 3R5 and voltage feedback through R25. Capacitor 3C11 shapes the M/S transitions.

The ground returns for capacitors 3C10 and 3C11 are provided through switch 5S8 FILTER IN-OUT and interlocked with the Speed switch 5S4 to prevent its use on speeds higher than 75 bauds. When inserted into the circuit the Filter helps reduce false starts and errors due to short duration (about ½ miliseconds or less) noise in the input signal.

When the High impedance Input is used gate 3J603-S9 Q2 becomes the input circuit. It presents an impedance of approximately 50K ohms to the line. A negative 5 volts signal on its input will be interpreted by the DT-603-3 as a Mark and a ground signal will be interpreted as a space. The output of 3J603-S9 Q2 connects to the second diode input of threshold gate 3H603-S4. As long as no signal is being applied to the current input 5J1 the Isolator output will not interfere with the operation of the Hi Z INPUT and as long as no signal is being applied to the Hi Z INPUT gate 3J603-S9 Q2 will not interfere with the Isolator output.

The output of 3H603-S4 Q2, either shaped or square, drives a Schmitt Trigger 3IT to provide a good reshaped replica of the telegraph signal with transitions occurring at the half-current points. FILTER Adj. resistor 3ER4 connected between the emitters of the two stages of the Trigger provides a means of adjusting the level at which 3IT changes state. In this way the output of 3IT can be adjusted to be the same with or without the Filter circuit.

The outputs of 3IT are used to trigger binary 3DF andform aregenerated replica of the input signal. Transistor 3DF Ql drives the SIG IND lamp 5DS3, turning it on when the input signal is in a marking condition.

The outputs of 3DF go to Assembly 8 to form transfer pulses for the Register.

#### C. SELECTED TRANSITIONS:

(

Module 3 also contains the diode gate which detects the count in the Bit Counter to produce the selected one bit timing interval for measuring SELECTED TRANSITIONS. Switch 5S3 connects the outputs of the Bit Counter stage of Assembly 1 and binary 3FF to the input of a diode gate formed by diodes 3CR1 through 3CR4 and resistor 3R1 except in the ALL position when it grounds these inputs. Grounding the inputs of the diode gate provides a positive output thereby neutralizing the effect of this circuit on gate 8DG. When a time interval is selected, however, the diode gate only grounds during the period  $\frac{1}{2}$  bit before and  $\frac{1}{2}$  bit after the proper transition time for the SELECTED TRANSITION, thereby allowing the gates on 8DG to pass a transfer pulse only during this interval.

Sub-module 3E contains the FILTER adjust network 3ER1 and 3ER4, the 20 MA. (20B) bias network 3ER2 and 3ER5, the 60 MA. (60B) bias network 3ER3 and 3ER6, and the Meter (M) shunt adjust 3ER7.

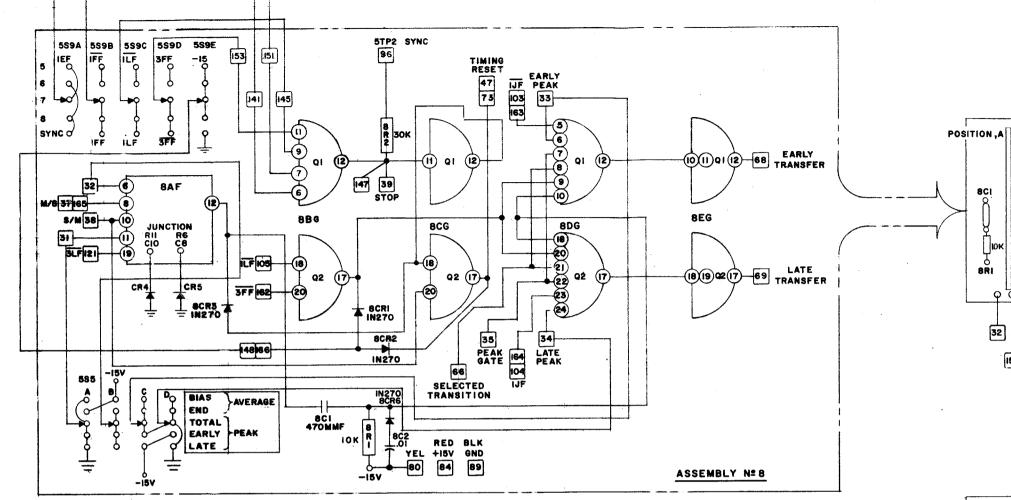

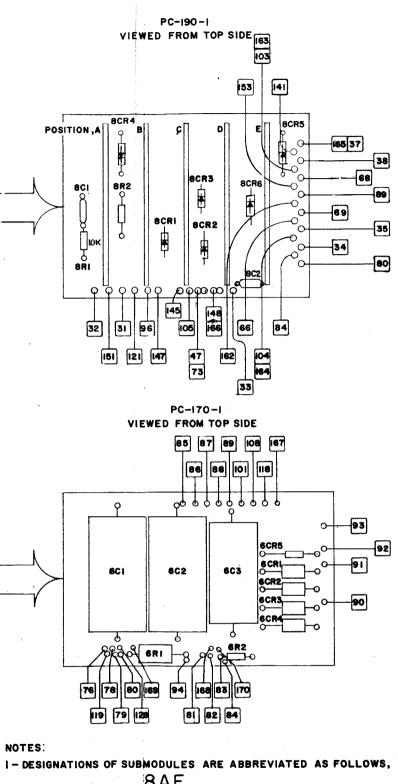

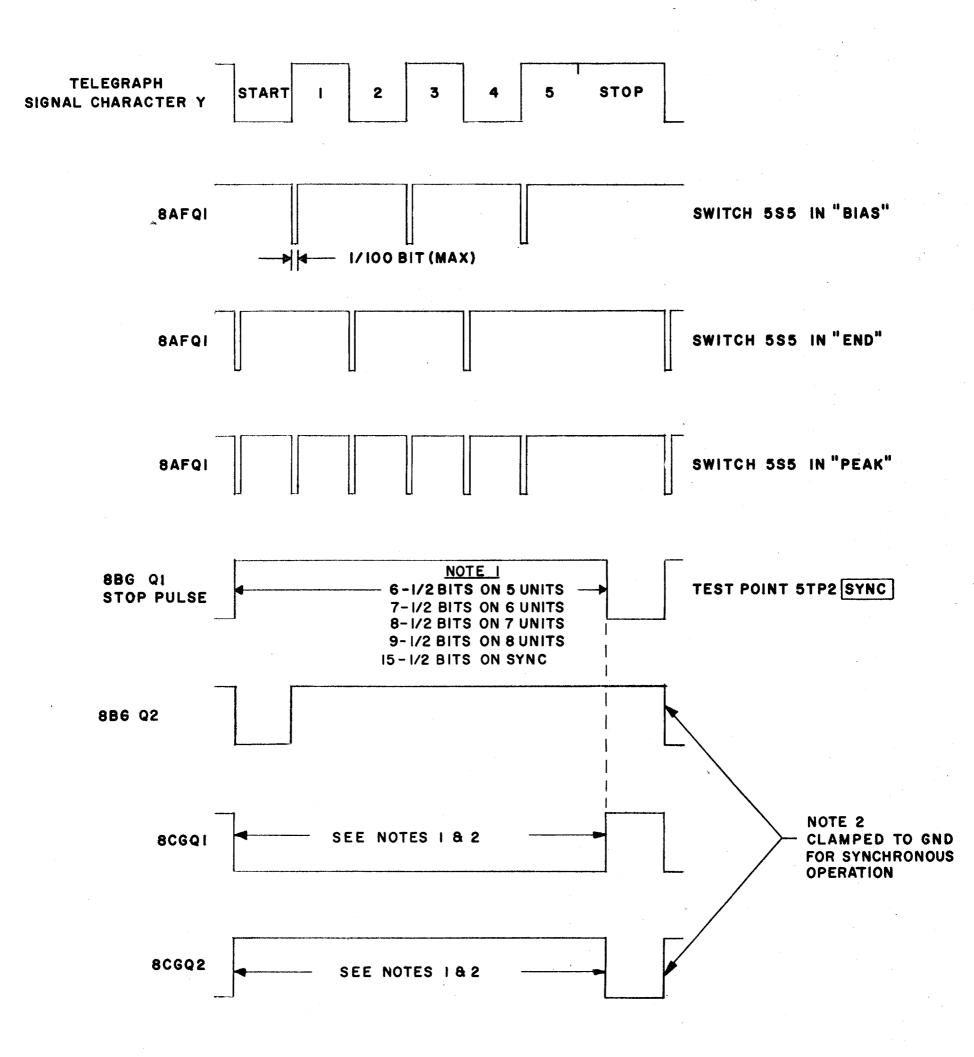

5-6. Assembly 8 - Transfer Pulses - Character Timing:

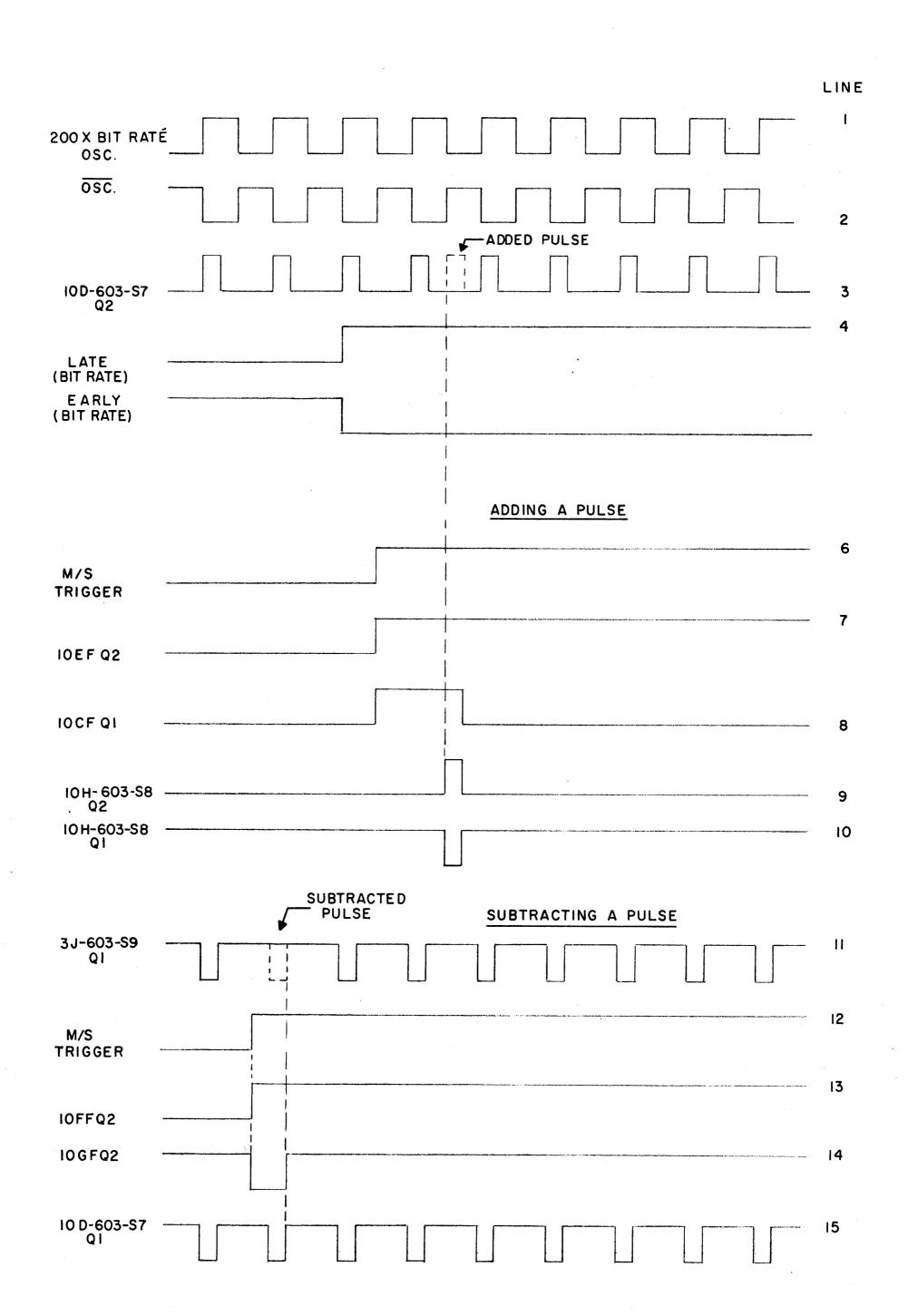

Refer to figure 9A and 9B.

Assembly 8 contains the circuitry for transforming telegraph signal transitions into transfer pulses for the Register (8AF, 8DG, and 8EG) and the circuitry which detects character timing (8BG and 8CG).

All Transfer pulses are formed in binary 8AF. Diodes 8CR4 and 8CR5 are electrically connected across Resistors 8AFR6 and 8AFR11 to permit rapid recovery of the trigger circuits of 8AF at operating speeds of 1200 bauds. Switch 5S5 provides a ground steering voltage for allowing

M/S transitions on BIAS S/M transitions on END Both M/S and S/M transitions on PEAK

to set 8AF to "0". A timing signal, 3LF, resets the binary within a time of 1/100 of a bit or less. The time of reset, which occurs only when the Decade counters are static, becomes the beginning of a transfer pulse. The output of 8AF is AC coupled to gates 8DG Q1 and Q2. The passage of the Transfer through these gates is then controlled by five factors:

- Q1 will pass only Transfers occurring EARLY (input IJF) Q2 will pass only Transfers occurring LATE - (input IJF)

- No transfer will pass for the Start transition (first M/S in a character) - the inhibiting signal comes from 8BG Q2.

- 3. The TRANSITION SELECT may restrict passage of transfers to a selected time interval.

- On EARLY PEAK position of 5S5 no late transfer pulses will pass through Q2.

On LATE PEAK position of 5S5 no early transfer pulses will pass through Q1.

- 5. On all PEAK positions of 5S5 the output of 2GF (PEAK Gate Signal) will prevent transfers from passing through Ql or Q2, unless they represent a distortion higher than that already stored in the Register.

The surviving Transfer pulses represent those transitions selected to be measured. They are passed through the inverter driver gates 8EG Q1 and Q2 before going to Assembly 2 to trigger the Register.

The character timing is detected by gate 8BG-Q1 from the signals connected to it from the Bit Counter through sections A to D of CODE LEVELS switch 5S9. Gate 8BG-Q1 produces a negative Stop pulse  $6\frac{1}{2}$ ,  $7\frac{1}{2}$ ,  $8\frac{1}{2}$  or  $9\frac{1}{2}$ bits from the Start transition for settings of 5,6,7, or 8 level respectively on the CODE LEVELS switch. This negative stop pulse is used to prevent timing signals from reaching binary 3LF of the timing countdown during the Stop interval.

The negative stop signal is inverted in gate 8CG Ql to prime gate 8CG Q2. The S/M signal from binary 3DF,the2nd input to 8CG Q2 is also positive during the Stop period. Gate 8CG is therefore turned off (negative) from the time the stop pulse begins until the S/M signal from 3DF goes negative. This occurs at the beginning of the next character and causes 8CG Q2 to saturate (positive). The output is used to reset the Decade and Bit Counters, removing the negative Stop signal of timing gate 3J603-S9 Ql and allowing another character cycle to take place.

Gate 8BG-Q2 detects the count ll from the last two stages only of the Bit Counter to produce a negative signal beginning at the start of a Character and lasting  $\frac{1}{2}$  bit. Its output is used to prevent the Start transitions from causing an effective Transfer.

Diode 8CR3 uses the positive Stop signal from gate 8CG Ql to reset binary 8AF. This reset is necessary since no timing signals are available from binary 3LF to reset 8AF during the stop interval.

## 5-7. Assembly 6 and 4 Power Supply:

Refer to figure 9A.

(

The DT-603-3 is operated from two zener diode regulated dc voltages and one unregulated voltage. The first secondary voltage of transformer 4Tl (pin 5-6) is rectified by a bridge and filtered by a Pi type RC filter before being connected to a 15 volt, 10 watt zener diode 4CR1. This provides the negative 15 volt dc supply. The unregulated voltage at junction of 6R1 and 6C2 (approx. 20 volts) is used to power Assembly 2 (Register and Peak Logic).

The second secondary voltage of 4Tl (7-8) is half wave rectified and filtered by capacitor 6C3 before being dropped in resistor 6R2. The zener regulator for the resulting +15 volts dc supply 3CR3 is located on Assembly 3 and provides a regulated +15 volts. The need for regulation on the +15 volts is occasioned only by the Filter Adjust of Trigger 3IT which is sensitive to significant voltage changes between the -15 volts and the +15 volts levels.

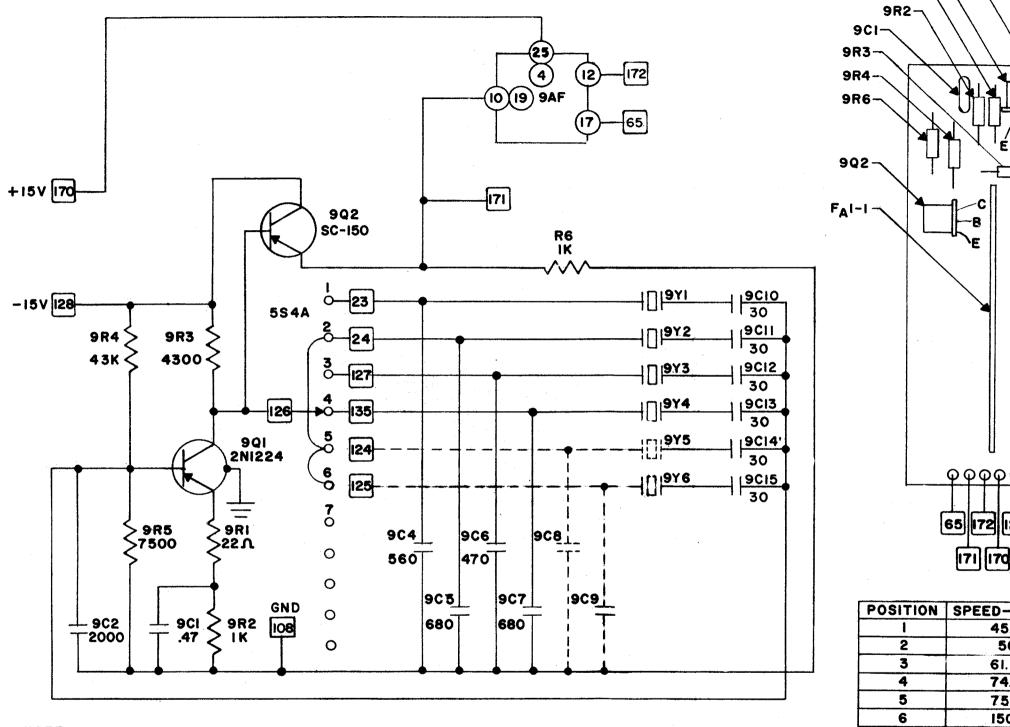

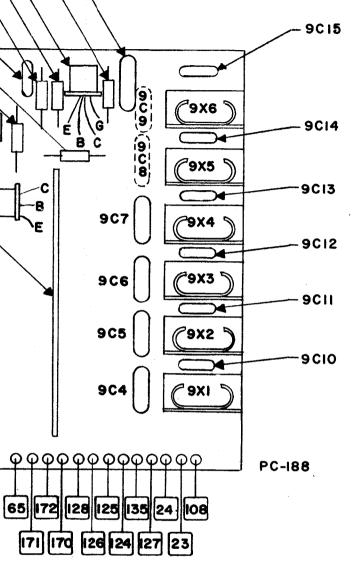

# 5-8. Assembly 9 - Crystal Oscillator:

The basic timing is produced by **a** transistor Pierce Oscillator consisting of transistor 9Ql and its associated biasing networks. Any one of four crystals are switched into the circuit by switch section 5S4A. (Space is provided for 2 additional crystals and load capacitors for special speeds).

Transistor 9Q2 acts as an emitter follower to provide load isolation for the oscillator. Binary 9AF is used as the first stage of the timing divider used to divide the oscillator frequency to 200 times the desired operating rate in bauds.

# Chapter 6

# CORRECTIVE MAINTENANCE

# 6-1. General:

#### a. Component Replacement

The use of printed circuit boards in this unit requires caution in the replacement of defective components. Printed circuit boards are easily damaged by excessive heat during soldering. Use a small iron (25 watts to 35 watts) and apply the hot iron tip to the lead of the component to be removed. DO NOT APPLY IRON TO FOIL. As soon as the solder melts remove the iron and brush excessive solder away. Straighten leads and, if necessary, reheat and pull the lead out. Do not force or twist the leads to remove them as this may result in damage to the foil.

Never attempt to save the component at the expense of damaging the printed circuit board. Cutting out of the component and subsequent removal of the remaining portion of the leads is the preferred method of component removal.

Before inserting the new component, clear all holes of solder. This may be accomplished by briefly heating the area of the hole and, when the solder is soft, tap the board. Mount the component on the p - c board, gently pushing the leads through the holes. Bend the leads close to the foil and clip them to about 1/8" in length. Apply flux to the joints and solder. Remove the iron as soon as the solder flows into the joint. Clean the joint of excess flux with alcohol and the repair is complete.

b. Repair of Printed Circuit Conductor

If the foil conductor is damaged it must be replaced with a physical wire conductor. Remove the defective portion of the conductor. Drill two holes one at each end of the break alongside the foil. Insert either buss wire or insulated wire from the side of the board opposite that of the broken conductor, and bend the ends of the wire across the foil. Apply flux and solder. Check with an ohmmeter for continuity.

## 6-2. Test Equipment Required:

The following test equipment is required for maintenance, and trouble shooting of the DT-603:

Oscilloscope - Tektronix Model 535A or equivalent. Frequency Counter - Hewlett-Packard Model 523B or equivalent. Multimeter - Simpson Model 260 or equivalent. Telegraph Signal Generator - Digitech Model DT-101B, Model DT-103 or equivalent unit capable of generating a telegraph signal with controlled amounts of distortion.

# 6-3. Assected v 10.00 clons:

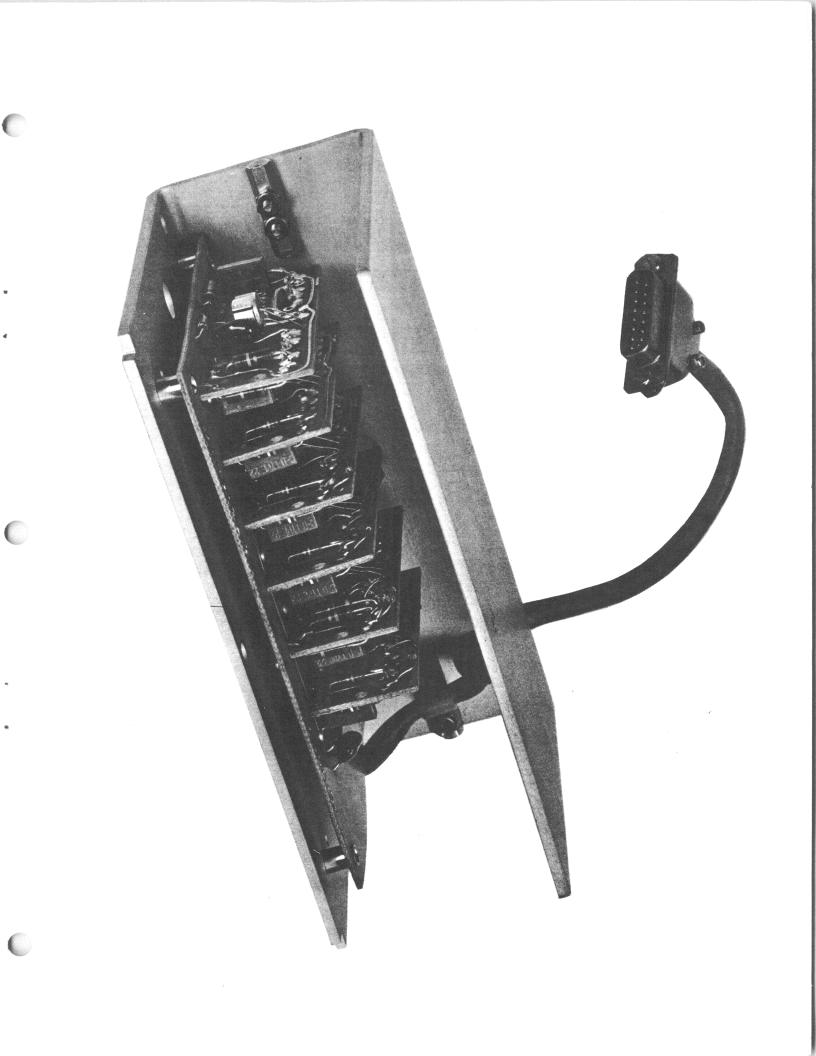

The DT-603-3 is made up of nine assemblies. See figure 2 for a view showing their location within the unit.

| ASSEMBLY<br>NUMBER | LOCATION     | DESCRIPTION                          |

|--------------------|--------------|--------------------------------------|

| 1                  | Тор          | PC-191 Timing                        |

| 2                  | Bottom       | PC-161 Register & Peak Logic         |

| 3                  | Right Side   | PC-189 Timing Divider Input Circuits |

| 4                  | Left Side    | Power Fuses and Transformer          |

| 5                  | Front & Rear | Front Panel & Chassis Components     |

| 6                  | Inside       | PC-170 Power Supply                  |

| 7                  |              | Case and Cover                       |

| 8                  | Rear         | PC-190 Transfer Circuits & Character |

|                    |              | Timing                               |

| 9                  | Inside       | PC-188 Crystal Oscillator            |

|                    |              |                                      |

# 6-4. Trouble Shooting Procedures:

a. General

The DT-603-3 is made up of six functional logic sections as outlined in figure 5, Block Diagram. In this diagram the reference designation for the logic blocks supplies locating information. For example lAF refers to Assembly 1 location A and designates a flip-flop type of circuit.

The first step in servicing a defective unit is to localize the fault to a particular section of the unit, then to a particular sub-module before locating the defective component. In most cases it will not be necessary to remove any of the module assemblies to replace a component. If it should become necessary, however, always turn the ac power off while doing so. Since the circuits other than the oscillator are constructed in the form of sub-modules containing, with few exceptions, either a complet binary or two (2) gates, a trouble shooting procedure for these logic elements will be discussed here.

b. Trouble Shooting a Binary (flip-flop) Figure 10:

There are two types of check which can be made to isolate a defective component in the flip-flop circuit. The first type of check is to determine whether the circuit is dc stable. Ground the base lead of Ql to turn it off. The collector of Ql should go negative and the collector of Q2 should go to ground. If Ql does not turn off, (1) it may have an internal collector to emitter short, or (2) the collector is grounded somewhere in the external circuit. If Q2 does not turn on, going to ground, it may have a base to emitter open or a base to collector open in the transistor. Open circuits between collector of Ql to base of Q2 are another possible cause. Next, reverse this procedure grounding the base of Q2. The dc check, therefore, will locate faulty transistors, resistors or connections within the flip-flop circuit.

If the flip-flop circuit is dc stable, grounding the bases of Ql and Q2 alternately will cause the circuit to flip back and forth between its two stable states. The second type of check involves the ac trigger circuits each consisting of a capacitor, resistor, diode combination. There is at least one trigger circuit connected to each transistor base in a flip-flop. With a signal on each input, check the collectors of Q1 and Q2 to determine which one is at ground and doesn't turn off. The trigger circuit associated with that transistor is suspect. The most probable cause of trouble is a defective diode. This may be checked with the Volt-Ohm-meter in the circuit. Forward resistance of a good diode will be under 20 ohms on the RX1 scale, while the reverse resistance will normally be in the range 200 K to 400K on the RX 10,000 scale. Input trigger diodes are located on sub-modules in position 7, 9, 20, and 22.

c. Trouble Shooting Gates - PNP (Figure 11).

Transistor gates are rather simple to trouble shoot in that they contain only two component types, transistors and resistors. If a gate is found to be not operating check the base wave form on the Oscilloscope. For the transistor to saturate the base must be negative about -0.2 volts with respect to the emitter and to be cut-off the gate must be positive ( and to about 3 volts ). If either one of these conditions exits steadily then the gate collector will stay at the appropriate voltage (gnd. or negative) without changing and the inputs to the gate should be checked. A base voltage significantly more negative than -0.2 volts with respect to its emitter indicates an open circuit.

To determine whether a transistor which is saturated is defective, short the base to the emitter; this should cut the transistor off, producing a negative voltage at the collector.

If the defect keeps the gate always cut-off, check the <u>forward</u> resistance on the transistor base to emitter and base to collector junctions for an open circuit condition.

d. Trouble Shooting a Schmitt Trigger - (Figure 12)

Since a trigger has two stable states controlled by the input signal level, the first check outlined for the binary (Para. 6-4b) is also applicable.

6-5. Trouble Shooting:

(

a. General

Trouble shooting the DT-603 requires the use of the test equipment listed in paragraph 6-2.

The Telegraph Signal Generator is necessary to key the Input circuits of the DT-603-3 and thereby provide Transfer pulses for known amounts and types of distortion.

The Oscilloscope is necessary for viewing waveforms to determine the faulty circuit. Once the trouble has been isolated to a faulty circuit, use of the ohmmeter portion of a Multimeter for checking diode and transistor forward and back resistances will locate the defective component.

The Frequency Counter is necessary only for checking the oscillator speeds. There are no adjustments for the crystal oscillator.

The trouble shooting procedure is given in the form of a discussion aided by a trouble chart where it seemed useful for each major circuitry section in the unit. A single General Chart is provided to make use of the various visual indicators in directing the maintenance personnel to the proper sections of the unit.

Refer to paragraphs 6-1, and 6-3 for specific information on component replacement, and how to trouble shoot the logical circuits found on individual sub-modules. Sub-module identification and location of components may be found in the Parts List, Chapter 7 and the figures associated with each Assembly or Module.

a. To service the DT-603-3 it must first be removed from its protable case. The case is made in two parts, a base and a cover. The cover is removed by removing three screws on each side of the unit and lifting. In this condition, however, access to Assemblies 2.0 and9are not possible. Removal of the two bottom screws on the front panel and two screws in the rear of the L-shaped base will allow the main unit to be removed from the base. Assemblies 1,2,3,8, and 9 containing all of the "active" circuitry are now accessible from the outside of the unit. To gain access to assemblies 4,5, 7 and 9 removal of one or all of the outside assemblies is necessary.

Before starting to trouble shoot make sure ac power of 115 volts 60 cps is applied to the unit, that the power switch is ON, and the neon indicator glows. Failure of the neon to light warrants a check of the  $\frac{1}{4}$ A. Slo Blo fuses located on Assembly 4. They are accessible from the top of the unit.

b. Finding the Faulty Section

For purposes of trouble shooting, the DT-603-3 is made up of 6 major circuitry sections. These are:

| PARAGRAPH     | SECTION      | LOCATION              |

|---------------|--------------|-----------------------|

| 6-5C          | Power Supply | Assembly 6 and 4      |

| 6-5d          | Timing       | Assembly 3,1,8, and 9 |

| 6 <b>-</b> 5e | Input        | Assembly 3            |

| 6 <b>-</b> 5f | Transfer     | Assembly 8            |

| 6-5g          | Register     | Assembly 2            |

| 6 <b>-</b> 5h | Peak Logic   | Assembly 2            |

Use the following chart of visual symptoms to isolate the source of trouble to one of the major sections. When more than one section is listed, they should be checked in the order in which they are listed.

In some cases the chart will list directly a sub-section, submodule, or switches to be checked.

SYMPTOM

(

(

(

- 1. Power Indicator doesn't light

- 2. Mark and Space Lights are both out when S5 is on BIAS or END

- 3. Meter doesn't give any indication on CAL (40)

- 4. Sig Ind doesn't flash

FAULT SECTION Power Supply

a. Power Supplyb. Register

Power Supply

- a. Polarity Switch in wrong position.

- b. Input MA Switch in wrong position.

- c. Input

a. Small Speed Difference between telegraph signal and DT-603-3 timing.

b. Timing (Decades)

c. Register

- a. Transfer

- b. Register

- a. Peak Logic

- b. Transfer (8DG)

- a. Timing

a. Check Gare 3FG Q1 & Q2 on Assembly 3.b. Switch 5S3

- 5. Constant error in Meter reading

- SiG Ind flashes but Meter doesn't read

- 7. Unit operates normally on Average, but will not hold Peak reading.

- 8. Operates on one or more speeds but not on others

- 9. Operates on ALL Transistions but not a. on a SELECTED TRANSITION.

The following reminders may be helpful in trouble shooting a unit.

- 1. To make measurements with the DT-603-3 the METER RESET switch 5S2 must be in the OFF position.

- 2. When, after inserting an input signal, the SIG IND doesn't flash, always check the position of the INPUT POLARITY and the INPUT MA switches.

- 3. When making PEAK measurements or when using the TRANSITION SELECT the METER RESET should be used to verify the readings.

- 4. When checking signals for END distortion, and use is made of the TRANSITION SELECT there can be no measurement for the 1st and last transistion of a character. This is due to the fact that these two can only be S/M (space to mark) transitions, while END distortion is a displacement of M/S transitions.

# c. Power Supply

Check dc supply voltages with a 20K ohm/volt meter. The voltage wires are color coded: Black for ground, Yellow for -15 volts (and -20 volts on Assembly 2), and Red for +15 volts.