|             | SHEET   |                                |   |          |          |          |   |          |   |           |   |    |             |    | IS | SUE | <u> </u> | NUN | 1BE      | R |    |    |      |    |      |           |         |        |         |                    |        |

|-------------|---------|--------------------------------|---|----------|----------|----------|---|----------|---|-----------|---|----|-------------|----|----|-----|----------|-----|----------|---|----|----|------|----|------|-----------|---------|--------|---------|--------------------|--------|

| DRAWING NO. | NO.     | DESCRIPTION                    | 1 | 2        | 3        | 4        | 5 | 6        | 7 | 8         | 9 | 10 | 11          | 12 |    |     |          |     |          |   | 19 | 20 | 21   | 22 | 23   | 24        | 25 2    | 262    | 7 2     | 32                 | _<br>2 |

|             |         | SCHEMATIC DIAGRAMS             |   |          |          |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

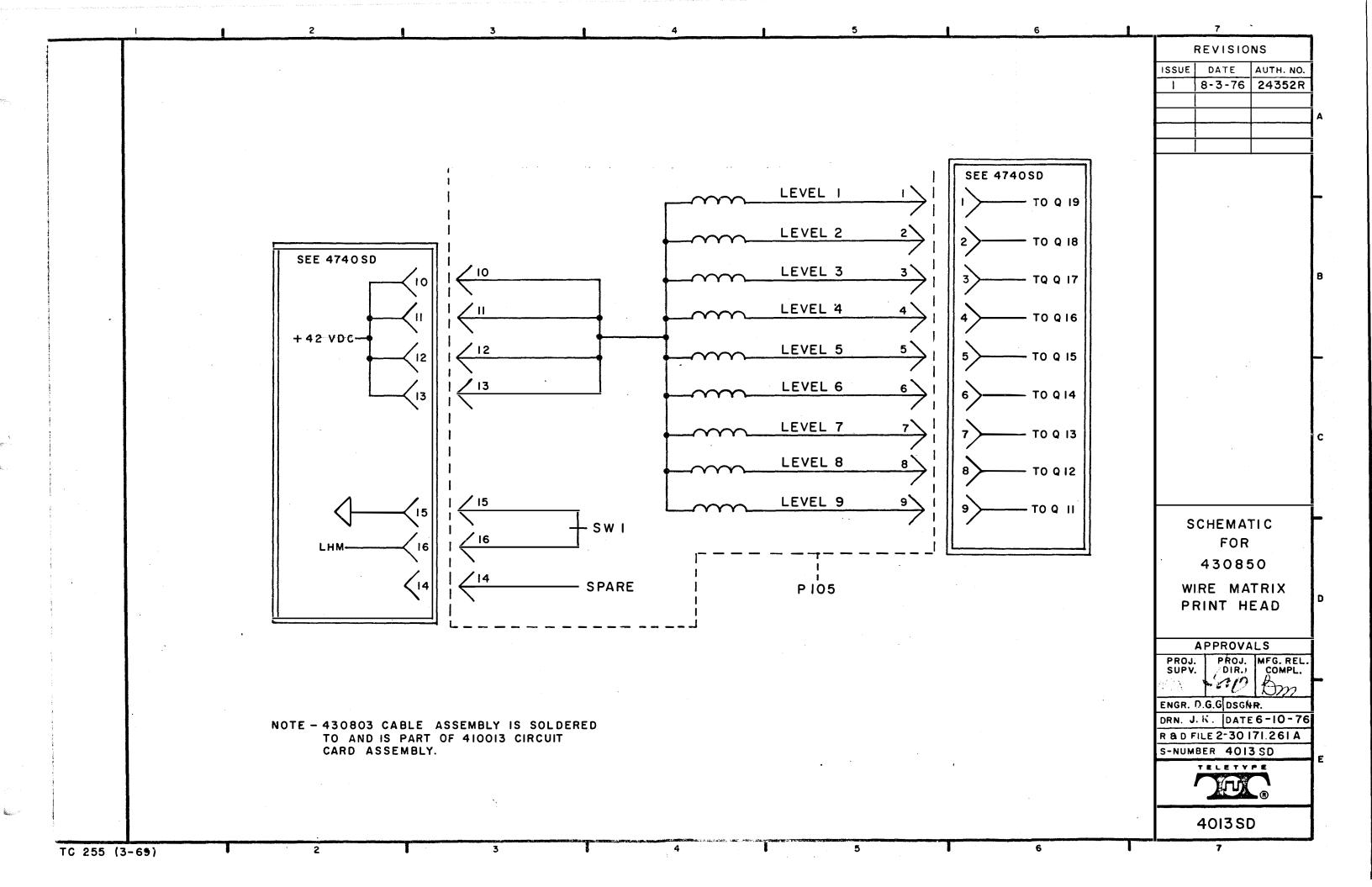

| 4013 SD     | 1       | 430850 WIRE MATRIX PRINT HEAD  | 1 | 1        | 1        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         | T                  |        |

| 4080 SD     | ALL     | OPCON (43K 101 CAA)            | 2 | 2        | 2        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

| 4700 SD     | ALL     | POWER SUPPLY                   | 6 | 6        | 6        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

| 4740 SD     | ALL     | 410740 LOGIC CARD              | 4 | 5        | 6        | _        |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    | <br> | -         |         |        | $\perp$ | -                  |        |

|             |         | ACTUAL DIAGRAMS                |   |          |          |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        | $\pm$   | -                  | _      |

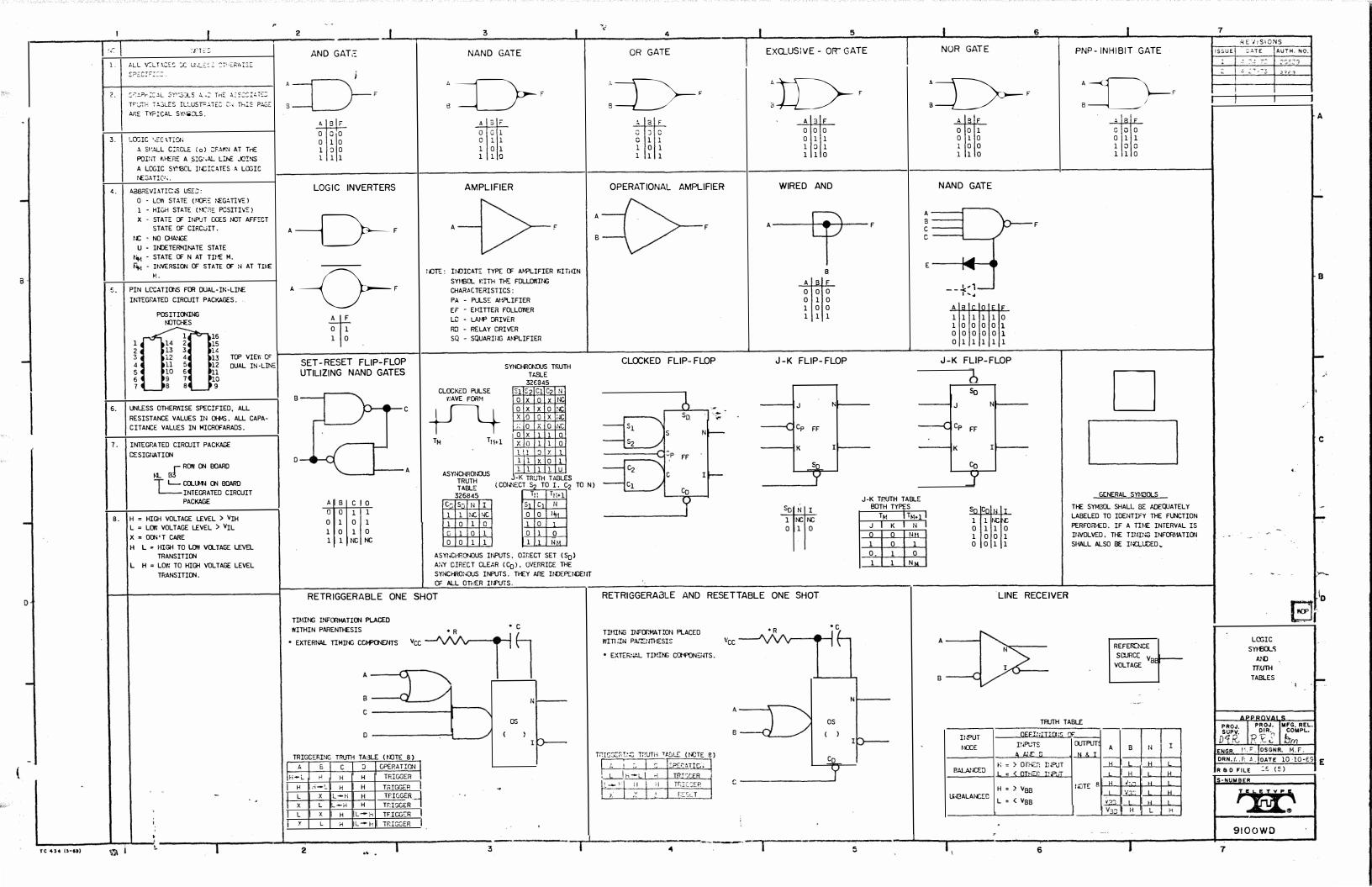

| 9100 WD     | 1       | LOGIC SYMBOLS AND TRUTH TABLES | 2 | 2        | 2        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

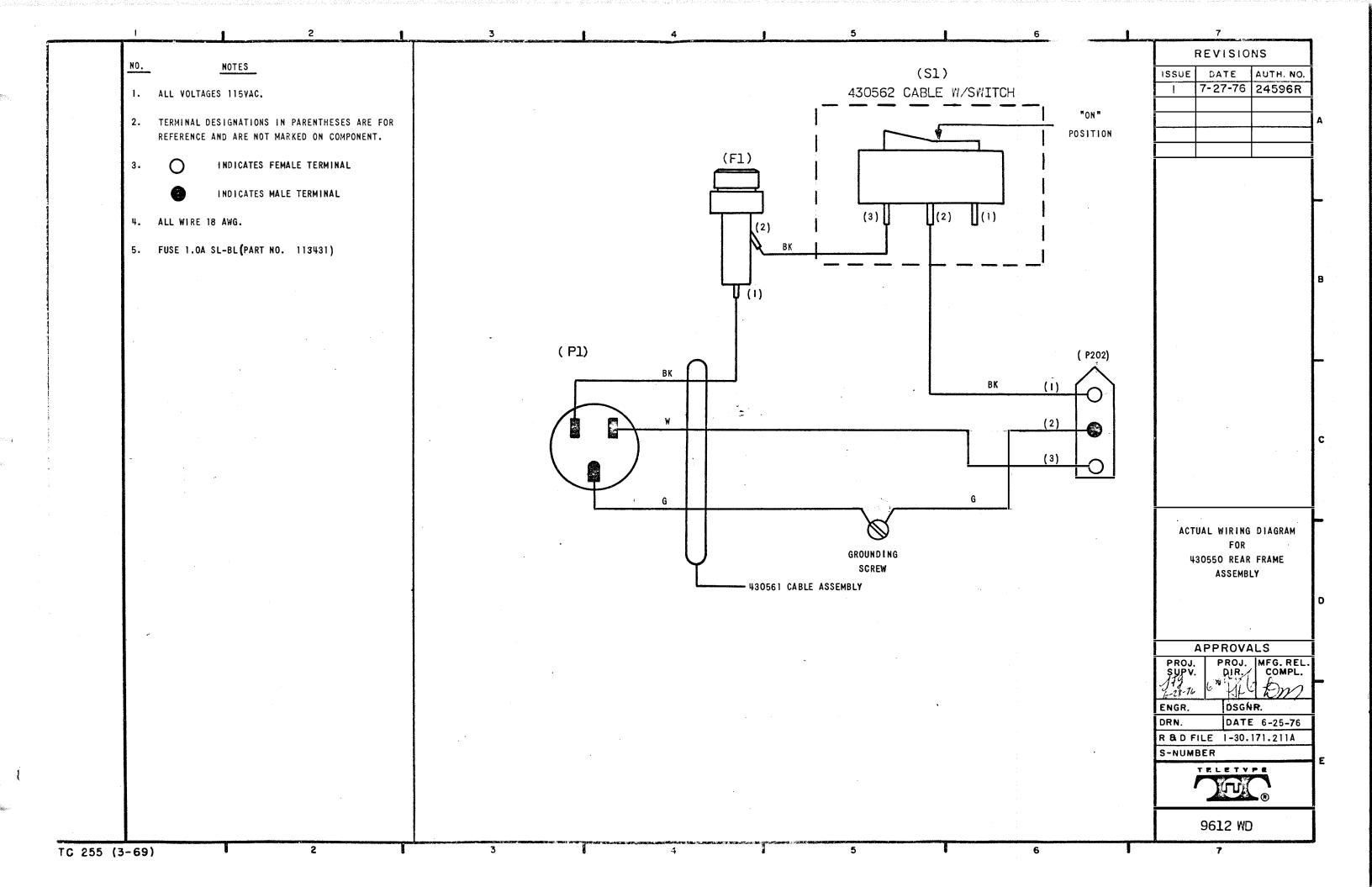

| 9612 WD     | 1       | 430550 REAR FRAME ASSEMBLY     | 1 | 1        | 1        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    | _      |

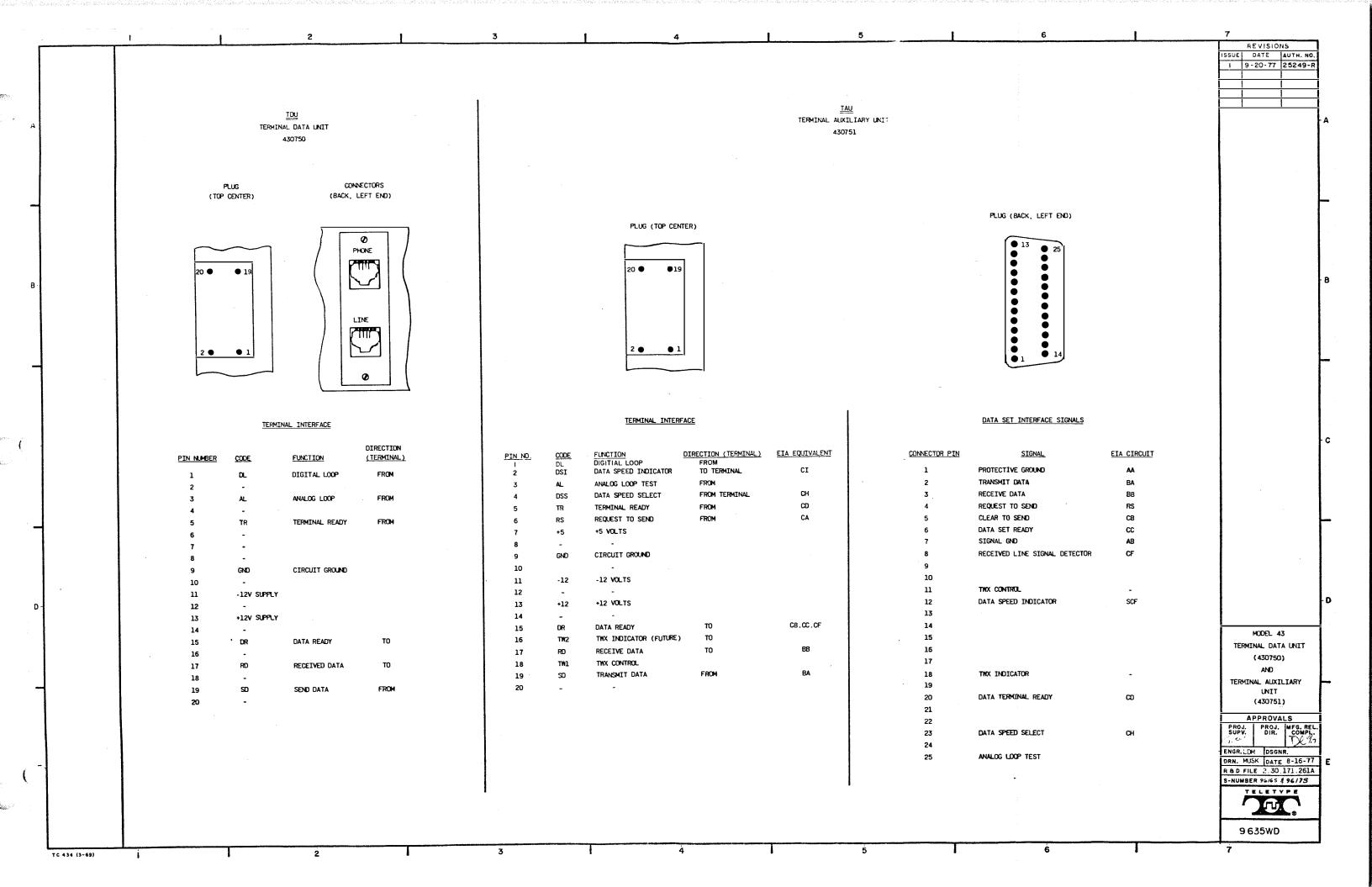

| 9635 WD     | 1       | AUXILIARY AND DATA TERMINAL    | 1 | 1        |          | _        |   | <u> </u> |   |           |   |    | <del></del> |    |    |     |          |     |          |   |    |    | <br> |    |      | <u></u> _ |         |        | +       | - -                | _      |

|             |         | CIRCUIT CARD ASSEMBLIES        |   | -        | -        | <u> </u> |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        | +       | -                  |        |

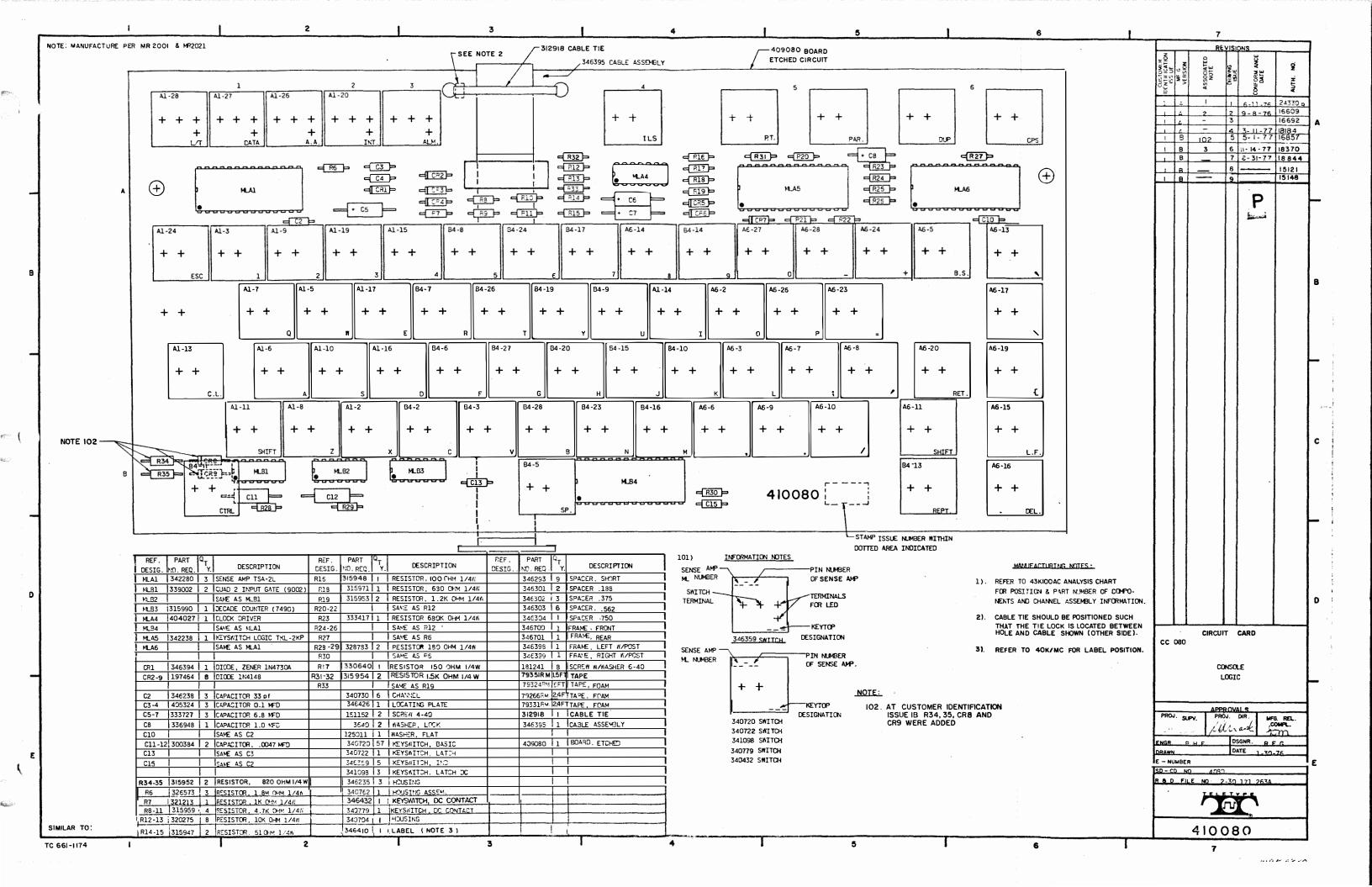

| 410080      | 1       | CONSOLE LOGIC                  | 6 | 7        | 7        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

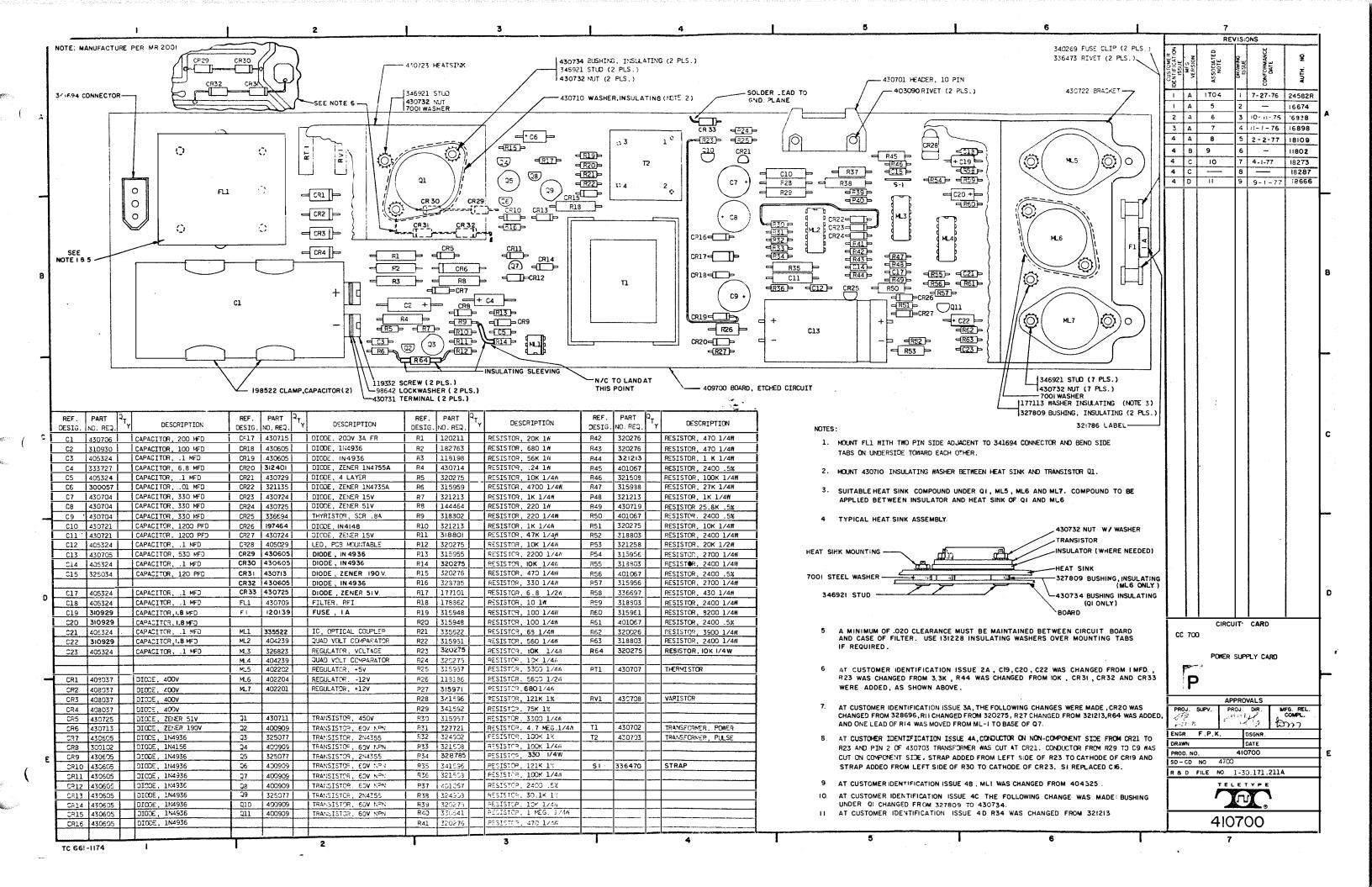

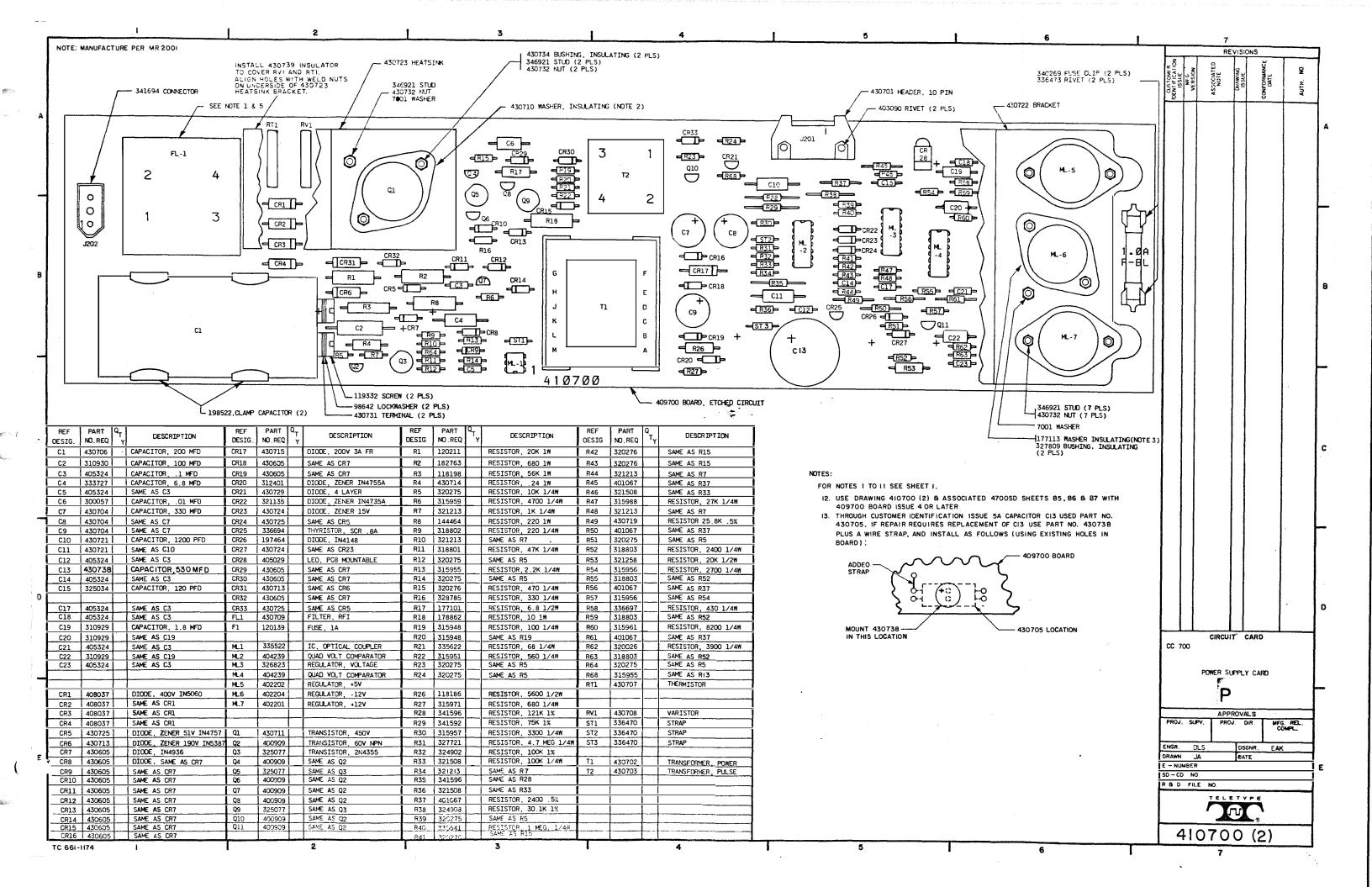

| 410700      | 1       | POWER SUPPLY                   | 9 | 9        | 9        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

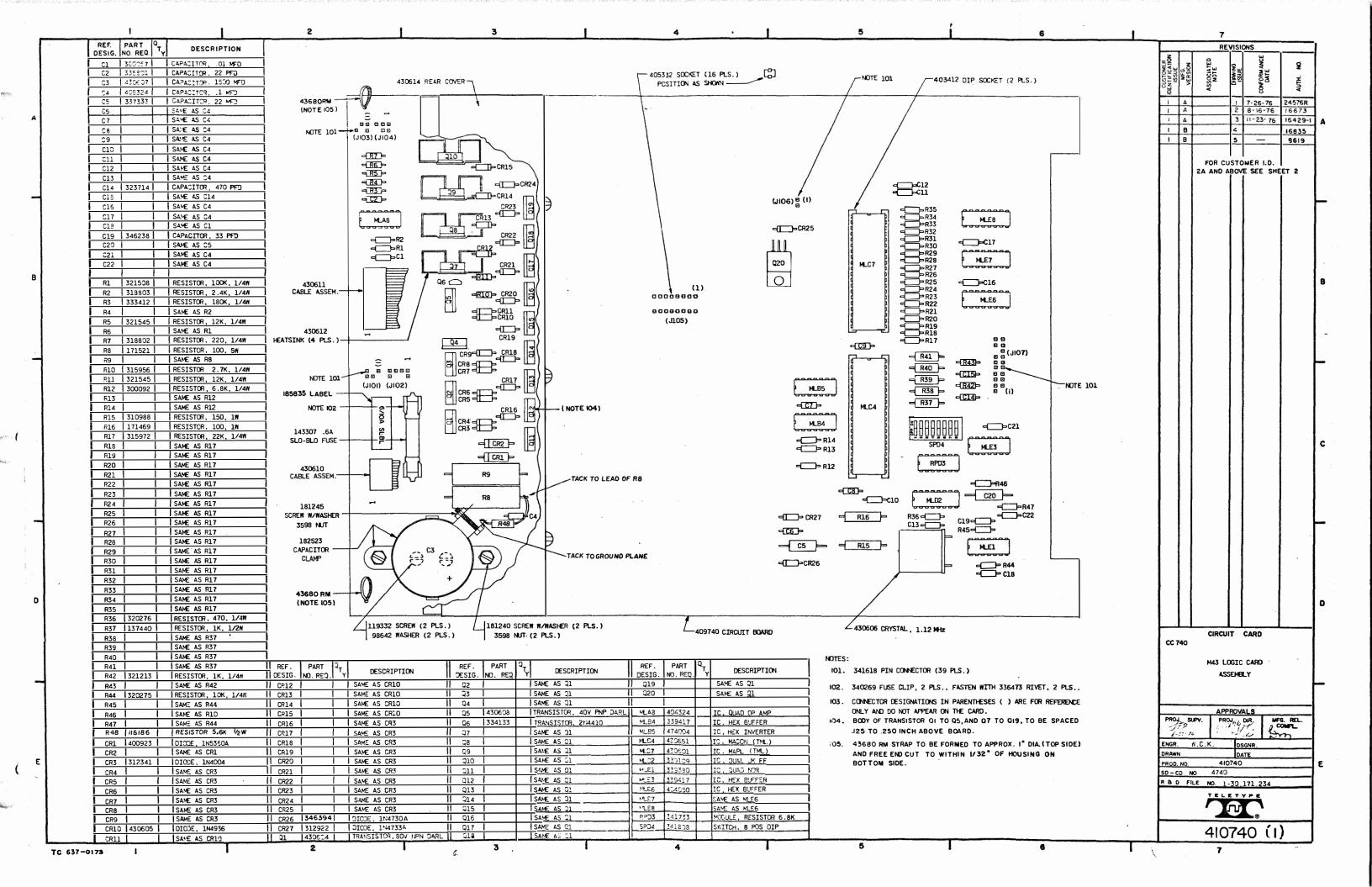

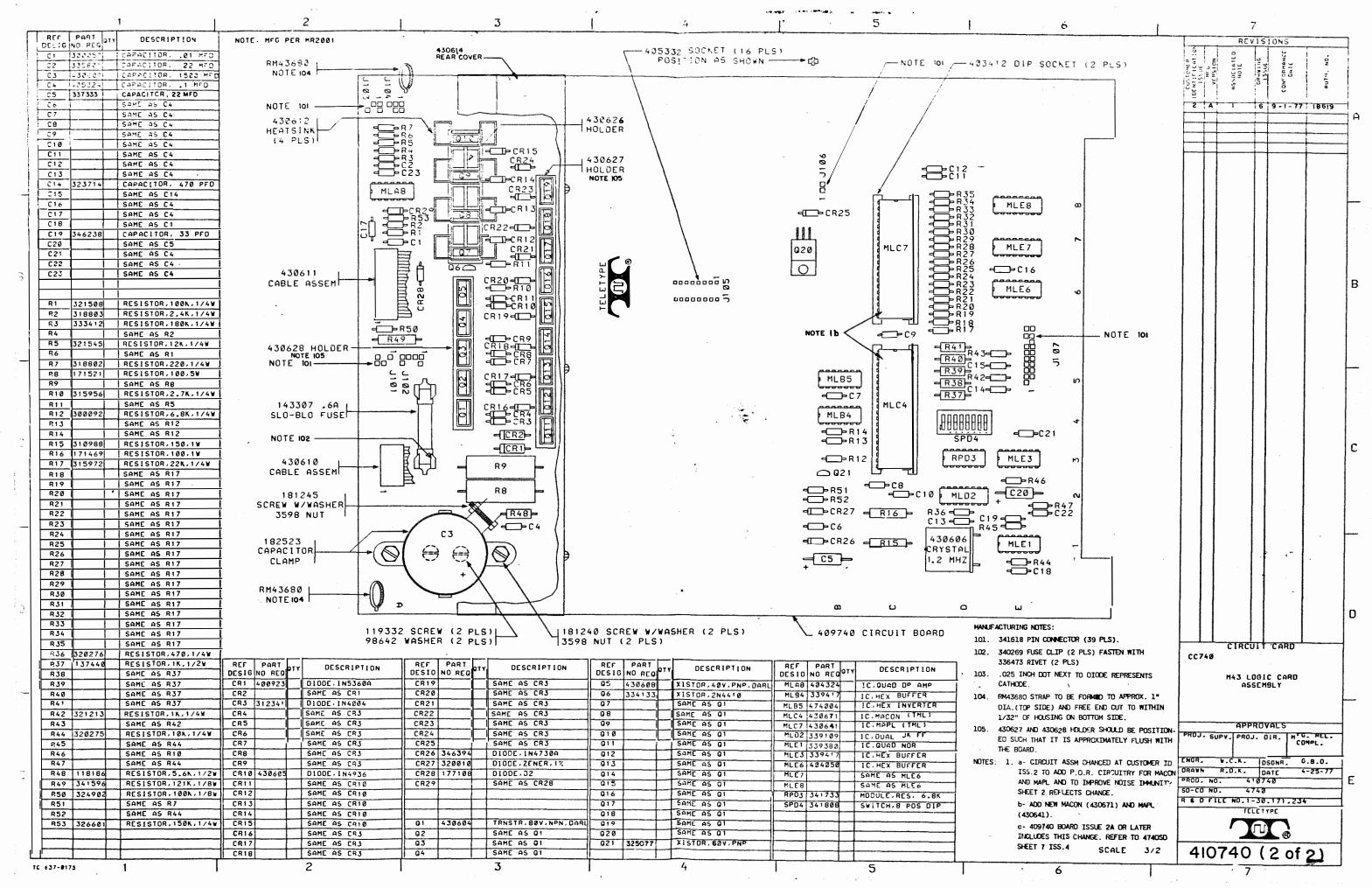

| 410740      | ALL     | K.P. LOGIC                     | 6 | 6        | 6        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

|             |         |                                |   |          |          |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

|             |         | CIRCUIT CARD DESCRIPTION       |   |          |          |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

| 4700 CD     | ALL     | POWER SUPPLY                   | 1 | ſ        | ı        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           | $\perp$ | $\bot$ |         | $oldsymbol{\perp}$ |        |

| 4740 CD     | ALL     | M43 LOGIC CARD                 | 1 | 2        | 2        |          |   |          |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        |         |                    |        |

| 4080 CD     | ALL     | 410080 CONSOLE LOGIC CARD      | 2 | 2        | 2        |          |   | <u> </u> |   |           |   |    |             |    |    |     | _        |     | $\dashv$ |   |    |    |      | ,  |      |           |         | _      | $\perp$ |                    | _      |

|             |         |                                |   |          |          | <u> </u> |   |          |   | ļ <u></u> | _ |    |             |    |    |     | _        |     |          |   |    |    |      |    |      | Ц.        |         | _      |         | _                  | -      |

|             |         |                                |   |          | _        | _        |   | <u> </u> |   |           | _ | ļ  |             |    |    |     |          |     | _        |   |    |    |      |    |      | <u> </u>  |         | _ _    | _       | _                  | _      |

|             |         |                                |   |          |          | <u> </u> |   | <u> </u> |   |           |   |    |             |    |    |     |          |     |          |   |    |    |      |    |      |           |         |        | _       | _ _                | _      |

|             | <b></b> |                                |   | <u> </u> | <u> </u> | _        |   | <u> </u> |   |           | _ |    |             |    |    |     |          |     |          |   |    |    |      |    |      | <u> </u>  |         |        | _       | _ _                | _      |

|             |         |                                |   | -        |          | +        |   | <u> </u> |   |           | _ |    |             |    |    | _   | _        |     | -        |   |    | -  |      |    |      | <u> </u>  | -       |        | +       | _                  |        |

|             | 1       |                                |   | -        | _        | _        | _ | <u> </u> |   |           | _ |    |             |    |    |     | _        |     |          |   |    |    |      |    |      |           | -       | -      | +       | _                  | _      |

REVISIONS

ISSUE DATE AUTH-NO.

1 6-14-76 24330R

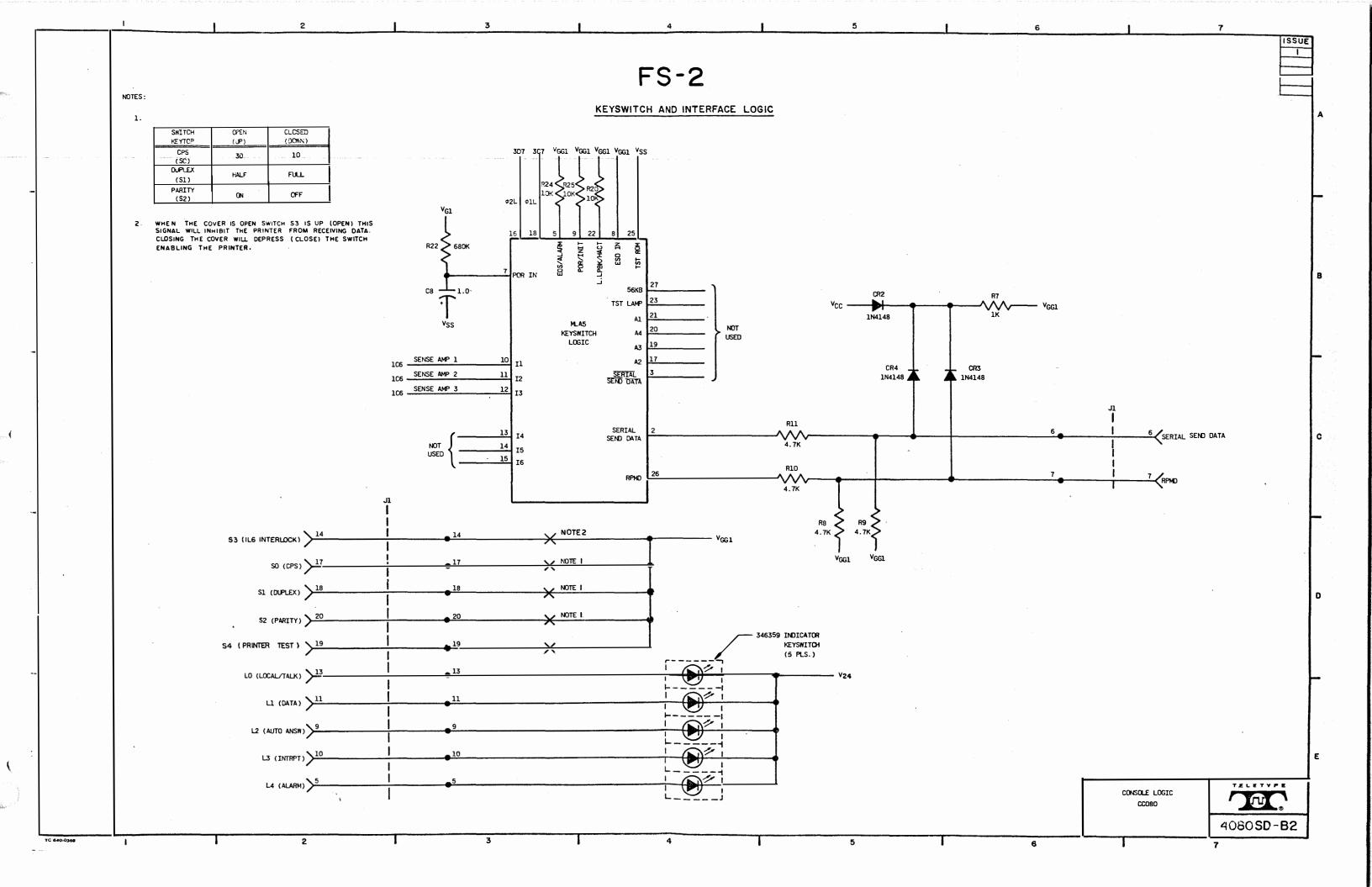

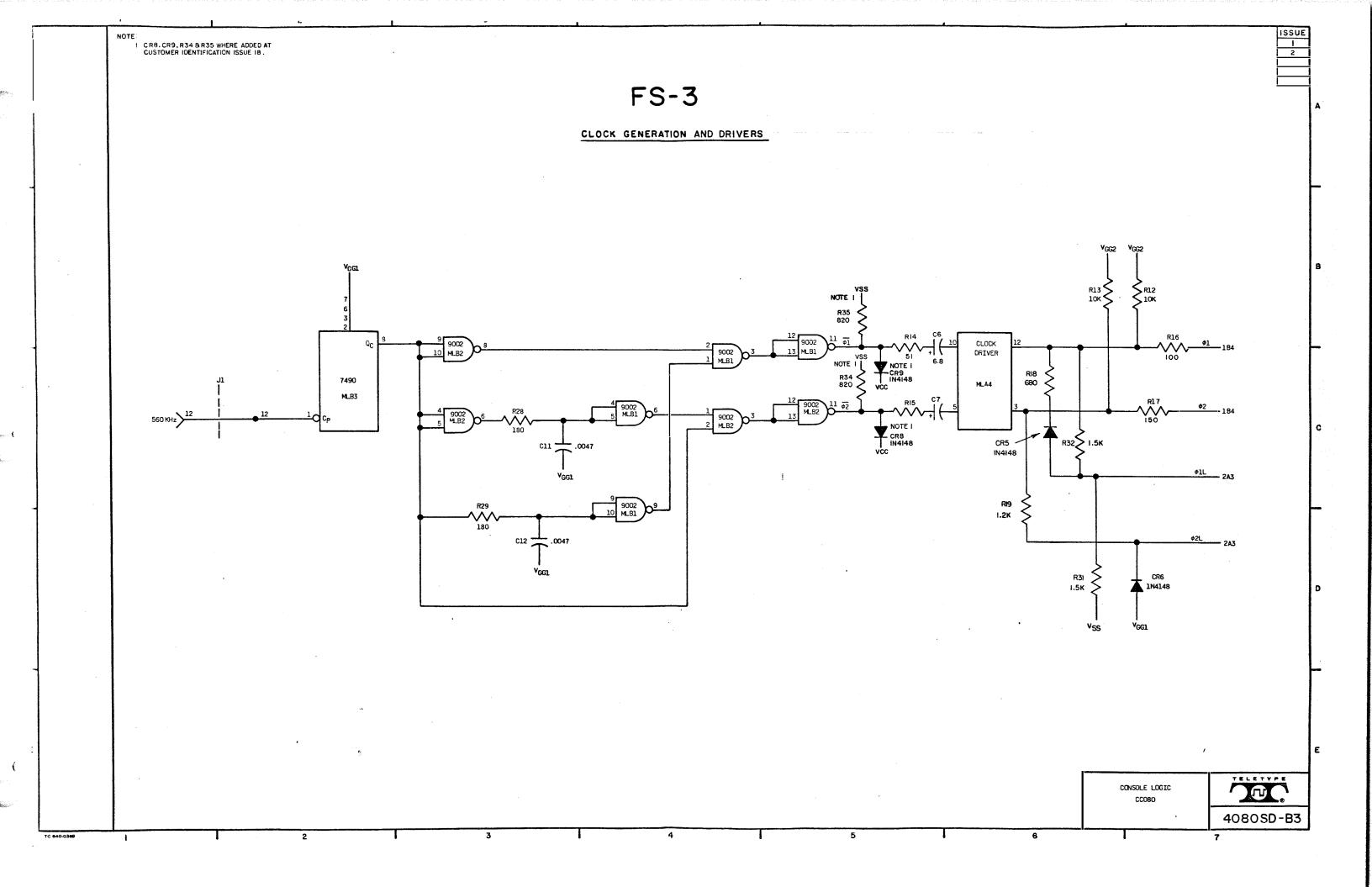

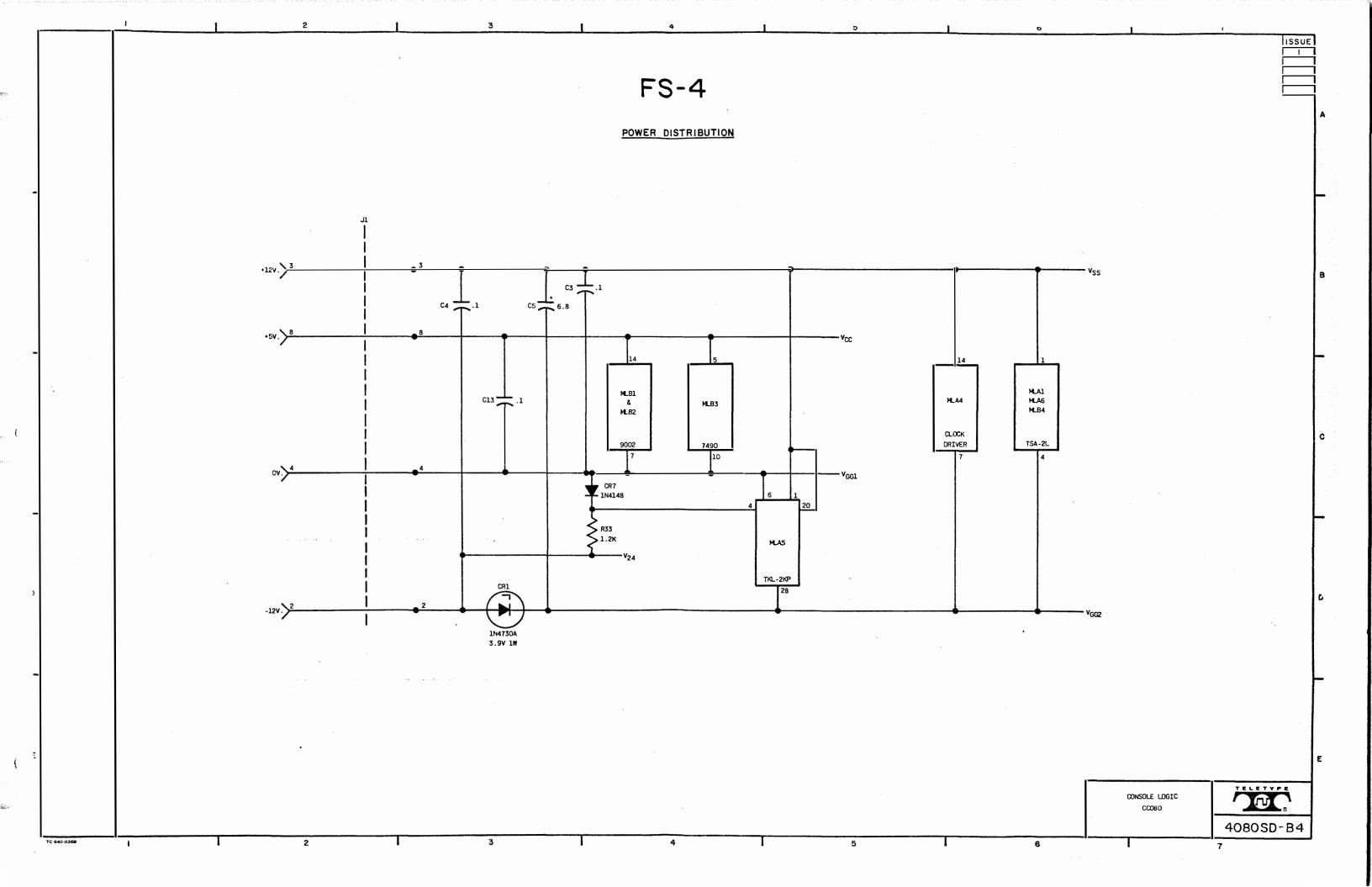

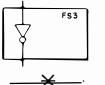

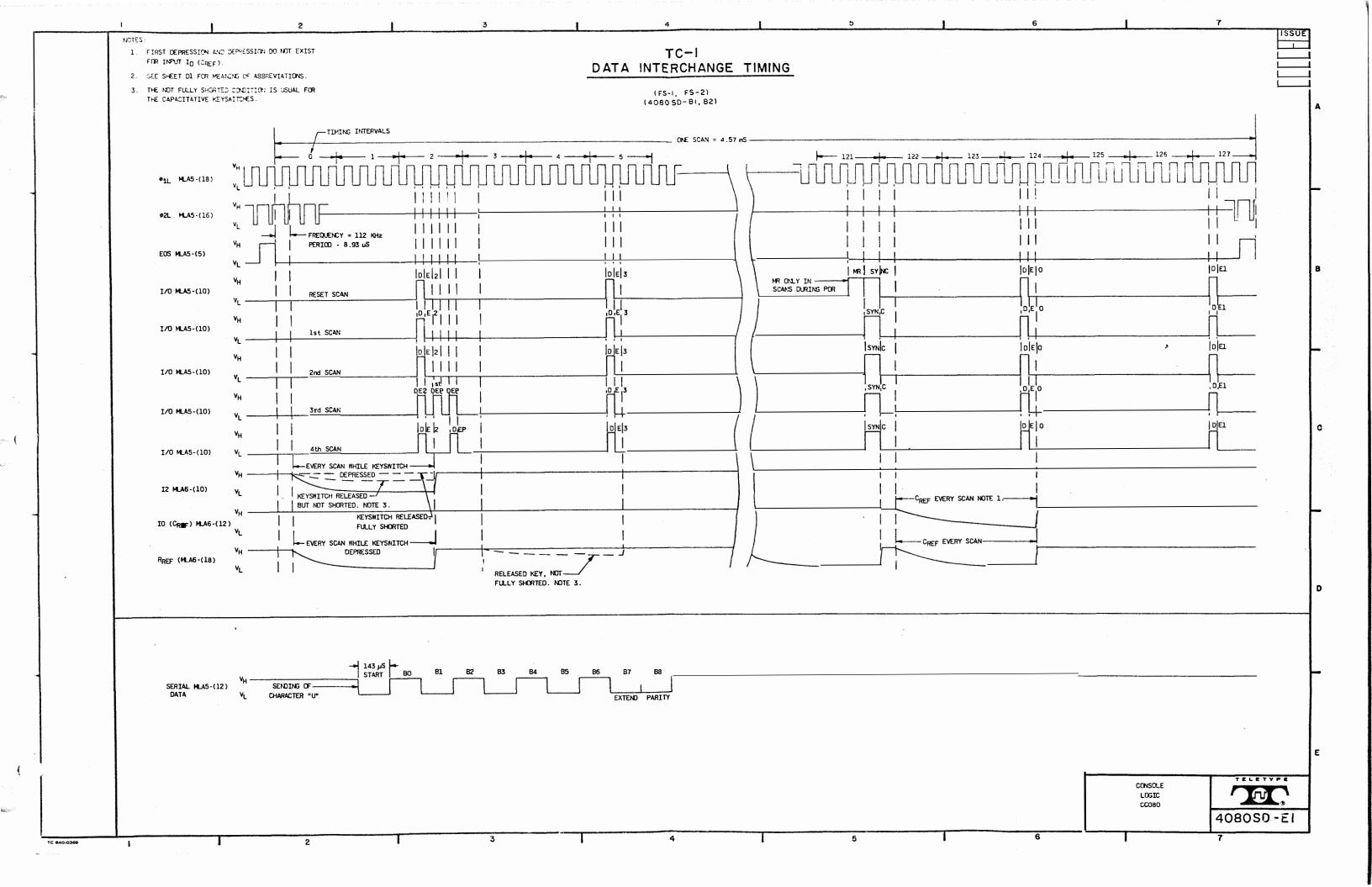

2 2-19-77 16857 SHEET INDEX USE OF SHEET INDEX SUPPORTING INFORMATION ISSUE NO. SHEET NO. SHEET NO. SHEET NO. MHÉN CHANGES ARE MACE IN CATEGORY CONTENTS NO. THIS DRAWING Al COMSOLE LOGIC 1 ONLY CHANGED SHEETS WILL BE REISSUED: \*INCLUEING SHEET 1: A1 1 2 SHEET INDEX, SUPPORTING INFORMATION CIRCUIT CARC 403000 81 81 1 | 1 FS-1 KEYSHITCHES AND SENSE AMPLIFIERS CCOSO CIRCUIT DESCRIPTION 82 1 | 1 2- UNCHANGED SHEETS FE EUSEI GAITZIKS AIAT 32 FS-2 KEYSWITCH AND INTERFACE LOGIC CIRCUIT CARD CCO80 23 CONSOLE LOGIC 410080 1 2 FS-3 CLOCK GENERATION AND DRIVERS 83 NUMBER ASSEMBLY DRAWING 84 THE LAST COMPLETED COLUMN ON THE SHEET INDEX INCI-CATES THE LATEST ISSUE PER SHEET: 84 FS-4 POWER DISTRIBUTION LOGIC SYMBOLS, TRUTH 910010 TABLES, AND GENERAL NOTES 21 Dl NOTES El El 1 TC-1 DATA INTERCHANGE TIMING E2 E2 1 TC-2 CLOCK TIMING н BD-1 CIRCUIT BLOCK DIAGRAM APPROVALS

I PROJ. MFG. REL. COMPL. PROJ. PROJ. COMPL. ENGR. RHF DSGNR. R.E.G. DRN DATE 2-2-76 R B D FILE 2-30.171.2634A S-NUMBER 62176 4080SD-A1 TC 654 (8-/1)

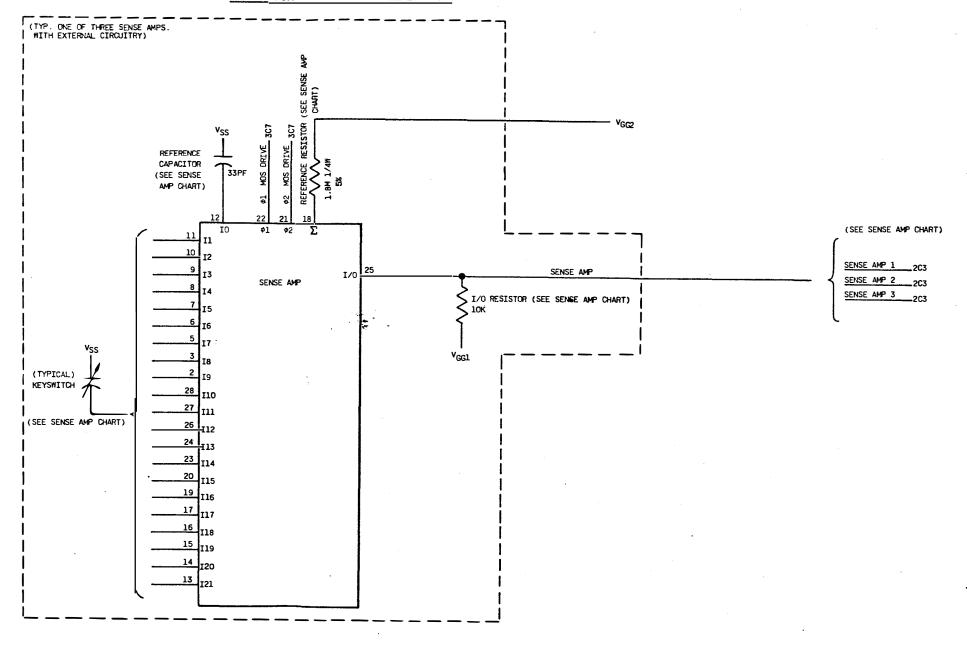

## SENSE AMP CHART

| SENSE    | SENSE AMP 1   | SENSE AMP 2     | SENSE AMP 3     |  |  |  |  |  |

|----------|---------------|-----------------|-----------------|--|--|--|--|--|

| AMP      | (MLAS)        | (MLB4)          | (MLAL)          |  |  |  |  |  |

| PIN NO.  | к             | EYTOP CHARACTER |                 |  |  |  |  |  |

| 11       | SHIFT (RIGHT) | CONTROL         | SHIFT (LEFT)    |  |  |  |  |  |

| 10       | /             | К               | S               |  |  |  |  |  |

| 9        |               | IJ              | 2               |  |  |  |  |  |

| 8        |               | 5               | Z               |  |  |  |  |  |

| 7        | ;             | Ř               | Q               |  |  |  |  |  |

| €        | , ,           | F               | Α               |  |  |  |  |  |

| 5        | BACK SPACE    | SPACE           | W               |  |  |  |  |  |

| 3        | L             | V               | 1               |  |  |  |  |  |

| ` 2      | 0             | С               | х               |  |  |  |  |  |

| 28       | -             | В               | LO(LOCAL TALK)  |  |  |  |  |  |

| 27       | O (ZERO)      | G               | 니 (DATA)        |  |  |  |  |  |

| 26       | Р             | T               | L2 (AUTO. ANSW) |  |  |  |  |  |

| 24       | +             | 6               | ESCAPE          |  |  |  |  |  |

| 23       | =             | N               | (CPT. SPARE)    |  |  |  |  |  |

| 20       | RETURN        | н               | L3 (INTRPT)     |  |  |  |  |  |

| 19       | {             | Y               | 3               |  |  |  |  |  |

| 17       | \             | 7               | E               |  |  |  |  |  |

| 16       | DELETE        | М               | D               |  |  |  |  |  |

| 15       | LINE FEED     | J               | 4               |  |  |  |  |  |

| 14       | 8             | 9               | I               |  |  |  |  |  |

| 13       | •             | REPEAT          | CAPS LOCK       |  |  |  |  |  |

|          | RĒ            | FERENCE RESISTO | R               |  |  |  |  |  |

| 18       | R27           | R <b>3</b> 0    | R6              |  |  |  |  |  |

| <u> </u> |               |                 | l               |  |  |  |  |  |

|          |               | I/O RESISTOR    |                 |  |  |  |  |  |

| 25       | R26           | R21             | R22             |  |  |  |  |  |

| 25       | KEYSWITCH L   | OGIC(MLA5) INPU | T PIN NO.       |  |  |  |  |  |

| L        | 10            | 11              | 12              |  |  |  |  |  |

| 12       | RE            | FERENCE CAPACIT | OR              |  |  |  |  |  |

|          | C10           | C15             | C2              |  |  |  |  |  |

CONSOLE LOGIC CCO80 4080 SD - BI

\_\_\_\_

-

2

5

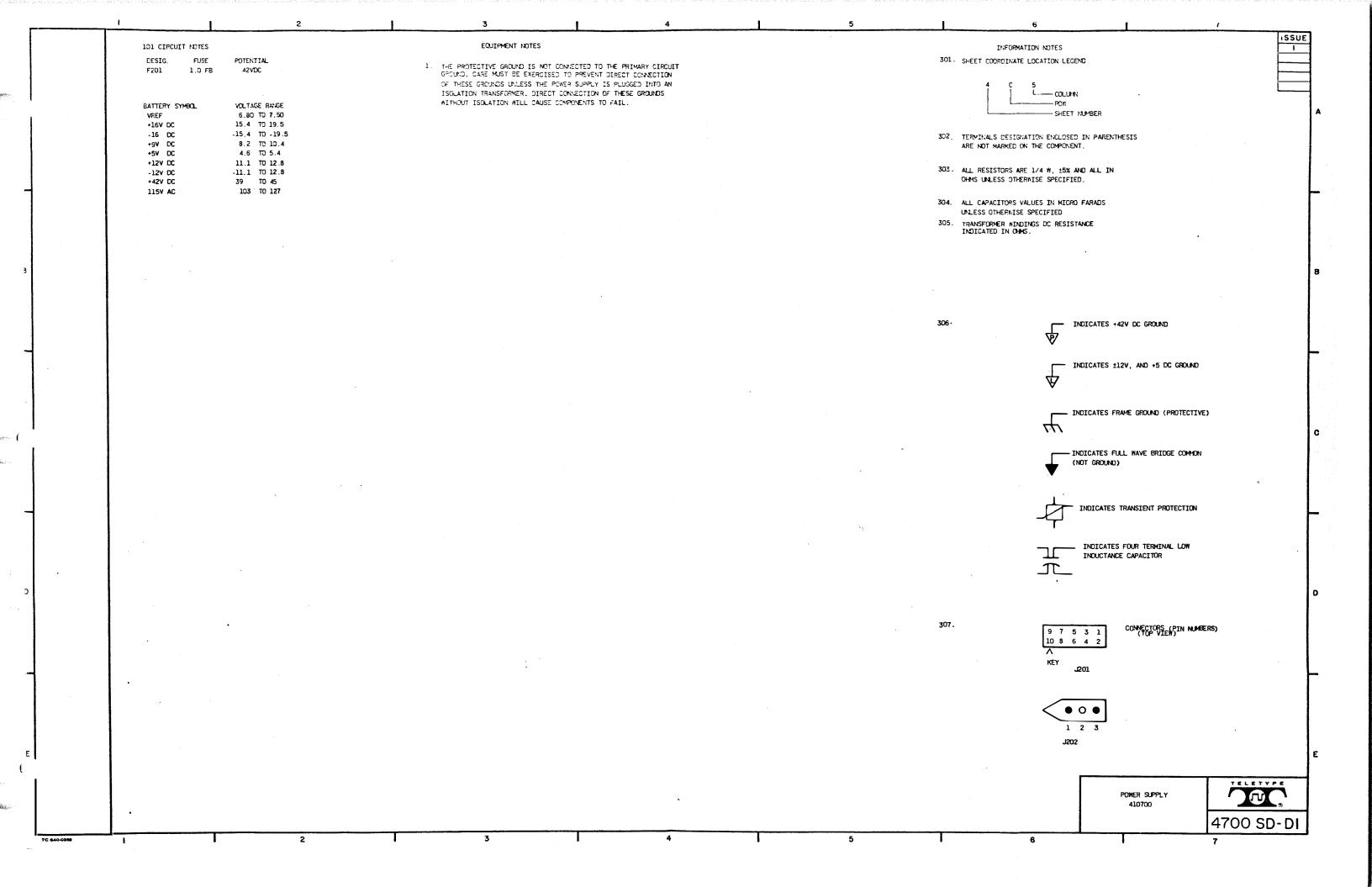

EQUIPMENT NOTES

CIRCUIT NOTES

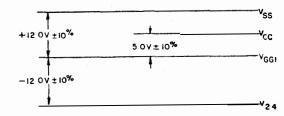

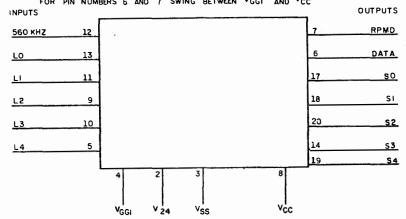

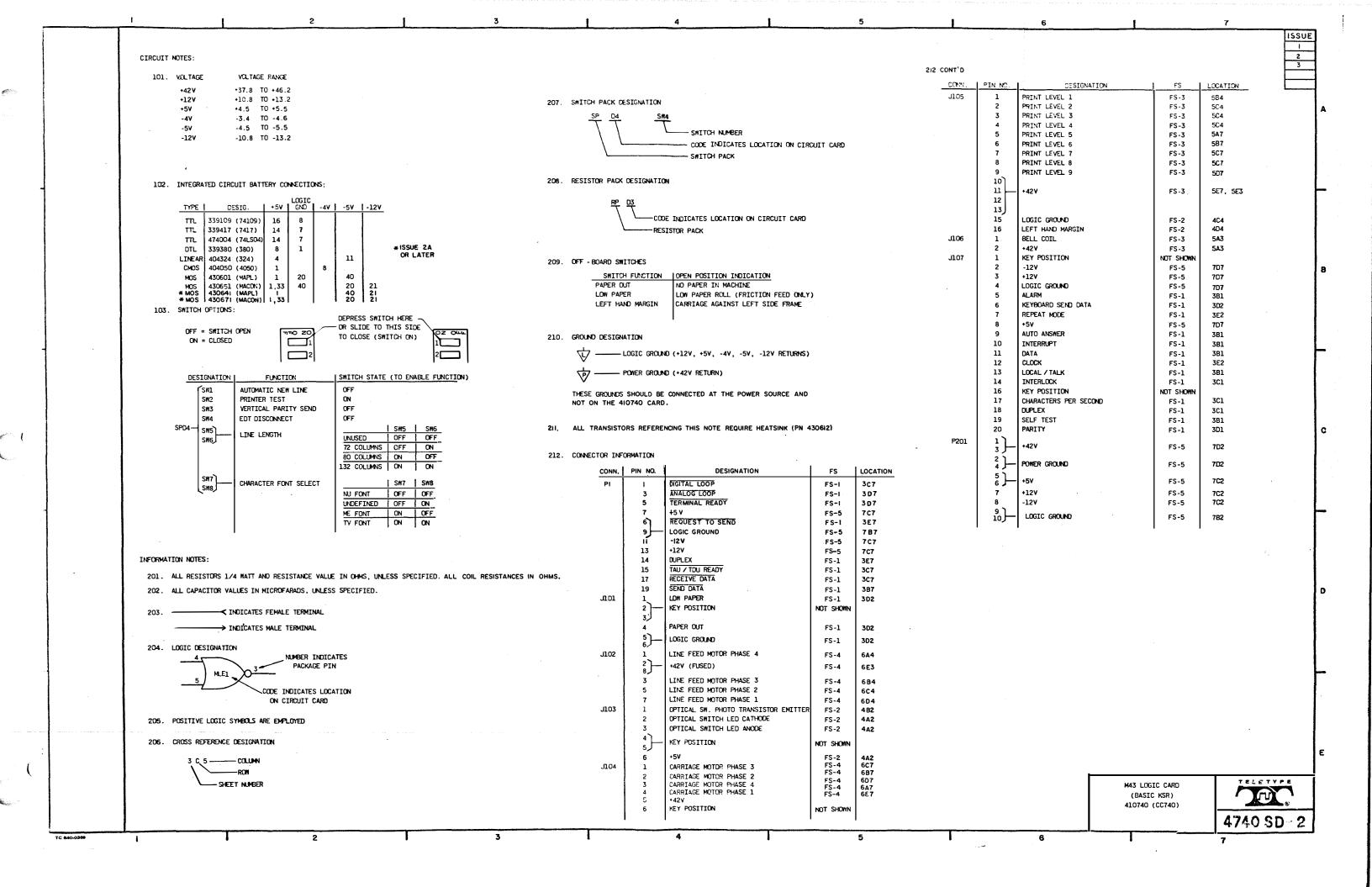

101. SUPPLY VOLTAGES: THE FOLLOWING VOLTAGES ARE MEASURED IN RESPECT TO VGG1.

102. SIGNAL VOLTAGES:

THE INPUT VOLTAGE FOR PIN NUMBER 12 SWINGS BETWEEN VGGI AND VCC. THE INPUT VOLTAGES FOR PIN NUMBERS 13,11,9,10, \$ 5 SWING BETWEEN V24 AND V24 + 2.0 V. THE OUTPUT VOLTAGES FOR PIN NUMBERS 14, 17,18,19 & 20 ALL SWING BETWEEN VGGI AND VCC. THE OUTPUT VOLTAGES FOR PIN NUMBERS 6 AND 7 SWING BETWEEN VGGI AND VCC

INFORMATION NOTES

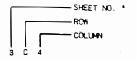

301. SHEET COOPDINATE LOCATION LEGEND:

SECTION LETTERS ARE NOT REQUIRED UNLESS REFERENCE IS TO OTHER SECTIONS. OF THE DRAWING, WHEN SECTION LETTERS ARE REQUIRED, THE SECOND LETTER SHALL PRECEDE THE SHEET NO., (E.G. BID4).

302. TERMINAL DESIGNATIONS ENCLOSED IN PARENTHRSES ARE FOR REFERENCE AND ARE NOT MARKED ON COMPONENTS.

303. ALL RESISTANCE VALUES IN OHMS UNLESS OTHERWISE SPECIFIED.

304. ALL RESISTORS ARE 1/4 WATT UNLESS OTHERWISE SHOWN.

305. ALL CAPACITANCE IN MICROFARADS UNLESS OTHERWISE SPECIFIED.

306. SYMBOLS:

SIGNAL GROUND

LETTER OR TITLE IN CIRCLE INDICATES PRESENCE OF AN

OPTION WHICH THE CUSTOMER CAN ARRANGE TO SUIT HIS CHOICE OR REQUIREMENT WITHIN THE POSSIBILITIES SHOWN.

CIRCUITRY WITHIN SINGLE SOLID LINE ENCLOSURE IS SHOWN FOR REFERENCE ONLY. IT IS SHOWN IN DETAIL ELSEWHERE IN THE SAME SD.

NORHALLY OPEN CONTACT

TEST POINT

307. ABBREVIATIONS:

DE - DATA ENABLE DEP - DEPRESSION MR - MASTER RESET

EOS - END OF SCAN

I/O - INPUT/OUTPUT

I - INPUT Σ - SUMMATION POR - POWER ON RESET

RPMD - REPEAT MODE RREF - REFERENCE RESISTOR

ISSUE

KL - KEYSWITCH LOGIC CREF- REFERENCE CAPACITOR

CONSOLE LOGIC CC080

4080SD - DI

TC-2 CLOCK TIMING (FS-3) (4080SD-83) 1.79 µS PERIOD NOTE 1. \$\phi \text{ AND \$\phi L , \$\phi 2 \text{ AND \$\phi 2L HAVE THE SAME TIMING AND LOGIC SENSE, BUT DIFFERENT VALUES OF \$V\_L\$. MLB3-(1) ÷5 OUTPUT MLB3-(8) MLB1-(6) MLBI-(B) (PREDRIVE) MLBI-(II) (PREDRIVE) MLB2-(11) \$2 DRIVE NOTE I OF DRIVE MLA4-(12) TELETYPE OPIC. CONSOLE LOGIC 4080SD-E2

|                                                        |          |   | 1        |     |     |   | 6 D F F | T 1805 | ~    |      |    |         |      |       |     | , J      |               |                  |        |        |                | 2110202                                 | TING INFORMA  | TION            | REVISIONS<br>TUA TAC SURVEY<br>1 8-3-75 245 |

|--------------------------------------------------------|----------|---|----------|-----|-----|---|---------|--------|------|------|----|---------|------|-------|-----|----------|---------------|------------------|--------|--------|----------------|-----------------------------------------|---------------|-----------------|---------------------------------------------|

| 201151172                                              | SHEET    |   |          |     |     |   |         | TINDE  |      |      |    | ISSUE N | NO   |       |     |          |               |                  | TT-    |        | SHEET          | CATEGO                                  |               | NO.             | 2 9-10-76 166                               |

| CONTENTS                                               | NO.      | 1 | 2        | 3 4 | 5   | 6 | 7   9   | 9      | 10 1 | 1 12 | 13 | 14 19   | 5 16 | 17 18 | 191 | 20   21  | 22            | 23   24          | 25   2 | 6   27 | 28 NO.         | CIRCUIT DESCRIPTION                     |               | 470000          | 4   11-24-76   168                          |

| SHEST INCEX SUPPORTING INFORMATION                     | Al       | 1 | 2        | 3 4 | 5   | ε |         |        |      |      |    |         |      |       |     |          | $\perp \perp$ | _                |        |        | Al             | 430700 POWER SURPL                      |               | 47000           | 5 2 2 - 77 1316<br>6 8-4-77 186             |

|                                                        |          |   |          |     |     |   |         |        |      | _    |    |         | -    |       | +   |          | ++            |                  | ++     | -      | 21             | ACTUAL MIRING DIAG<br>430550 REAR FRAME |               | 961240          | -                                           |

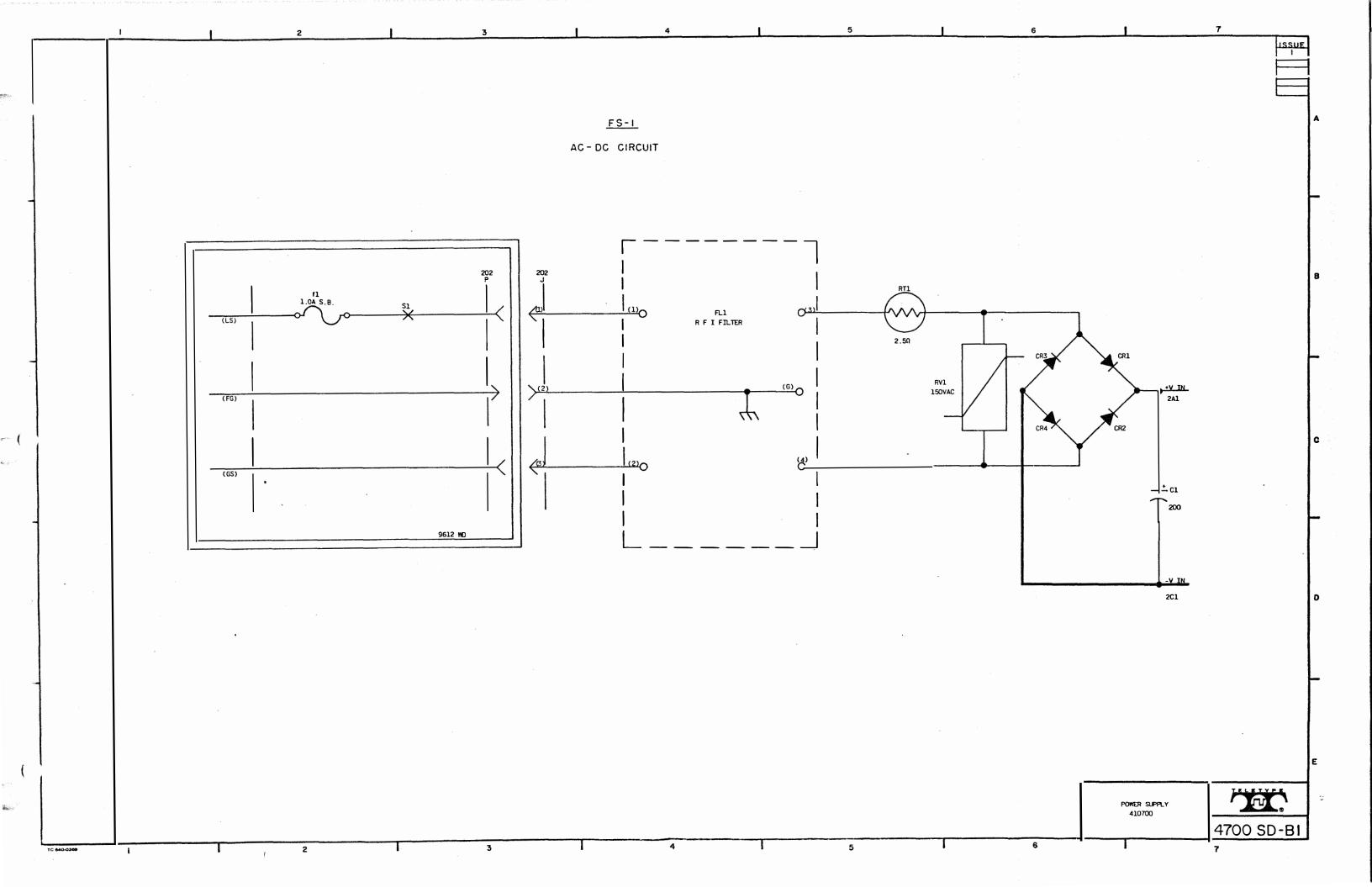

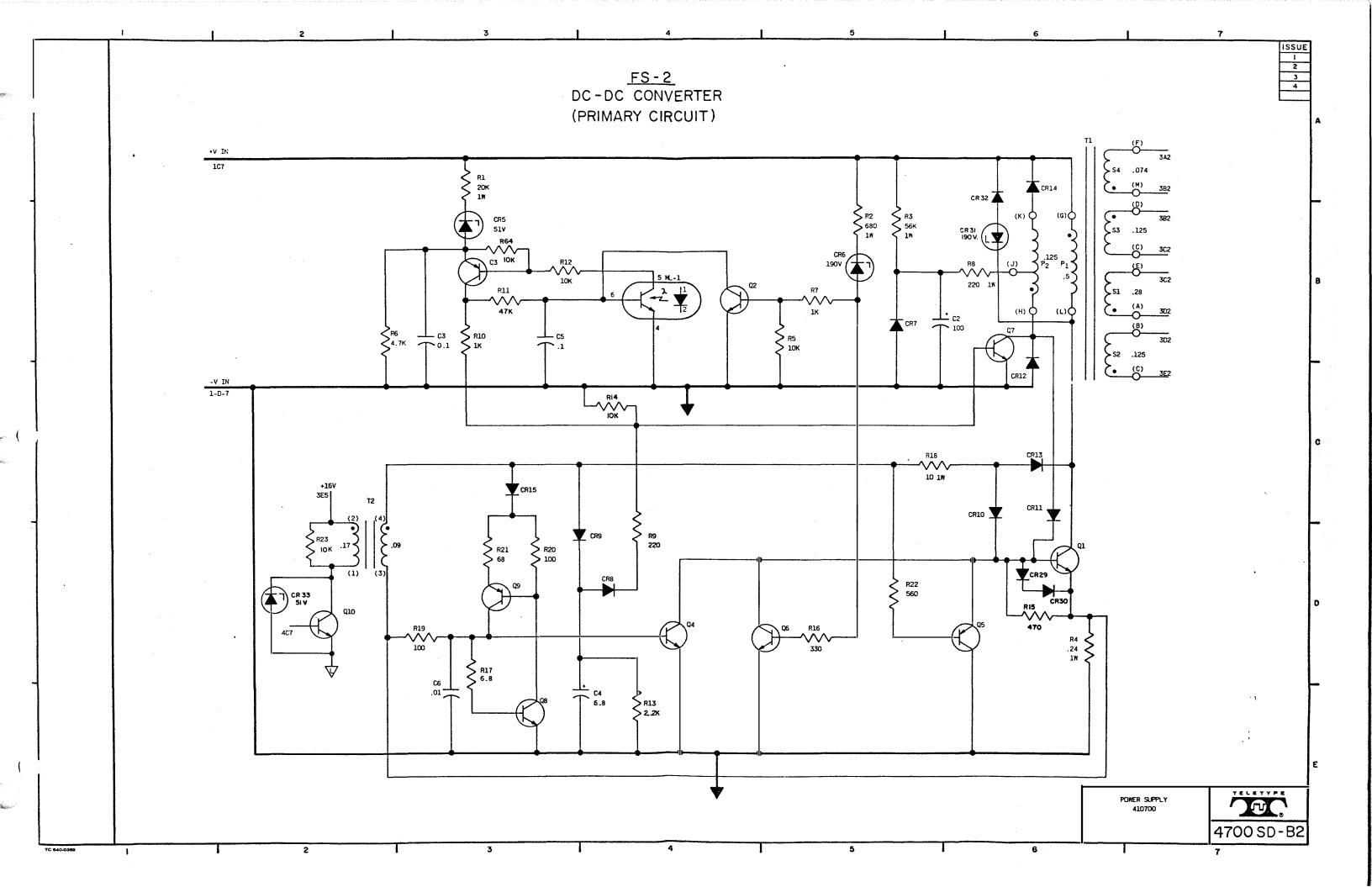

| FS-1 AC-DC CIRCUIT FS-2 EC-DC CONVERTER (PRIMARY)      | £1<br>£2 |   | 1 2      | 3 4 | 4   |   | - 1     |        |      |      | 1  |         | 1    |       | 1 1 | 1        | 1 1           | <del>- } -</del> |        | 1      | B5             | 40000 NEAR THAT E                       |               |                 |                                             |

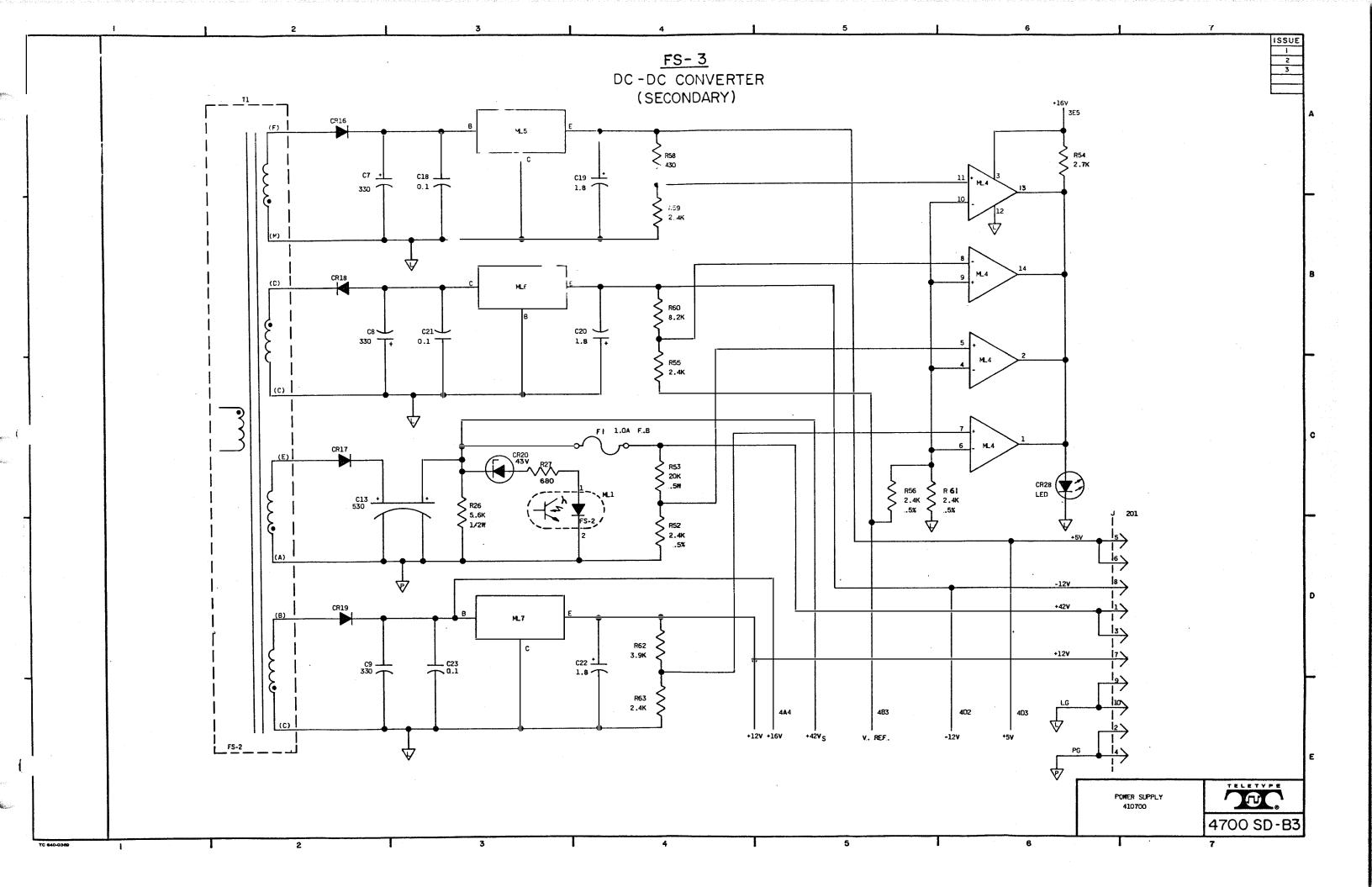

| FS-3 DO-DO CONVERTER (SECONDARY)                       | 83       | _ |          | 2 3 |     |   | İ       |        |      |      | İ  |         | 1    |       |     |          |               | 1                |        |        | B3             |                                         |               |                 |                                             |

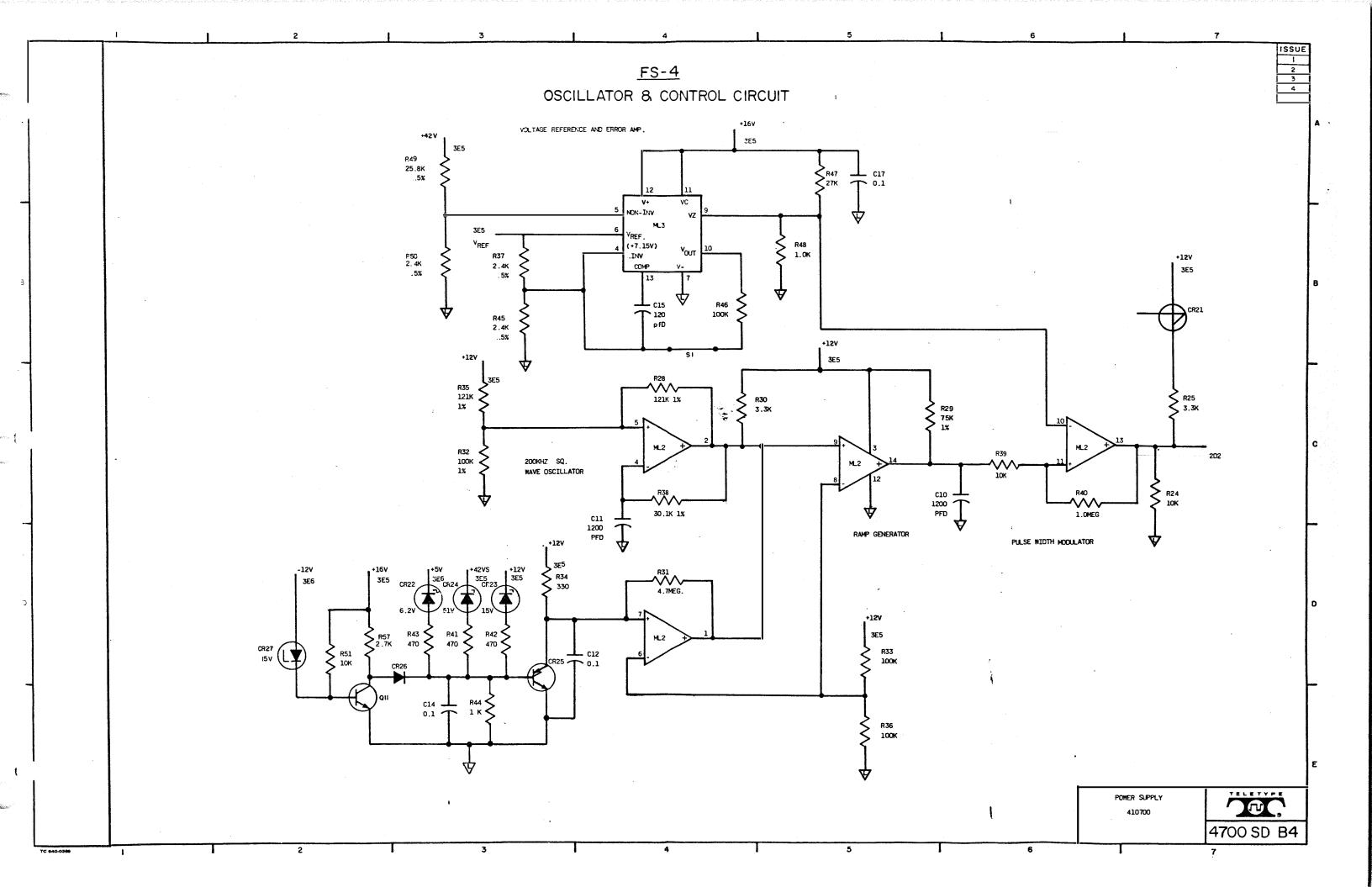

| FS-4 OSCILLATOR & CONTROL CIRCUIT                      | 84       | 1 |          | 2 2 | 3   | 4 | _       |        |      |      | -  |         | -    |       | ++  |          | +             |                  | +      |        | B4             |                                         |               | 1.              |                                             |

| CIRCUIT MOTES ECUIPMENT NOTES INFORMATION NOTES        | C1       | 1 | i        | 1   |     | 1 |         |        |      |      |    |         |      |       |     |          |               |                  |        |        | C1             |                                         |               |                 |                                             |

| NOT TACE CHOOSENT WAVE FORMS                           | E1       | 1 |          | -   | 1 1 | 1 | -       | +      |      | +    | 1  |         | 1    |       | ++  | +        | + +           | -                | 1 1    | 1      | El             |                                         |               |                 |                                             |

| VOLTAGE-CURRENT WAVE FORMS  VOLTAGE-CURRENT WAVE FORMS | E2       | 1 | <u> </u> | 1   |     |   | i       |        |      |      | Ì  |         |      |       |     |          |               |                  |        |        | E2             |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         | _ !  |       |     | <u> </u> | 1 !           |                  | 1 1    |        | 1 1            |                                         |               |                 |                                             |

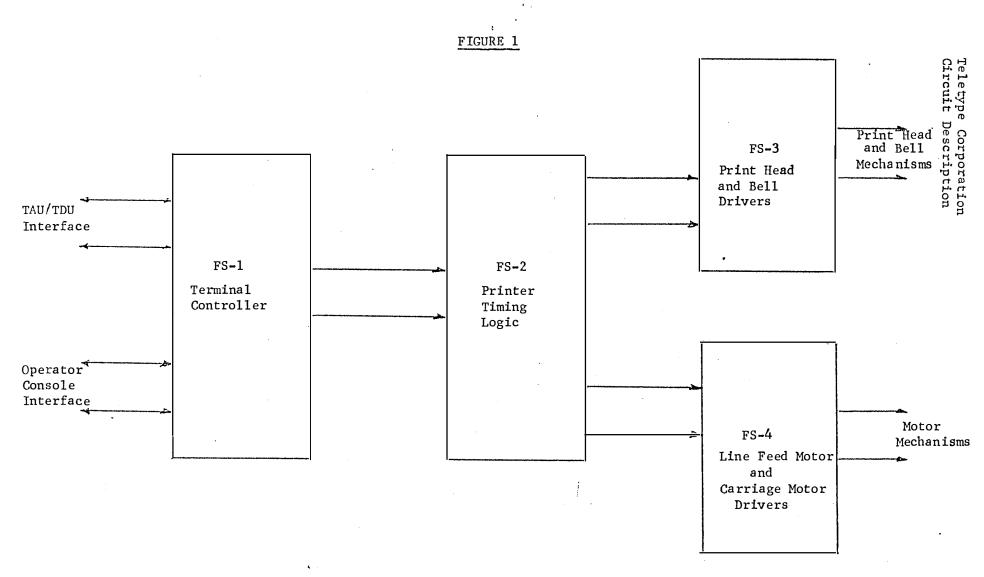

| FS BLOCK DIAGRAM                                       | H1       | 1 | 1        | 1   | '   | 1 |         | +      |      |      | 1  |         | - 1  |       | 1 1 | 1        | 1 1           | <del>- }-</del>  | 1 1    | 1      | 1 1 н <u>а</u> |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      | -    |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      | ١     |     | -        |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       | 1   |          |               |                  |        |        |                |                                         | RE MADE IN TH | IS DRAWING ONLY |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      | ļ  |         |      |       |     |          |               |                  |        |        |                | 2. THIS SHEET IND UPDATED EACH          | Y WILL BE BE  | ISSUED AND      |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        | Ì      |                | DRAWING IS REIS                         | SUED OR A NE  | W SHEET IS      |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                | 3. THE LAST COMP                        | ETED COLUMN   | INDICATES THE   |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                | LATEST ISSUE I                          |               | · ·             |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                | THEIR EXISTIN                           | S ISSUE NO.   | i               | <b>.</b>                                    |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     | .        |               | -                |        |        | i              | INDEX ONLY.                             | LL BE SHOWN   | ON THE SHEET    | 1                                           |

|                                                        |          |   |          |     |     |   | İ       |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   | \       | '      |      |      |    |         |      |       |     |          |               |                  |        | 1      |                |                                         |               |                 | · ·                                         |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                | _                                       |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     | -        |               |                  |        |        | [              |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     | - |         | •      | -    |      |    |         | •    | -     |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         | •             |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                | •                                       |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         | ,             |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 | APPROVALS                                   |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 | PROJ. PROJ. MFG<br>SUPV. DIR. CO            |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         | •             |                 | ENGR. DIS IDSGNR.                           |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 | DRN. DATE<br>R&D FILE 1-30.171.             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 | R & D FILE 1-30.171.<br>S-NUMBER            |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         |               |                 |                                             |

|                                                        |          |   |          |     |     |   |         |        |      |      |    |         |      |       |     |          |               |                  |        |        |                |                                         | •             |                 | 4700 SD-                                    |

|                                                        |          |   |          |     |     |   |         |        |      |      |    | -       |      |       |     |          |               |                  | 5      |        | <del></del>    | 6                                       |               |                 | 7                                           |

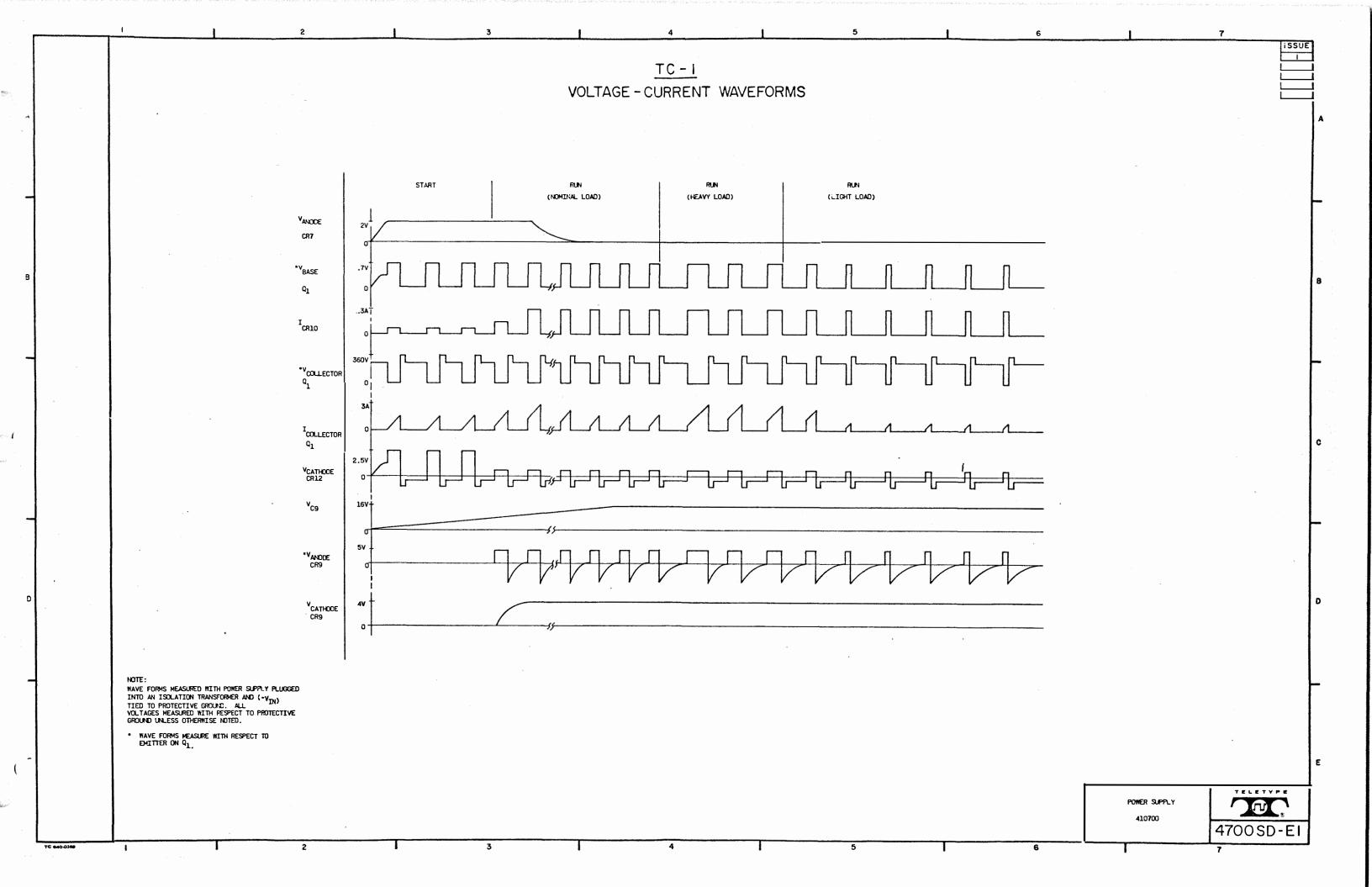

TC-2 VOLTAGE - CURRENT WAVEFORMS OSCILLATOR DRIVEN MODE +12V 20 KHZ SQUARE WAVE OSCILLATOR ML2-2 RAMP GENERATOR ML2-14 + 3.5V OV CONTROL VOLTAGE ML3-9 + 5V **0y** PULSE NIDTH HODULATOR ML2-13 + 1.0V OV PULSE TRANSFORMER DRIVE Q10-COLLECTOR +30v +20V +107 POWER SUPPLY 410700 4700 SD E2

|    |                                                |       |            |                                                   |       |                  | SHI              | EET IN           | IDEX |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          | SUPPORTING INFOR                                                                                                                                         | AATION ·                                                          | REVISIONS<br>  ISSUE   DATE   AUT<br>  1   8-2-76   24            |

|----|------------------------------------------------|-------|------------|---------------------------------------------------|-------|------------------|------------------|------------------|------|--------------------------------------------------|-------------|------|--------------------------------------------------|--------|----------|----------|-----|--------|--------------|--------------------------------------------------|------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| -  | CONTENTS                                       | SHEET |            |                                                   |       |                  |                  |                  |      |                                                  |             | ISSU | E NO.                                            |        | ·        |          |     |        |              | T                                                |                  |     | SHEET    | CATEGORY                                                                                                                                                 | NO.                                                               | 2 9-28-76 16                                                      |

| _  |                                                | NO.   | 111        | 2 3                                               | 4     | _                | 7                | 8   9            | 10   | 11                                               | 12   13     | 14   | 15                                               | 6   17 | 1 18     | 9   20   | 21  | 22   2 | 5   24       | 25   3                                           | 26 27            | 28  | NO.      |                                                                                                                                                          | <del></del>                                                       | 3   11-15-76   16<br>4   6-15-77   18                             |

| -  | SHEET INCEX, SUPPORTING INFORMATION            | 2     | + + +      | -                                                 | 2     |                  |                  | $\dashv$         | +    |                                                  |             | +-   | -                                                | -      |          | _        | +-+ | _      | +            |                                                  |                  | +-+ | 2        | CIRCUIT CESCRIPTION<br>SCHEMATIC DIAGRAM                                                                                                                 | 4740CD<br>4013SD                                                  | 5  0-25-77   18                                                   |

| -  | NOTES                                          | 3     | +;+        | <del>,                                     </del> | -     | 2 3              | -                | _                | 1-   |                                                  |             | 1-1  |                                                  |        | ++       | +-       | 1   | -      |              | 1-1-                                             |                  | +   | 3        | CIRCUIT DESCRIPTION SCHEMATIC DIAGRAM                                                                                                                    | 4080CD<br>4080SD                                                  | 9 14 14                                                           |

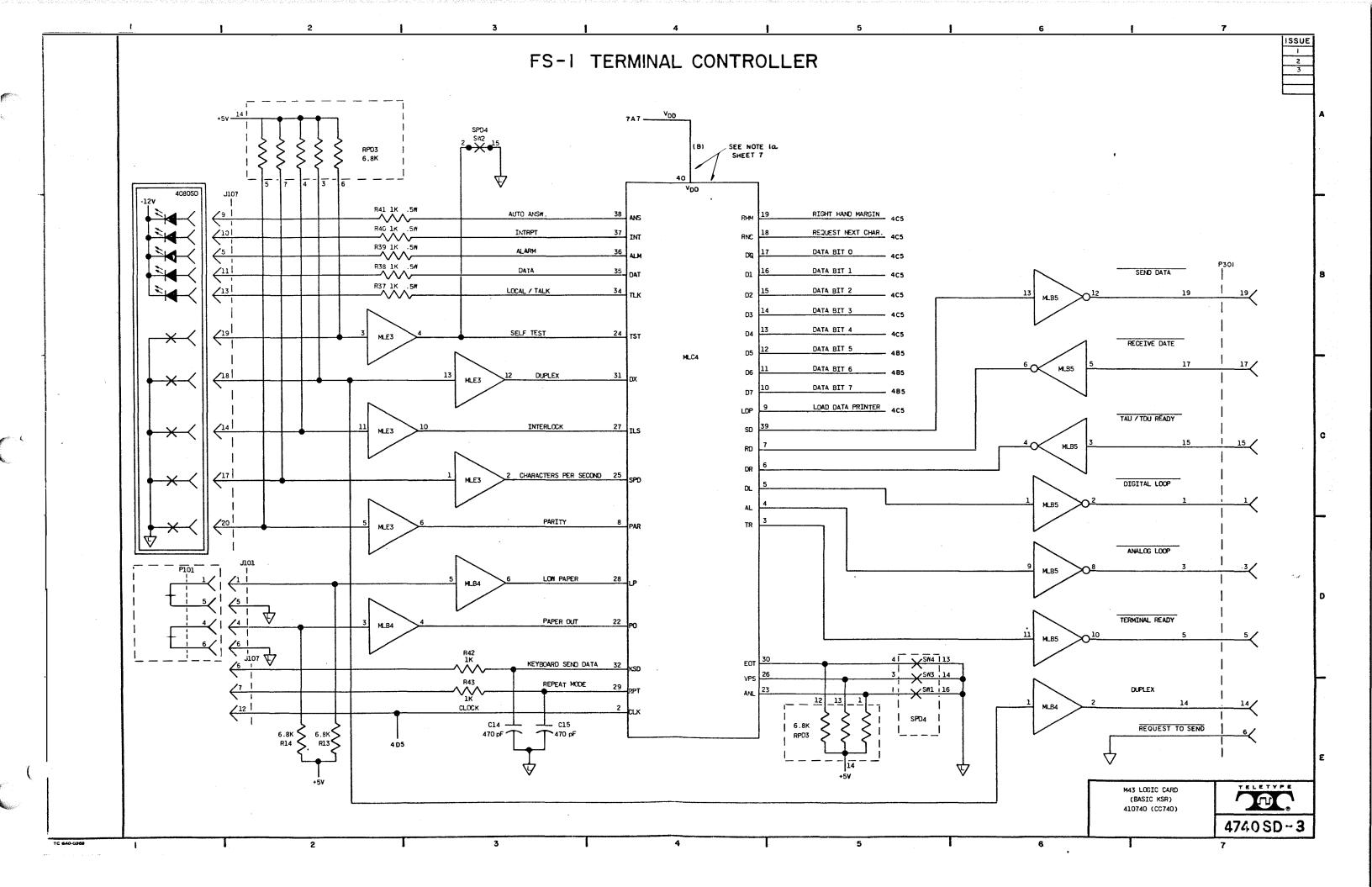

| -  | FS-1 TERMINAL CONTROLLEP                       | 4     | 1 1        | <u>'   '</u>                                      | 2     |                  | 1                | 1                |      | 1 1                                              |             | 1 1  | 1                                                | 1      | 1 1      | 1        | 1 1 | -      | 1            | 1 1                                              | i                | 1 1 | 4        |                                                                                                                                                          |                                                                   |                                                                   |

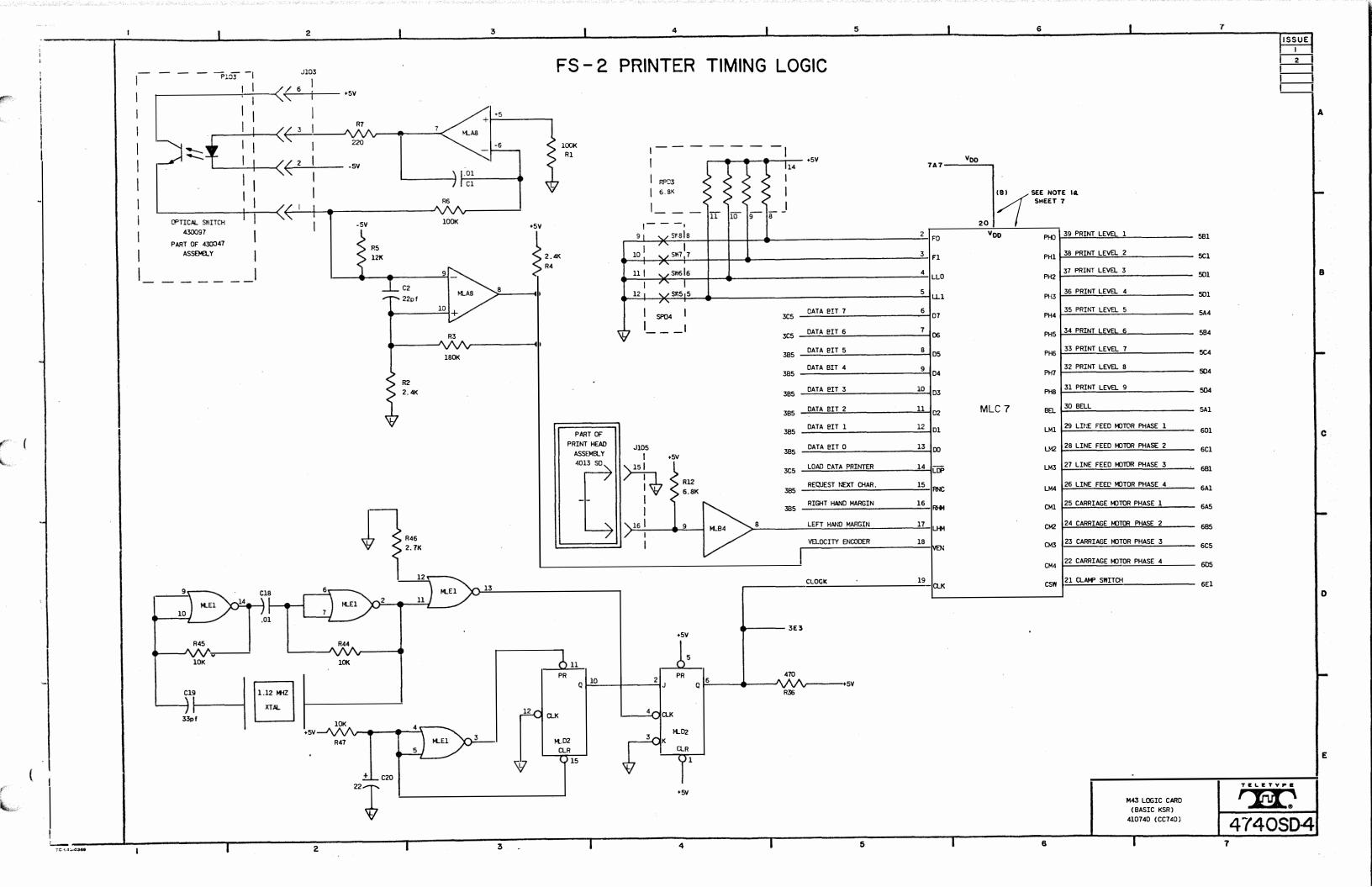

| }- | FS-2 PRINTER TIMING LOGIC                      | 5     | 1 1        | <u>'   '</u>                                      | + ;   | 1 1              | 1                |                  |      | 1                                                |             |      | -                                                | -      | 1 1      | +        | 1 1 | 1      | 1            | 1 1                                              | +                | 1 1 | 5        |                                                                                                                                                          |                                                                   |                                                                   |

|    | FS-3 PEINT HEAD AND BELL DRIVERS               |       | 1-11       |                                                   | + : ! | 1 1              | 1                | <del>- }</del> - |      | <u> </u>                                         |             | 1 1  |                                                  | 1      | 1 1      | <u> </u> | 1 1 | Ť      | 1            | <u>, ,</u>                                       | i                | 1 1 | 6        |                                                                                                                                                          |                                                                   | 1                                                                 |

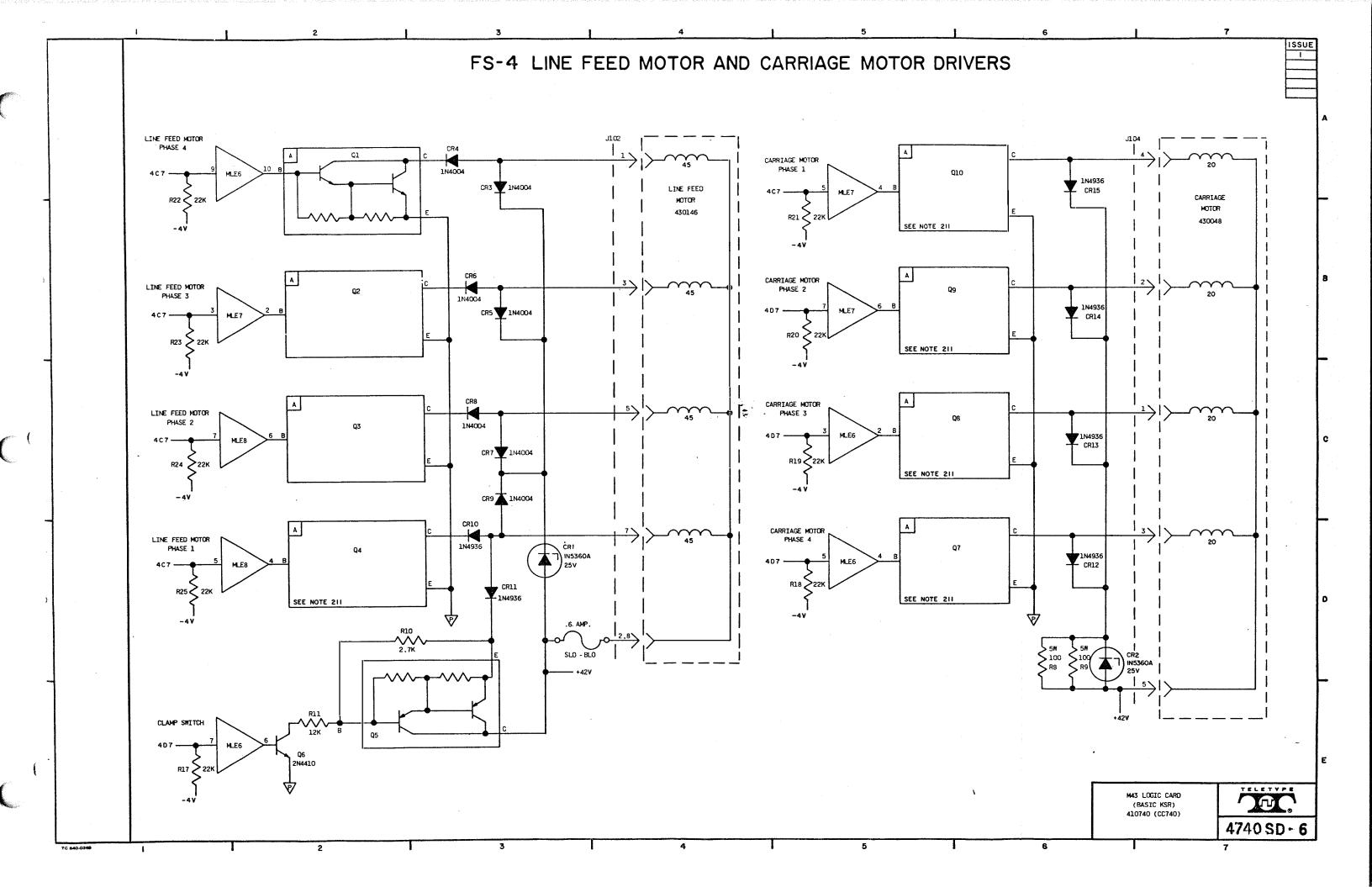

| -  | FS-4 CARRIAGE MOTOR AND LINEFEED MOTOR DRIVERS | 6     | 1 1        | 2 3                                               | + +   | 4 4              | + +              |                  | +    | 1 1                                              |             | 1 1  | <del>                                     </del> | 1      | 1 1      | +        | 1 1 | 1      | 1            | 1 1                                              | <del>-  </del> - | 1 1 | 7        |                                                                                                                                                          |                                                                   | -                                                                 |

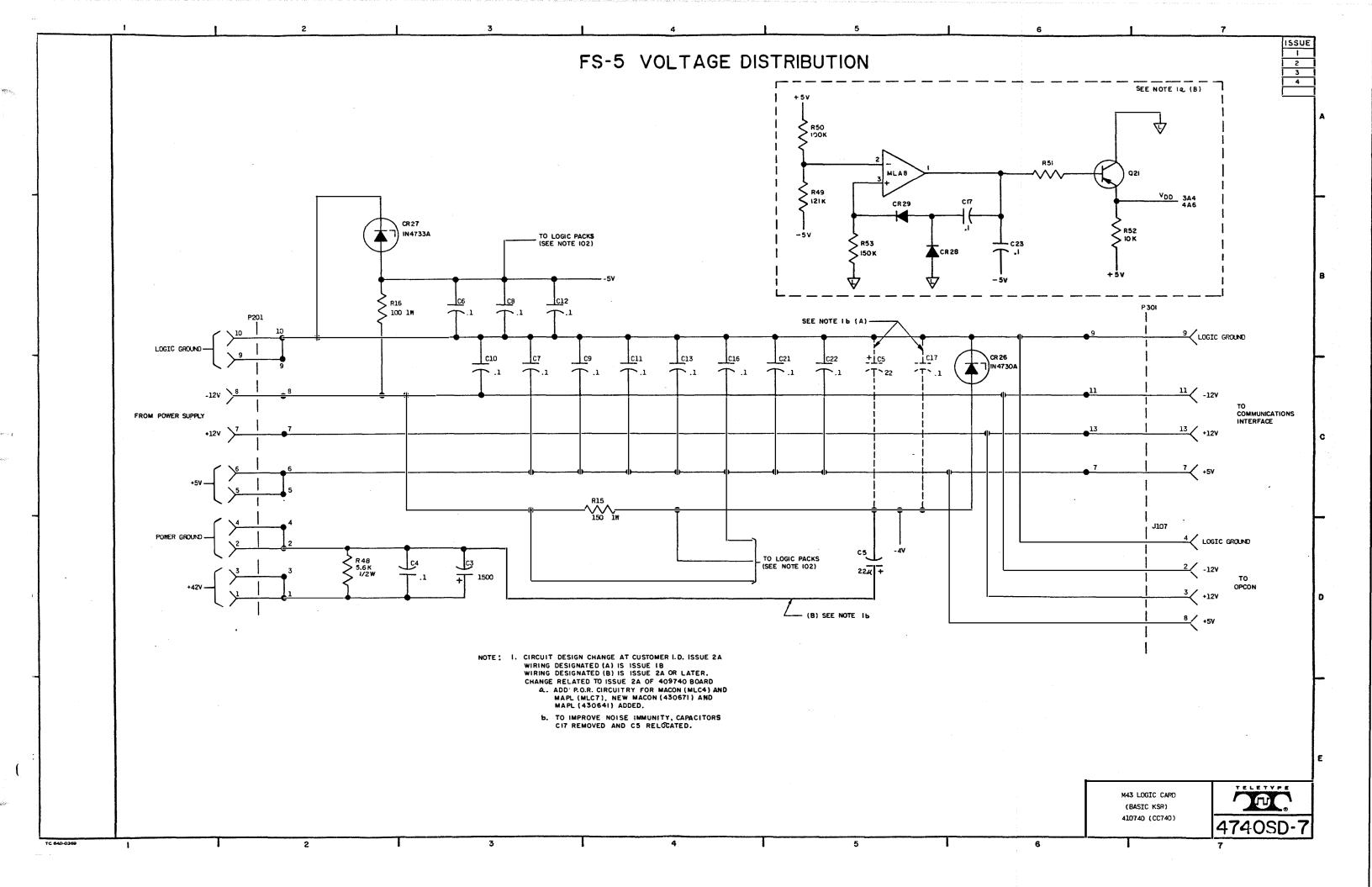

| -  | FS-5 VOLTAGE DISTRIBUTION                      |       | $+ \div +$ | 2 3                                               |       |                  | -  -             |                  | +    |                                                  |             | +    | -                                                |        | ┼┼┼      | +-       | +-+ |        |              | -                                                |                  | +-+ |          |                                                                                                                                                          |                                                                   |                                                                   |

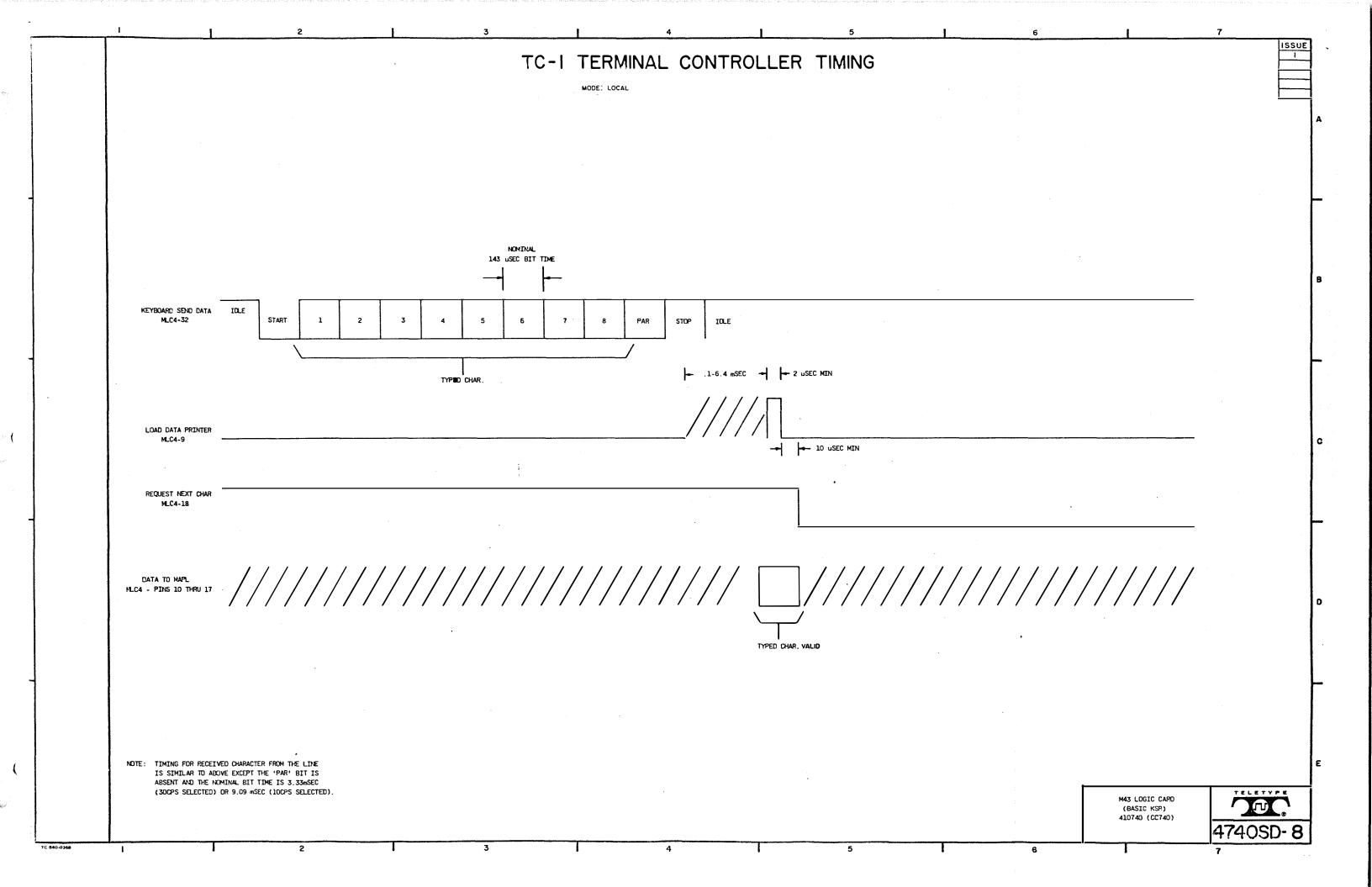

| -  | TC-1 TERMINAL CONTROLLER TIMING                | 8     | $+ \div +$ | <del>'</del>                                      |       | $\dot{-}\dot{-}$ | - <del>  -</del> |                  | +    |                                                  |             | +    |                                                  |        | +-+-     | +        | +   |        | +            | -                                                |                  | +-1 | - 8<br>9 |                                                                                                                                                          | 1 1                                                               |                                                                   |

| -  | TC-2 PRINT CHARACTER TIMING                    | 9     | +:+        | <del>-   -  </del>                                | -     |                  | <del> </del>     |                  | +    | <del>                                     </del> | <del></del> | +-   | <del></del>                                      |        | ┼┼-      | +        | +   | _      | +-           | ++                                               |                  | +-  |          |                                                                                                                                                          |                                                                   |                                                                   |

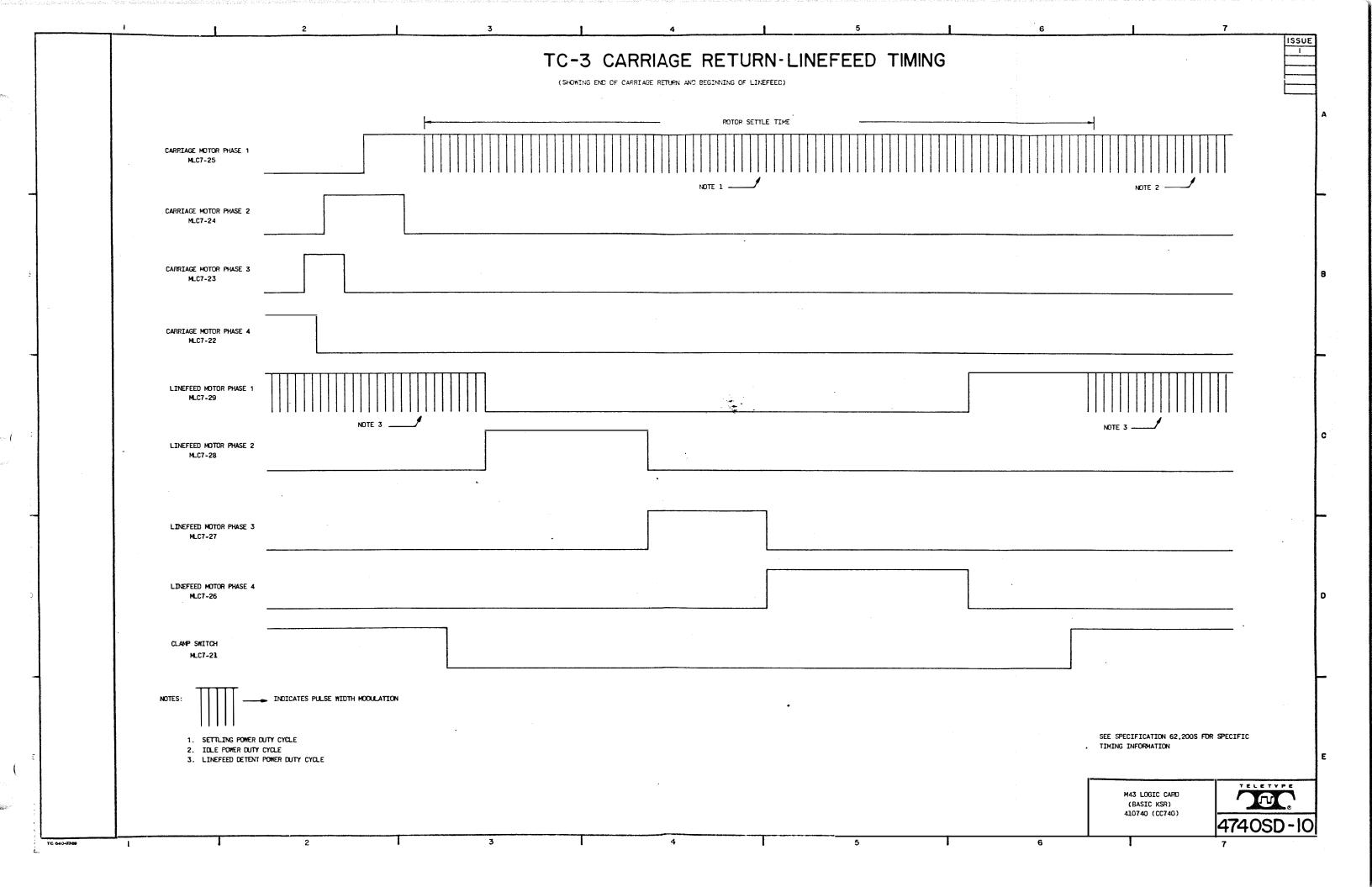

| -  | TC-3 CARRIAGE RETURN - LINEFEED TIMING         | 10    | ++         | <del>'   '</del>                                  | -     |                  |                  |                  |      | $\vdash$                                         |             |      |                                                  |        | -        |          | +   |        | +-           | <del>                                     </del> |                  | +-+ | 10       |                                                                                                                                                          |                                                                   |                                                                   |

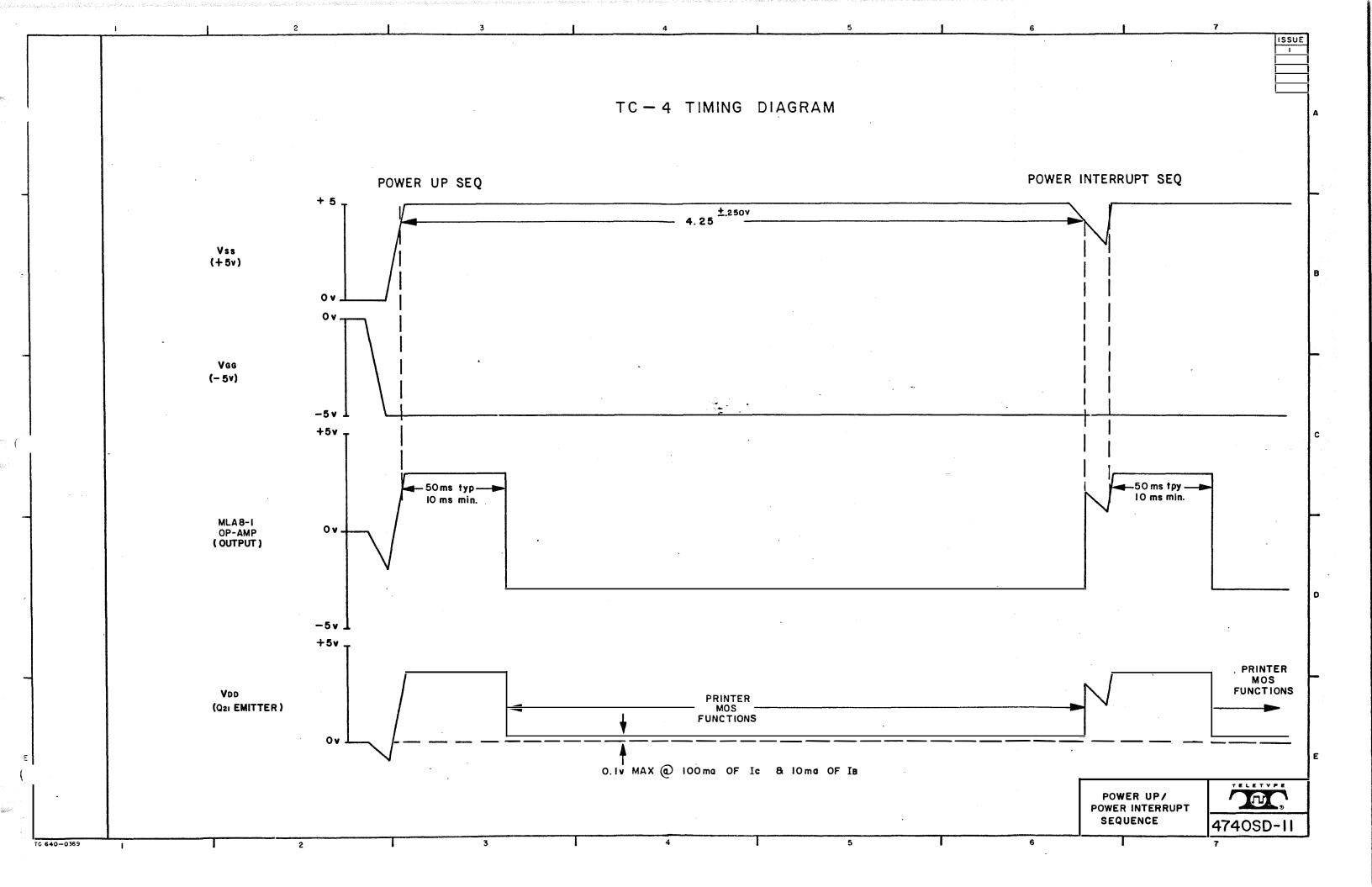

| 1  | TC-4 TIMING DIAGRAM                            | 11    | 1-1        | -   -                                             | -     | 1 1              | 1                | <u> </u>         | }    | <u> </u>                                         |             | 1 1  | <u>                                     </u>     | · l    | <u> </u> | j<br>i   | 1 1 | -      | <del> </del> | <u>]                                    </u>     | 1                | 1 1 | 11       |                                                                                                                                                          | 1.                                                                | 1.                                                                |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          |                                                                                                                                                          |                                                                   |                                                                   |

|    |                                                |       |            |                                                   |       | -                |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          | SHEET INDEX N  I. WHEN CHANGES ARE MADE IN THOSE SHEETS AFFECTED WIL  2. THIS SHEET INDEX WILL BE UPDATED EACH TIME ANY SH DRAWING IS REISSUED OR A      | THIS DRAWING ONLY<br>L BE REISSUED.<br>REISSUED AND<br>EET OF THE |                                                                   |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          | ADDED.  3. THE LAST COMPLETED COLULATEST ISSUE NUMBER OF 1  4. SHEETS THAT ARE NOT CHAITHEIR EXISTING ISSUE NO.  5. ISSUE DATES WILL BE SHOW INDEX ONLY. | IN INDICATES THE<br>HE SHEET INDEX.<br>GED WILL RETAIN            |                                                                   |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          | •                                                                                                                                                        |                                                                   |                                                                   |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          |                                                                                                                                                          |                                                                   |                                                                   |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          |                                                                                                                                                          |                                                                   | M43 LOGIC CAF<br>(BASIC KSR)<br>410740 (CC740                     |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          |                                                                                                                                                          |                                                                   | APPROVALS PROJ. PROJ. DIR. J                                      |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          | •                                                                                                                                                        | <u>-</u> - 1                                                      | ENGR. YCK DEGNR. DRN. DATE R B D FILE 1-30.171. S-NUMBER TELETYPI |

|    |                                                |       |            |                                                   |       |                  |                  |                  |      |                                                  |             |      |                                                  |        |          |          |     |        |              |                                                  |                  |     |          |                                                                                                                                                          |                                                                   | <b>7</b> ₱€,                                                      |

## ISSUE TC-2 PRINT CHARACTER TIMING MODE TWO CHARACTER BURST (AT BELL COLUMN) REQUEST NEXT CHARACTER ML.C7-15 ROTOR SETTLE TIME CARRIAGE MOTOR PHASE 1 MLC7-25 CARRIAGE MOTOR PHASE 2 MLC7-24 NOTE 1 -CARRIAGE MOTOR PHASE 3 MLC7-23 CARRIAGE MOTOR PHASE 4 MLC7-22 PRINT LEVELS 1 THRU 9 MLC7 PINS 39 THRU 31 NOTE 4 BELL MLC7-30 → INDICATES PULSE WIDTH MODULATION VARIABLE DUTY CYCLE SETTLING POWER DUTY CYCLE 3. IDLE POWER DUTY CYCLE 4. PRESENCE OF PULSE ON A GIVEN LEVEL DEPENDS ON CHARACTER PRINTED. TELETYPE M43 LOGIC CARD (BASIC KSR) 410740 (CC 740) 4740SD-9

Sheet 1

### CIRCUIT DESCRIPTION FOR 430700 POWER SUPPLY

| F            | REVISIO | NS        | 1          |                    |              |              |          |          |                                              | s         | HE               | ĒΤ         | N        | UM           | 185 | ล        |            |             |                |         |          |              |   |

|--------------|---------|-----------|------------|--------------------|--------------|--------------|----------|----------|----------------------------------------------|-----------|------------------|------------|----------|--------------|-----|----------|------------|-------------|----------------|---------|----------|--------------|---|

| SSUE         |         | AUTH. NO. |            | 1                  | 2            | 3            | 4        | 5        | 6                                            | 7         | 8                | ,          |          |              |     | -        | 14         |             |                |         | T        | T            | T |

| 1            | 7/1/76  | 24599R    | j          | 1                  | 1            | 1            | 1        | 1        | 1                                            | 1         | 1                | 1          | 1        | 1            | 1   | 1        | 1          |             |                |         |          |              | - |

|              |         |           |            |                    |              |              |          |          |                                              |           |                  |            |          |              |     |          |            |             |                |         |          |              | 7 |

|              |         |           |            |                    |              |              |          |          |                                              |           |                  |            |          |              |     |          |            |             |                |         |          |              | 7 |

|              |         |           | 1          |                    |              |              |          |          |                                              |           |                  |            |          |              |     |          |            |             |                |         |          |              | , |

|              |         |           | 1          |                    |              |              |          |          |                                              |           |                  | Ĺ          |          |              |     |          |            |             |                |         |          |              | _ |

|              |         |           | į.         | <u></u>            |              |              | <u> </u> | <u> </u> | '                                            |           |                  | Ĺ.'        |          |              |     |          |            |             |                |         |          |              | _ |

|              |         |           | 1          |                    | 1            |              |          |          | <u> </u>                                     |           |                  | <u> </u>   | '        |              |     |          |            |             |                |         |          | _            | _ |

|              |         |           | 1          |                    |              |              |          |          | <u>                                     </u> |           |                  | <u></u>    |          |              |     |          |            |             |                |         | <u> </u> |              | _ |

|              |         |           | 1          |                    | '            | 1            |          | <u> </u> | <u> </u>                                     |           |                  | <u></u>    | <u>'</u> |              |     |          | '          |             |                | _       | <u> </u> |              | _ |

|              |         |           | 1          |                    | '            | 1            |          | <u> </u> | <u> </u>                                     |           |                  | <u></u>    | <u>'</u> | -            |     |          | <u> </u>   |             |                |         | <u> </u> |              | _ |

| 1            |         |           | 1          |                    | '            |              |          | $\perp$  | <u> </u>                                     | $\perp$   |                  | <u>—</u> ′ |          |              |     | <u></u>  | <u> </u>   |             | _              | $\perp$ |          |              | _ |

|              |         |           | 1          | <u> </u>           |              | -            |          | !        |                                              |           |                  | <u></u> '  | -        |              | -   | -        | <u> </u> ' |             |                | -       | '        |              | _ |

|              |         |           | 1          |                    |              | 1            |          | $\sqcup$ | <u> </u>                                     | $\coprod$ |                  | <u>—</u> ' | <u></u>  |              |     | <u> </u> |            | _           | _              |         | '        | _            | _ |

| -            |         | -         | æ          | -                  | '            | -            | -        | -        | -                                            | -         |                  |            |          | <del> </del> | ļ - |          | <u> </u>   | <br>        |                | -       |          | <del> </del> | - |

|              |         |           | NUMBER     | -                  | -            | -            | -        | -        | $\vdash$                                     | -         |                  |            | -        | +-           |     | -        | -          |             |                | -       |          | -            |   |

|              |         |           | S          | -                  | <del> </del> |              |          | -        | H                                            |           |                  |            | -        |              | -   |          |            | -           | '              | -       |          | -            | - |

|              |         |           | <b>⊣</b> ` |                    | -            | -            |          | -        | H                                            | -         |                  |            | -        | -            | -   | <u>—</u> |            | <del></del> | +              | -       |          |              |   |

| -            |         |           | SSUE       | -                  | -            |              | -        | -        | H                                            |           |                  | -          |          | -            | -   | -        |            |             | -              |         | -        | -            |   |

|              |         |           | S          |                    | -            | -            | -        | -        |                                              |           | -                |            |          | -            | -   | -        | -          | <del></del> | 1.             | -       | -        | -            |   |

|              |         | 1         | 1          |                    | -            |              | -        | -        |                                              |           | -                |            |          | -            | -   |          |            |             | -              |         |          |              |   |

|              |         |           | SHEET      | -                  |              | -            |          |          |                                              |           |                  | -          |          |              |     | -        | 1          |             | -              |         |          | <del> </del> | - |

|              |         |           | 10,        |                    |              | <del> </del> | -        |          |                                              |           |                  | 1          |          |              | -   |          |            |             |                |         |          |              | · |

|              |         |           | 1          |                    |              |              |          | j        | ı i                                          |           |                  | -          |          |              |     |          |            |             |                |         |          | ĺ            | ĺ |

|              |         |           |            |                    | ,            | ĺ            |          | j        |                                              |           | <del>- ;</del>   |            | İ        |              |     | -        |            | i           |                |         |          |              | ! |

|              |         |           |            |                    | ,            |              |          | j        |                                              |           |                  |            | İ        |              |     |          |            | i           |                |         |          |              | , |

|              |         |           |            |                    |              |              |          | - 1      |                                              |           |                  |            |          |              |     |          |            |             |                |         |          |              | į |

|              |         |           |            |                    |              |              |          |          |                                              |           |                  |            |          |              |     |          |            |             |                |         |          |              | į |

|              |         |           | ,          |                    |              |              |          |          |                                              |           |                  |            |          |              |     |          |            |             |                |         |          |              | ĺ |

|              |         |           |            |                    |              |              |          |          |                                              |           |                  |            |          |              |     |          |            |             |                |         |          |              | ĺ |

|              | APPROV  |           |            | NG.                | FP           | K            |          | DSGI     | NR.                                          |           | NUM              |            | ORN.     |              |     |          |            |             | 1 3 1<br>1 5 1 | المؤون  |          | -            | A |

| PROU<br>SUPV | v. DIR. |           | ·          | are<br>a D<br>L-30 | FIL.         | E N          | 0.       |          | <del></del>                                  |           | אטא<br>47<br>אטא | 7005       | SD       |              |     |          | +          |             |                | 000     |          | <b>②</b>     |   |

Teletype Corporation

Circuit Description

4700CD Issue 1 Sheet 2

### CIRCUIT DESCRIPTION FOR 430700 POWER SUPPLY

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                   | Sheet                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| SECTION I - GENERAL TECHNICAL DATA                                                                                                                                                                                                                                                  | 3                                       |

| 1. PUR POSE                                                                                                                                                                                                                                                                         | 3                                       |

| 2. OPERATION                                                                                                                                                                                                                                                                        | 3                                       |

| 3. SUPPORTING INFORMATION                                                                                                                                                                                                                                                           | 4                                       |

| SECTION II - DETAILED DESCRIPTION AND THEORY OF OPERATION                                                                                                                                                                                                                           | 4                                       |

| 1. GENERAL                                                                                                                                                                                                                                                                          | 4                                       |

| <ul><li>1.1 Operating Modes</li><li>1.2 Features</li></ul>                                                                                                                                                                                                                          | <b>4</b><br>5                           |

| 2. POWER-UP MODE                                                                                                                                                                                                                                                                    | 5                                       |

| 2.1 AC Line Input 2.2 AC Line Rectifier 2.3 Blocking Oscillator Operation 2.4 Snubbing Circuit                                                                                                                                                                                      | 5<br>6<br>6<br>7                        |

| 3. OSCILLATOR DRIVEN MODE                                                                                                                                                                                                                                                           | 7                                       |

| 3.1 20 KHz Square Wave Oscillator 3.2 Generator 3.3 Pulse Width Modulator 3.4 Voltage Reference and Error Amplifier 3.5 Primary Power Conversion 3.6 Feedback Regulation 3.7 Optical Isolator 3.8 Primary Circuit Overcurrent Protection 3.9 Primary Circuit Overvoltage Protection | 7<br>7<br>8<br>8<br>9<br>10<br>10<br>11 |

| 4. LOGIC VOLTAGES                                                                                                                                                                                                                                                                   | 12                                      |

| 4.1 +5V Supply<br>4.2 +12V Supply<br>4.3 -12V Supply                                                                                                                                                                                                                                | 12<br>12<br>12                          |

| 5. OUTPUT VOLTAGE INDICATOR                                                                                                                                                                                                                                                         | 12                                      |

| 6. FAULT PROTECTION ON SECONDARY                                                                                                                                                                                                                                                    | 13                                      |

| 6.1 Short Circuit Protection 6.2 Overvoltage Protection                                                                                                                                                                                                                             | 13<br>13                                |

#### SECTION I - GENERAL TECHNICAL DATA

#### PURPOSE

1.1 The 430700 Power Supply is designed to provide the DC power required to operate the basic Model 43 KSR Set consisting of the Model 43 Printer, OPCON, Controller, and Terminal Data Unit (TDU) or Terminal Auxiliary Unit (TAU). Line input power may be 115 VAC  $\pm$  10%, 58/62 hertz or 165 VDC  $\pm$  10%. Four regulated DC output voltages are produced;  $\pm$ 5V,  $\pm$ 12V  $\pm$ 12V,  $\pm$ 42V.

1.2 The input and output ratings are as follows:

Input:  $115VAC_{,\pm}10\%$ , 58/62 Hz - 0.9 amp

Output: +5 VDC + 8% - 0.75A

$+12 \text{ VDC} \pm 7\% - 0.4A$ -12 VDC  $\pm 7\% - 0.4A$

+42 VDC + 8% - 1.0A (Average)

1.3 All circuitry for the 430700 Power Supply is contained on the 410700 Power Supply Card. This card and associated heat sinks, brackets, and covers are assembled to form the 430700 Power Supply unit which is mounted in the cabinet rear frame. Line power is applied to the unit through a cable having a three terminal connector. A line fuse is provided in the cabinet rear frame adjacent to the ON/OFF switch. The output is available through a 10 pin connector located at the top edge of the circuit card in the supply.

#### 2. OPERATION

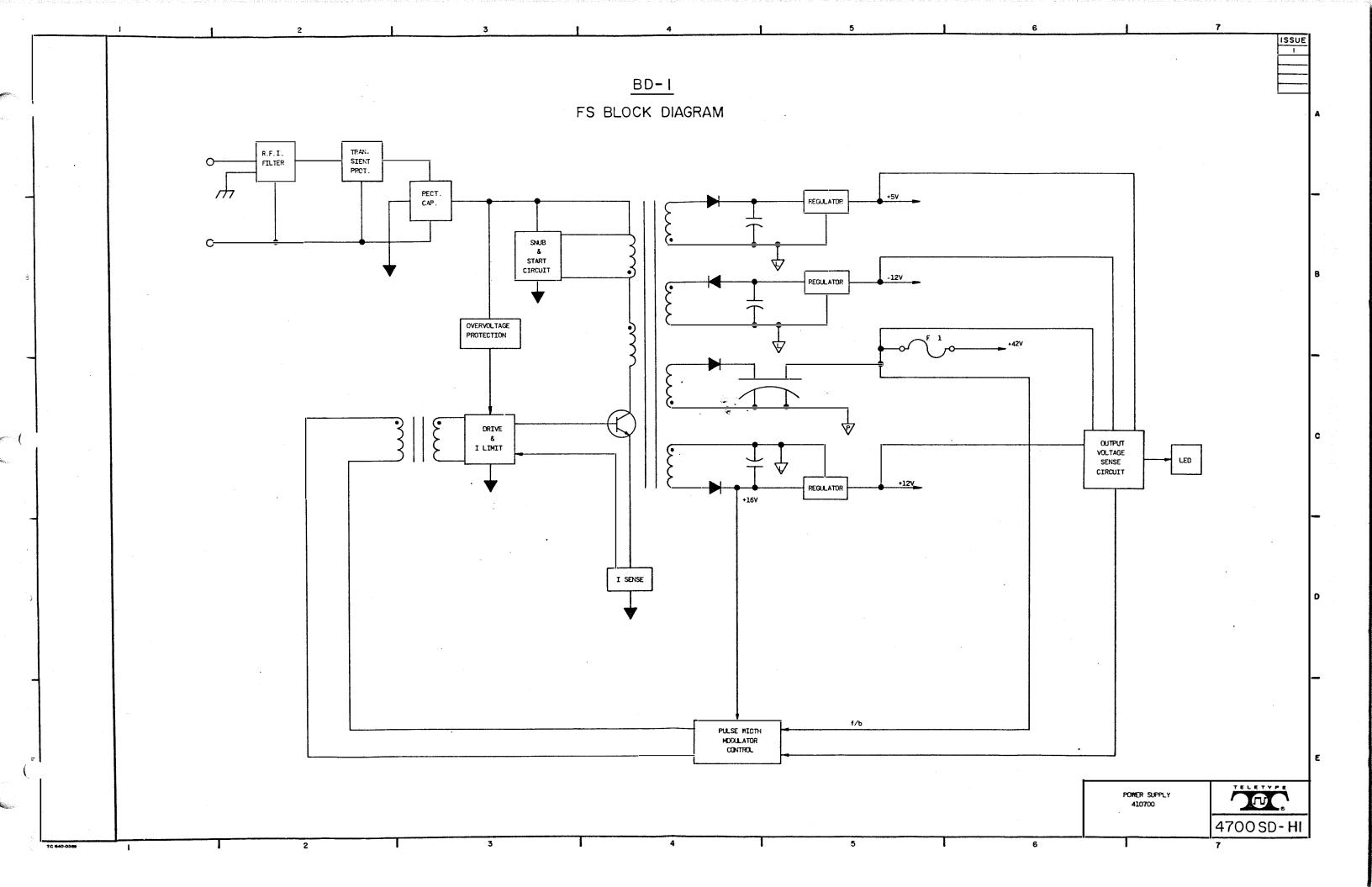

- 2.1 The 430700 Power Supply is of the "Off-the-Line" Switching Regulator type utilizing a "Ringing Choke" design to accomplish power conversion at a nominal frequency of 20 KHz. This design provides a relatively high power conversion efficiency, and minimizes the size and weight of the supply.

- 2.2 The AC line voltage is directly converted to DC by a bridge rectifier connected directly to the AC input and filtered by a capacitor on the output side of the bridge rectifier. The primary of a power transformer is connected to the DC source in series with a primary switching transistor. In operation, the transistor is driven into conduction for a controlled period of each cycle during which the current in the primary increases. During the remainder of the cycle, the transistor is non-conducting, but the energy stored in the primary inductance is transferred to four secondary windings. The secondaries each contain a semiconductor diode which provides half wave rectification.

- 2.3 The +5V, +12V and -12V outputs are derived from three separate windings which drive integrated circuit voltage regulators. These regulators are of the linear type.

- 2.4 The +42V output is derived from the fourth secondary winding. This output is sensed by a feedback circuit which controls the conduction period of the primary switching transistor so that the output is regulated to the correct voltage in response to line and load variations. A more detailed description of operation is contained in Section II.

- 2.5 The Protective Ground is not connected to the Primary Circuit ground. Care must be exercised during trouble shooting to prevent direct connection of these grounds because this will effectively by-pass one of the bridge rectifier diodes and cause full line voltage to be directly applied to another diode in the forward direction. This rectifier and other line components will fail under this condition.

- 2.6 The secondary voltage returns are tied together and directly connected to the Protective Ground. However, isolation is maintained between the AC line and the secondary circuits.

#### 3. SUPPORTING INFORMATION

4700SD - Schematic Diagram 62,097S - Specification

#### SECTION II - DETAILED DESCRIPTION AND THEORY OF OPERATION

#### 1. GENERAL

#### 1.1 Operating Modes

- 1.1.1 During normal operation, the 430700 Power Supply functions as a fixed frequency, pulse width modulated switching regulator. However, whenever power is initially applied, the oscillator and control circuitry which are on the secondary side of the main power transformer, Tl, are not operational. An auxiliary mode of operation is provided which is operational only during start-up while the oscillator and control circuitry are non-operating. In this auxiliary mode, the primary switching transistor is driven by an extra winding on transformer Tl which is connected such that positive feedback is provided to its base. This results in a blocking oscillator like mode of operation during start-up.

- 1.1.2 Operation of the Power Supply in the power-up mode results in energy transfer to the secondary windings so that the oscillator and control circuitry, which are powered from the unregulated voltage which drives the +12V Regulator, will commence operation. With a low secondary voltage, the control circuitry provides a maximum pulse width which is constrained to be slightly less than 50% of a cycle. Whenever the oscillator drive has gained sufficient amplitude to reliably drive the primary switching transistor, the blocking oscillator action is automatically terminated and operation continues under oscillator driven control.

#### 1.2 Features

- 1.2.1 An RFI filter is included in the AC line input to reduce conducted interference resulting from the use of a switching regulator "Off-the-Line".

- 1.2.2 In-rush currents on start-up are controlled by the use of a series line resistance and by a current limited drive on start-up.

- 1.2.3 AC line transient protection has also been provided which both tends to limit peak voltages as well as suppress the transfer of the transient to the secondary circuits.

- 1.2.4 An Output voltage detector circuit is included which will light an LED indicator only whenever all four secondary output voltages are present, although not necessarily within tolerance. This indicator may be viewed for maintenance purposes without removal of the unit.

- 1.2.5 The +5V, +12V, -12V logic voltages are automatically protected against accidental load shorts and recover upon removal of the short. The +42V is also protected against load shorts by means of a fuse in the output.

- 1.2.6 All outputs are protected against sustained overvoltages. Detecting circuitry monitors each output and in the event of a fault, the oscillator drive is immediately removed so that the secondary circuits are no longer powered.

#### 2. POWER UP MODE

- 2.1 AC Line Input (FS-1)

- 2.1.1 Nominal input voltage (115 VAC) is applied to connector J202. The hot side of the line is applied to terminal #1. Protective earth ground is applied to terminal #2, and line neutral to terminal #3 of J202.

- 2.1.2 An R.F.I. filter, FL1, reduces conducted interference entering and leaving the power supply.

- 2.1.3 Thermistor RTl is in the hot side of the line to limit initial inrush current into capacitor Cl. Initial resistance of RTl is 2.5 ohms which after the supply is operational reduces to approximately 1.0 ohm due to self heating.

- 2.1.4 The transient protector RV1 is a voltage clamping device to limit the potential applied to primary circuits of the power supply. RV1 avalanches at approximately 150 VAC (RMS), limiting the voltage applied to other devices.

#### 2.2 AC Line Rectifier

- 2.2.1 AC to DC rectification occurs through the full wave bridge consisting of the four diodes CR1, CR2, CR3 and CR4. Capacitor C1 filters the DC.

- 2.2.2 The anodes of CR3 and CR4 and the negative end of Cl are connected to a common buss for all primary circuits. This buss is not to be confused or connected with any ground buss on the secondary circuits unless the power supply is floated through an isolation transformer. Grounding of the primary buss might cause distruction of diode CR3, as well as thermistor RT1.

- 2.3 Blocking Oscillator Operation (FS-2)

- 2.3.1 Upon initial application of DC voltage to R3, current flows to charge C2. The time constant of R3 and C2 delays the start-up until capacitor C1 is fully charged.

- 2.3.2 The voltage across C2 biases the base of Q1 into the active region by applying DC potential through R8, terminal (J, H) of P2 and diode CR11. This causes current to flow into the base of Q1 tending to turn it on. As Q1 turns on, terminal L of P1 is forced toward primary buss common. Since Q1 turns on, terminal L of P1 is forced toward primary buss common. Since coil P1 is tightly coupled to P2 an equivalent potential is applied across P2 according to the dot notation shown. R15 is a base bias resistor for Q1.

- 2.3.3 A portion of P2 is tapped at J to act as a source to further drive the base of Q1 toward saturation. Regenerative action occurs because of positive feedback driving Q1 into saturation.

- 2.3.4 Base drive into Q1 is limited by resistor R8. The Q1 collector current ramps up due to the magnitizing inductance of T1. This current is limited by the gain hFE of Q1. For constant current base drive, Q1 remains in saturation until IC exceeds hFE times  $I_{\rm R}$ .

- 2.3.5 As Q1 comes out of saturation voltage across J-H is reduced, lowering the base drive to Q1. Regenerative action occurs forcing Q1 off. Q1 remains off until the energy in T1 collapses via dumping energy into the secondaries (S1, S2, S3, S4). The cycle then repeats itself until the pulse width modulator mode takes over.

#### 2.4 Snubing Circuit (FS-2)

- 2.4.1 The snubing network consisting of coil P2 and diodes CR14 and CR12, clamp the collector of transistor Q1 during turn off to twice the DC supply voltage. During turn off terminal L of P1 exceeds the potential at terminal G due to the inductive kick of the transformer T1. The potential across terminals L-G is mirrored on terminals K-H by observing the dot notation polarity.

- 2.4.2 Upon turn off terminal K becomes more positive than +VDC in and is clamped by CR14. Terminal H becomes more negative than the -VDC buss common. This forces a clamping of coil P2 which reflects to coil P1 due to tight coupling. The voltage on the collector of Q1 is limited to that across P2 or twice VIN. Diode CR7 prevents capacitor C2 from being reversed biased.

#### 3. OSCILLATOR DRIVEN MODE

- 3.1 20 KHz Square Wave Oscillator

- 3.1.1 During start-up, the secondaries of T1 receive a limited amount of power which results in an increasing rectified voltage. The oscillator is fabricated from one of the comparators in ML2 which derives its power from the unregulated +16V supply used to power the +12V linear regulator. As this voltage increases to approximately 4 volts, oscillation commences.

- 3.1.2 If the oscillator output (Pin 2) has just switched to ground, the voltage at the non-inverting input (Pin 5) will be determined by the divider of R35 and R28 in parallel with R32. This voltage is 31% of the +16V supply. The voltage on the inverting input (Pin 4) discharges toward ground at a rate determined by R38 and C11. As this voltage drops to 31% of the +16V supply, the comparator output switches to the high state. Now, the voltage on Pin 5 is essentially determined by the divider of R28 in parallel with R35 and R32. This voltage is 62% of the +16V supply. The voltage or Pin 4 charges toward the +16V supply at a rate determined by R30 and R38 in series, and C11. As this voltage now reaches 62% of the +16V supply, the comparator output (Pin 2) switches to the low state.

- 3.1.3 Since the comparator switch points are a fixed ratio of the +16V supply, the frequency will be virtually independent of the actual voltage of the +16V supply. In fact, from approximately +4 to +20 volts, the frequency and duty cycle are essentially constant.

#### 3.2 Ramp Generator (FS-4)